靴带式开关的制作方法

本发明申请是关于靴带式开关,具体地,是关于可降低寄生电容影响的靴带式开关。

背景技术:

1、开关电路常应用于模拟数字转换器与/或数字模拟转换器。为了达到高线性度的信号转换,需使用具有高效能的开关电路。例如,靴带式开关被提出以提供具有稳定的导通阻值以获得较高的线性度。然而,在现有的靴带式开关中,晶体管仍会受到电压相依的寄生电容的影响,使得靴带式开关无法达到目前应用所要求的线性度要求。

技术实现思路

1、在一些实施方式中,本发明申请的目的之一(但不限于)提供一种可降低电压相依的寄生电容影响的靴带式开关。

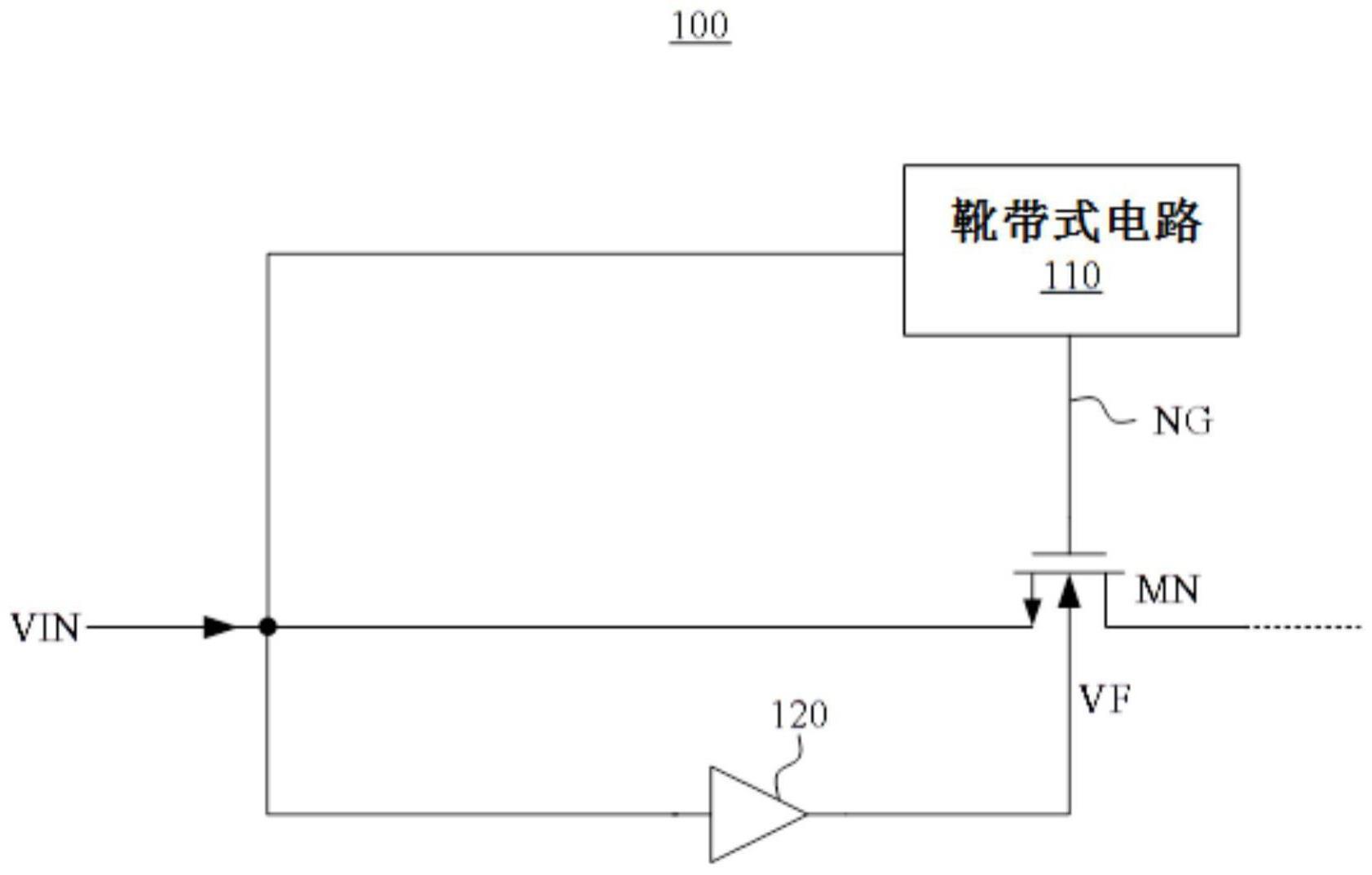

2、在一些实施方式中,靴带式开关包含取样晶体管、靴带式电路以及缓冲器电路。取样晶体管用以根据一控制节点的位准选择性地导通,以自该取样晶体管的第一端传输输入信号到该取样晶体管的第二端,且该取样晶体管的基极用以接收缓冲信号。靴带式电路用以拉升该控制节点的位准,以使该控制节点与该取样晶体管的第一端在该取样晶体管的导通期间内具有一固定电压差。缓冲器电路用以根据该输入信号产生该缓冲信号。

3、在一些实施方式中,靴带式开关可利用基极偏压的方式来降低电压相依的寄生电容的影响,以进一步地提升靴带式开关的线性度。

4、有关本发明申请的特征、操作与技术效果,请结合附图对较佳实施例进行如下详细说明。

技术特征:

1.一种靴带式开关,其特征在于,所述靴带式开关包含:

2.如权利要求1所述的靴带式开关,其特征在于,所述靴带式电路包含多个n型晶体管,且所述多个n型晶体管中的至少一者的基极用以接收所述缓冲信号。

3.如权利要求1所述的靴带式开关,其特征在于,所述多个n型晶体管中的所述至少一者在所述取样晶体管的导通期间内是导通的,并接收所述输入信号。

4.如权利要求1所述的靴带式开关,其特征在于,所述靴带式电路包含多个n型晶体管,且所述多个n型晶体管中的至少一者的基极不直接接收所述输入信号。

5.如权利要求4所述的靴带式开关,其特征在于,所述多个n型晶体管中的所述至少一者在所述取样晶体管的导通期间内是导通的,并接收所述输入信号。

6.如权利要求1所述的靴带式开关,其特征在于,所述靴带式电路包含:

7.如权利要求6所述的靴带式开关,其特征在于,所述第一n型晶体管、所述第三n型晶体管与所述第四n型晶体管中的至少一者的基极用以接收所述缓冲信号。

8.如权利要求6所述的靴带式开关,其特征在于,所述第二n型晶体管在所述取样晶体管的导通期间内是不导通的。

9.如权利要求6所述的靴带式开关,其特征在于,所述靴带式开关更包含:

10.如权利要求1所述的靴带式开关,其特征在于,所述取样晶体管的基极接收所述缓冲信号以降低所述取样晶体管的寄生电容的容值变动,且所述寄生电容为电压相依。

技术总结

靴带式开关包含取样晶体管、靴带式电路以及缓冲器电路。取样晶体管用以根据控制节点的位准选择性地导通,以自该取样晶体管的第一端传输输入信号到该取样晶体管的第二端,且该取样晶体管的基极用以接收缓冲信号。靴带式电路用以拉升该控制节点的位准,以使该控制节点与该取样晶体管的第一端在该取样晶体管的导通期间内具有固定电压差。缓冲器电路用以根据该输入信号产生该缓冲信号。

技术研发人员:雷良焕

受保护的技术使用者:瑞昱半导体股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!