一种高压集成电路及其控制方法

1.本发明涉及半导体技术领域,特别是一种高压集成电路及其控制方法。

背景技术:

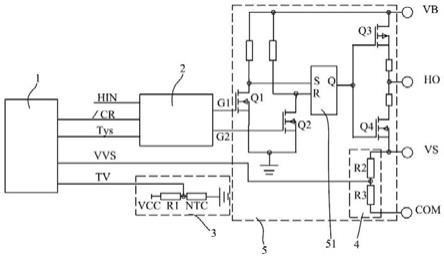

2.高压集成电路,即hvic,是一种把mcu信号转换成驱动igbt管或mos管的信号的集成电路产品。如图1所示,hvic把pmos管、nmos管、三极管、二极管、稳压管、电阻和电容集成在一起,形成斯密特、低压levelshift、高压levelshift、脉冲发生电路、延时电路、滤波电路、过电流保护电路和过热保护电路、欠压保护电路以及自举电路等电路。

3.现有的hvic的高侧驱动单元5包括n沟道dmos管q1、n沟道dmos管q2和rs触发器51,单脉冲gen根据上位机输入的hin信号产生脉冲,在如图1和2所示的上位机输入的hin信号的上升沿产生脉冲g1用于驱动n沟道dmos管q1,并于rs触发器51的触发端s输入对应的逻辑,hin信号的下降沿产生脉冲g2用于驱动n沟道dmos管q2并于rs触发器51的触发端s输入对应的逻辑,rs触发器51根据相应的逻辑于其输出端q输出相应的逻辑信号,通过该逻辑信号控制后面的p沟道dmos管q3和p沟道dmos管q4的通断,从而产生输出vb、输出ho和输出vs。脉冲的宽度一般在几百纳秒,使hin与ho对应。但在hvic驱动负载为大电感电路时,输出vs的电压在某种情况下会被拉低,导致rs触发器51无法记录到单脉冲gen发出的信号,从而导致产生的控制信号不准确。

技术实现要素:

4.针对上述缺陷,本发明的一个目的在于提出一种高压集成电路,解决了现有的高压集成电路的rs触发器产生的控制信号不准确的问题。

5.针对上述缺陷,本发明的另一个目的在于提出一种高压集成电路的控制方法,解决了现有的高压集成电路的rs触发器产生的控制信号不准确的问题。

6.为达此目的,本发明采用以下技术方案:一种高压集成电路,包括mcu处理器、延时脉冲单元、电压检测单元和高侧驱动单元;所述延时脉冲单元包括移位寄存器、第一单脉冲gen、第二单脉冲gen、第一或门和第二或门;所述第一单脉冲gen的输入端与上位机的hin信号输出口电连接,所述第一单脉冲gen的上升沿输出端与所述第一或门的输入端a1电连接,所述第一单脉冲gen的下降沿输出端与所述第二或门的输入端b1电连接;所述移位寄存器的清零管脚cr与所述mcu处理器的清零信号输出端/cr电连接,所述移位寄存器的时钟管脚cpa与所述mcu处理器的pwm输出端tys电连接,上位机的hin信号输出口与所述移位寄存器的串行输入端电连接;所述移位寄存器的输出端q与所述第二单脉冲gen的输入端电连接,所述第二单脉冲gen的上升沿输出端与所述第一或门的输入端b2电连接,所述第二单脉冲gen的下降沿输出端与所述第二或门的输入端a2电连接;所述第一或门的输出端a3与所述高侧驱动单元内的n沟道dmos管q1的栅极电连

接,所述第二或门的输出端b3与所述高侧驱动单元内的n沟道dmos管q2的栅极电连接;所述电压检测单元的检测端与所述高侧驱动单元的输出端vs电连接,所述电压检测单元的信号输送端与所述mcu处理器的电压信号输入端vvs电连接。

7.值得说明的是,所述高压集成电路还包括温度检测单元,所述温度检测单元包括温度传感器ntc和电阻r1,所述温度传感器ntc设置于所述高压集成电路的封装内,所述温度传感器ntc的一端与所述电阻r1的一端电连接,所述温度传感器ntc的一端还与所述mcu处理器的温度输入端tv电连接,所述温度传感器ntc的另一端接地,所述电阻r1的另一端与电源vcc电连接。

8.可选地,所述温度传感器ntc为热敏电阻。

9.具体地,所述移位寄存器为d触发器移位寄存器,所述移位寄存器由多个d触发器依次排列组成,所有d触发器的触发端c1并联后组成所述移位寄存器的时钟管脚cpa,所述移位寄存器的串行输入端为第一个所述d触发器的输入端d1。

10.优选的,所述移位寄存器为jk触发器移位寄存器,所述移位寄存器由多个jk触发器依次排列组成,所有jk触发器的触发端c2并联后组成所述移位寄存器的时钟管脚cpa,所述上位机的hin信号输出口与第一个所述jk触发器的输入端j电连接,所述上位机的hin信号输出口通过非门还与第一个所述jk触发器的输入端k电连接。

11.一种高压集成电路的控制方法,包括以下步骤:a1:所述第一单脉冲gen接收上位机的hin信号输出口的hin信号后产生第一脉冲,其中所述第一单脉冲gen在hin信号的上升沿和下降沿时产生第一脉冲,当在hin信号的上升沿时,所述第一单脉冲gen的上升沿输出端导通,第一脉冲通过所述第一单脉冲gen的上升沿输出端输入到所述第一或门的输入端a1,当在hin信号的下降沿时,所述第一单脉冲gen的下降沿输出端导通,第一脉冲通过所述第一单脉冲gen的下降沿输出端输入到所述第二或门的输入端b1;a2:所述mcu处理器通过所述电压检测单元采集所述高侧驱动单元的输出端vs的电压;当所述高侧驱动单元的输出端vs的电压低于设定值时,所述mcu处理器通过其自身的清零信号输出端/cr触发所述移位寄存器清零后,所述mcu处理器通过其自身的pwm输出端tys输送pwm波到所述移位寄存器的时钟管脚cpa,执行步骤a3;当所述高侧驱动单元的输出端vs的电压低于设定值时,所述mcu处理器不会触发所述移位寄存器的清零管脚cr,所述mcu处理器不会输送pwm波到所述移位寄存器的时钟管脚cpa;a3:所述移位寄存器运行,同步接收上位机的hin信号输出口的hin信号并延时s秒后触发所述第二单脉冲gen产生第二脉冲,其中延时时间s=1/f,f为额定占空比的pwm波的频率,所述第二单脉冲gen在hin信号的上升沿和下降沿时产生第二脉冲,当在hin信号的上升沿时,所述第二单脉冲gen的上升沿输出端导通,第二脉冲通过所述第二单脉冲gen的上升沿输出端输入到所述第一或门的输入端b2,从而在所述第一或门的输入端b2当在hin信号的下降沿时,所述第二单脉冲gen的下降沿输出端导通,第二脉冲通过所述第二单脉冲gen的下降沿输出端输入到所述第二或门的输入端a2;所述第一或门根据其自身的输入端a1的输入信号和输入端b2的输入信号作或运

算,得到结果后通过其自身的输出端a3输入到所述高侧驱动单元内的n沟道dmos管q1的栅极;所述第二或门根据其自身的输入端b1的输入信号和输入端a2的输入信号作或运算,得到结果后通过其自身的输出端b3输入到所述高侧驱动单元内的n沟道dmos管q2的栅极。

12.值得说明的是,在所述步骤a3中,所述mcu处理器根据其自身的温度输入端tv采集到的高压集成电路的封装内的温度来调节所述pwm波的频率f,当温度升高时,所述pwm波的频率f减少,当温度降低时,所述pwm波的频率f增大。

13.可选地,在所述步骤a3中预设定多个温度范围和多个预设频率,所述温度范围与所述预设频率一一对应,所述mcu处理器根据所述温度范围选取对应的预设频率并赋予给所述pwm波的频率f。

14.上述技术方案中的一个技术方案具有如下有益效果:当所述高压集成电路的驱动负载为大电感电路时,所述高侧驱动单元的输出端vs的电压会被拉低,此时所述mcu处理器通过电压检测单元采集到的输出端vs的电压低于设定值时,就会通过所述mcu处理器的清零信号输出端/cr动作使所述移位寄存器清零后,pwm输出端tys触发并控制所述移位寄存器动作,由于所述移位寄存器具有延时的作用,所述移位寄存器在接收到上位机的hin信号输出口的hin信号后会延迟s秒经过第二单脉冲gen产生第二脉冲并发送到第一或门的输入端b2或第二或门的输入端a2;没有经过移位寄存器而直接由第一单脉冲gen产生并发送到第一或门的输入端a1或第二或门的输入端b1的第一脉冲没有延迟,就能与所述第二脉冲在时间上有所间隔,从而形成双脉冲,确保所述高侧驱动单的rs触发器能获取信号,使用双脉冲时,相当于增加了脉冲的存在时间,给足了时间所述高侧驱动单元的n沟道dmos管q1或n沟道dmos管q2导通,从而保证了所述rs触发器能获取信号,从而保证所述rs触发器产生的控制信号准确。

附图说明

15.图1是现有的高压集成电路的电路结构图;图2是现有的高压集成电路中的单脉冲gen的时序波形图;图3是本发明的一个实施例的高压集成电路的电路结构图;图4是本发明的一个实施例的延时脉冲单元的电路结构图;图5是本发明的另一个实施例的高压集成电路的电路结构图;图6是本发明的另一个实施例的延时脉冲单元与高压集成电路的封装内的温度的时序波形图;图7是本发明的一个实施例的脉冲信号g1、脉冲信号g2、第一或门的输入端a1、第一或门的输入端b2、第二或门的输入端b1和第二或门的输入端a2之间的时序波形图;图8是本发明的一个实施例的移位寄存器组成的延迟电路的延时时序波形图;图9是本发明的一个实施例中由d触发器组成的移位寄存器的电路结构图;图10是本发明的一个实施例中由jk触发器组成的移位寄存器的电路结构图;其中:1、mcu处理器;2、延时脉冲单元;21、移位寄存器;22、第一单脉冲gen;23、第二单脉冲gen;24、第一或门;25、第二或门;3、温度检测单元;4、电压检测单元;5、高侧驱动单元;51、rs触发器。

具体实施方式

16.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。

17.下面结合图3至图10,描述本发明实施例的一种高压集成电路,包括mcu处理器1、延时脉冲单元2、电压检测单元4和高侧驱动单元5;所述延时脉冲单元2包括移位寄存器21、第一单脉冲gen22、第二单脉冲gen23、第一或门24和第二或门25;所述移位寄存器21是一种在若干相同时间脉冲下工作的以触发器为基础的器件,数据以并行或串行的方式输入到移位寄存器21中,然后每个时间脉冲依次向左或右移动一个比特,在输出端q进行输出。移位寄存器21不仅能寄存数据,而且能在时钟信号的作用下使其中的数据依次左移或右移,从而实现延时。所述第一单脉冲gen22和第二单脉冲gen23均为现有的单脉冲发生器;所述第一单脉冲gen22的输入端与上位机的hin信号输出口电连接,所述第一单脉冲gen22的上升沿输出端与所述第一或门24的输入端a1电连接,所述第一单脉冲gen22的下降沿输出端与所述第二或门25的输入端b1电连接;所述移位寄存器21的清零管脚cr与所述mcu处理器1的清零信号输出端/cr电连接,所述移位寄存器21的时钟管脚cpa与所述mcu处理器1的pwm输出端tys电连接,上位机的hin信号输出口与所述移位寄存器21的串行输入端电连接;所述移位寄存器21的输出端q与所述第二单脉冲gen23的输入端电连接,所述第二单脉冲gen23的上升沿输出端与所述第一或门24的输入端b2电连接,所述第二单脉冲gen23的下降沿输出端与所述第二或门25的输入端a2电连接;所述第一或门24的输出端a3与所述高侧驱动单元5内的n沟道dmos管q1的栅极电连接,所述第二或门25的输出端b3与所述高侧驱动单元5内的n沟道dmos管q2的栅极电连接;所述电压检测单元4的检测端与所述高侧驱动单元5的输出端vs电连接,所述电压检测单元4的信号输送端与所述mcu处理器1的电压信号输入端vvs电连接。

18.如图3-5所示,当所述高压集成电路的驱动负载为大电感电路时,所述高侧驱动单元5的输出端vs的电压会被拉低,此时所述mcu处理器1通过电压检测单元4采集到的输出端vs的电压低于设定值时,就会通过所述mcu处理器1的清零信号输出端/cr动作使所述移位寄存器21清零后,pwm输出端tys触发并控制所述移位寄存器21动作,由于所述移位寄存器21具有延时的作用,所述移位寄存器21在接收到上位机的hin信号输出口的hin信号后会延迟s秒经过第二单脉冲gen23产生第二脉冲并发送到第一或门24的输入端b2或第二或门25的输入端a2;没有经过移位寄存器21而直接由第一单脉冲gen22产生并发送到第一或门24的输入端a1或第二或门25的输入端b1的第一脉冲没有延迟,就能与所述第二脉冲在时间上有所间隔,从而形成双脉冲,确保所述高侧驱动单元5的rs触发器51能获取信号,使用双脉冲时,相当于增加了脉冲的存在时间,给足了时间所述高侧驱动单元5的n沟道dmos管q1或n沟道dmos管q2导通,从而保证了所述rs触发器51能获取信号,从而保证所述rs触发器51产生的控制信号准确。

19.一些实施例中,所述高压集成电路还包括温度检测单元3,所述温度检测单元3包

括温度传感器ntc和电阻r1,所述温度传感器ntc设置于所述高压集成电路的封装内,所述温度传感器ntc的一端与所述电阻r1的一端电连接,所述温度传感器ntc的一端还与所述mcu处理器1的温度输入端tv电连接,所述温度传感器ntc的另一端接地,所述电阻r1的另一端与电源vcc电连接。

20.如图5和6所示,由于由第一脉冲和第二脉冲组成的双脉冲会在短时间内增加高压集成电路的功耗而使高压集成电路发热,在所述高压集成电路的第一单脉冲gen22和第二单脉冲gen23的附近增加温度检测单元3,所述mcu处理器1根据所述温度检测单元3检测到的温度来调节所述移位寄存器21的延时时间;当温度升高时,移位寄存器21的延时时间增大,第一脉冲和第二脉冲之间的距离增大,当温度降低时,移位寄存器21的延时时间减少,第一脉冲和第二脉冲之间的距离减少,从而避免所述高压集成电路过热而损坏。

21.值得说明的是,所述温度传感器ntc为热敏电阻。当温度升高时,所述温度传感器ntc的阻值减少,当温度降低时,所述温度传感器ntc的阻值增大;所述mcu处理器1的温度输入端tv用于采集所述温度传感器ntc的两端的电压,因此,当温度升高时,所述mcu处理器1的温度输入端tv采集到的电压会降低,当温度降低时,所述mcu处理器1的温度输入端tv采集到的电压会升高。所述电阻r1用于分压,所述电源vcc用于产生电压信号。

22.可选地,所述移位寄存器21为d触发器移位寄存器,所述移位寄存器21由多个d触发器依次排列组成,所有d触发器的触发端c1并联后组成所述移位寄存器21的时钟管脚cpa,所述移位寄存器21的串行输入端为第一个所述d触发器的输入端d1。如图9所示为4个d触发器依次排列组成的移位寄存器21,四个d触发器依次为d触发器ff0、d触发器ff1、d触发器ff2和d触发器ff3,每个d触发器的输出端q1电连接到下一个d触发器的输入端d1,因此,第一个d触发器的输入端就是移位寄存器21的串行输入端,最后一个d触发器的输出端q1就是移位寄存器21的输出端q。从输入到触发端c1的信号的上升沿开始到输出端q1稳定地建立起新状态有一段延迟时间,所以信号同时加到四个d触发器的触发端c1上时,每个d触发器接收的都是上一个d触发器中原来的数据,每经过一个d触发器,移位寄存器21中的数据依次右移一位。

23.具体地,所述移位寄存器21为jk触发器移位寄存器,所述移位寄存器21由多个jk触发器依次排列组成,所有jk触发器的触发端c2并联后组成所述移位寄存器21的时钟管脚cpa,所述上位机的hin信号输出口与第一个所述jk触发器的输入端j电连接,所述上位机的hin信号输出口通过非门还与第一个所述jk触发器的输入端k电连接。具体地,所述上位机的hin信号输出口输出的hin信号直接从第一个所述jk触发器的输入端j输入,与此同时,所述上位机的hin信号输出口输出的hin信号经过非门后再从第一个所述jk触发器的输入端k输入。当所述上位机的hin信号输出口输出的hin信号的逻辑为1时,从第一个所述jk触发器的输入端j输入的逻辑为1,从第一个所述jk触发器的输入端k输入的逻辑为0,由现有的jk触发器逻辑运算可知,第一个所述jk触发器的输出端的逻辑为1,如此类推,最后一个jk触发器的输出端的逻辑也为1,hin信号经过移位寄存器21后不会改变逻辑。如图10所示,一个实施例中,4个jk触发器依次排列组成的移位寄存器21,四个jk触发器依次为jk触发器j0、jk触发器j1、jk触发器j2和jk触发器j3,每个jk触发器的输出端q2电连接到下一个jk触发器的输入端j,每个jk触发器的输出端/q2电连接到下一个jk触发器的输入端k,其中q2与/q2输出的信号相反,即当q2输出的信号的逻辑为1的时候,/q2输出的信号的逻辑为0;因此,

最后一个jk触发器的输出端q2就是移位寄存器21的输出端q。从输入到输入端j和输入端k的信号开始到输出端稳定地建立起新状态有一段延迟时间,所以信号同时加到四个jk触发器的输入端j和输入端k上时,每个jk触发器接收的都是上一个jk触发器中原来的数据,每经过一个jk触发器,移位寄存器21中的数据依次右移一位。

24.一种高压集成电路的控制方法,包括以下步骤:a1:所述第一单脉冲gen22接收上位机的hin信号输出口的hin信号后产生第一脉冲,其中所述第一单脉冲gen22在hin信号的上升沿和下降沿时产生第一脉冲,当在hin信号的上升沿时,所述第一单脉冲gen22的上升沿输出端导通,第一脉冲通过所述第一单脉冲gen22的上升沿输出端输入到所述第一或门24的输入端a1,当在hin信号的下降沿时,所述第一单脉冲gen22的下降沿输出端导通,第一脉冲通过所述第一单脉冲gen22的下降沿输出端输入到所述第二或门25的输入端b1;a2:所述mcu处理器1通过所述电压检测单元4采集所述高侧驱动单元5的输出端vs的电压;当所述高侧驱动单元5的输出端vs的电压低于设定值时,所述mcu处理器1通过其自身的清零信号输出端/cr触发所述移位寄存器21清零后,所述mcu处理器1通过其自身的pwm输出端tys输送pwm波到所述移位寄存器21的时钟管脚cpa,执行步骤a3;当所述高侧驱动单元5的输出端vs的电压低于设定值时,所述mcu处理器1不会触发所述移位寄存器21的清零管脚cr,所述mcu处理器1不会输送pwm波到所述移位寄存器21的时钟管脚cpa;a3:所述移位寄存器21运行,同步接收上位机的hin信号输出口的hin信号并延时s秒后触发所述第二单脉冲gen23产生第二脉冲,其中延时时间s=1/f,f为额定占空比的pwm波的频率,所述第二单脉冲gen23在hin信号的上升沿和下降沿时产生第二脉冲,当在hin信号的上升沿时,所述第二单脉冲gen23的上升沿输出端导通,第二脉冲通过所述第二单脉冲gen23的上升沿输出端输入到所述第一或门24的输入端b2,从而在所述第一或门24的输入端b2当在hin信号的下降沿时,所述第二单脉冲gen23的下降沿输出端导通,第二脉冲通过所述第二单脉冲gen23的下降沿输出端输入到所述第二或门25的输入端a2;如图7所示,所述第一或门24根据其自身的输入端a1的输入信号和输入端b2的输入信号作或运算,得到结果后通过其自身的输出端a3输入到所述高侧驱动单元5内的n沟道dmos管q1的栅极;所述第二或门25根据其自身的输入端b1的输入信号和输入端a2的输入信号作或运算,得到结果后通过其自身的输出端b3输入到所述高侧驱动单元5内的n沟道dmos管q2的栅极。其中,所述第一或门24根据其自身的输入端a1的输入信号和输入端b2的输入信号作或运算得到结果为脉冲信号g1,所述第二或门25根据其自身的输入端b1的输入信号和输入端a2的输入信号作或运算得到结果为脉冲信号g2。

25.经过移位寄存器21的hin信号会延迟s秒后再输入到第二单脉冲gen23,使所述第二单脉冲gen23产生第二脉冲并发送到第一或门24的输入端b2或第二或门25的输入端a2,没有经过移位寄存器21而直接由第一单脉冲gen22产生并发送到第一或门24的输入端a1或第二或门25的输入端b1的第一脉冲没有延迟,就能与所述第二脉冲在时间上有所间隔,从而形成双脉冲,确保所述高侧驱动单元5的rs触发器51能获取信号,使用双脉冲时,相当于增加了脉冲的存在时间,给足了时间让所述高侧驱动单元5的n沟道dmos管q1或n沟道dmos

管q2导通,从而保证了所述rs触发器51能获取信号,从而保证所述rs触发器51产生的控制信号准确。优选地,额定占空比的pwm波的占空比为50%。

26.优选的,在所述步骤a3中,所述mcu处理器1根据其自身的温度输入端tv采集到的高压集成电路的封装内的温度来调节所述pwm波的频率f,当温度升高时,所述pwm波的频率f减少,当温度降低时,所述pwm波的频率f增大。如图8所示,当温度升高时,所述pwm波的频率f减少,所述移位寄存器21的延时时间s增大,第一脉冲和第二脉冲之间的距离增大,当温度降低时,所述pwm波的频率f增大,所述移位寄存器21的延时时间s减少,第一脉冲和第二脉冲之间的距离减少,从而避免所述高压集成电路过热而损坏。

27.一些实施例中,在所述步骤a3中预设定多个温度范围和多个预设频率,所述温度范围与所述预设频率一一对应,所述mcu处理器1根据所述温度范围选取对应的预设频率并赋予给所述pwm波的频率f。如此,mcu处理器1就能根据温度范围直接获得对应的预设频率,然后使用该预设频率作为所述pwm波的频率f,从而提高运算速度和反应速度。

28.根据本发明实施例的一种高压集成电路及其控制方法的其他构成等以及操作对于本领域普通技术人员而言都是已知的,这里不再详细描述。

29.在本说明书的描述中,参考术语“实施例”、“示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

30.尽管已经示出和描述了本发明的实施例,本领域的普通技术人员可以理解:在不脱离本发明的原理和宗旨的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1