一种异步主从自时钟数据变化检测器的制作方法

1.本发明涉及时钟检测技术领域,特别是涉及一种异步主从自时钟数据变化检测器。

背景技术:

2.目前已有的自时钟状态机的自时钟模块是通过判定输入数据的变化产生自时钟信号,电路逻辑结构是通过相应状态机具体功能的状态转换表产生的,电路结构不固定,设计不具有通用性,而且对输入数据的毛刺敏感从而造成状态转换的误触发,进而影响状态机的功能正确性。并且目前已有的输入变化检测电路,虽然实现对输入数据变化的检测,但是他对输入数据的检测点是寄存器的输入,所以需要窄脉冲生成模块将已经变为高电平的自时钟输出信号复位,而窄脉冲生成模块无法通过hdl进行行为级描述,而且增加了额外的硬件开销。

技术实现要素:

3.本发明的目的是提供一种异步主从自时钟数据变化检测器,结构简单固定,不产生毛刺且对输入数据的毛刺不敏感从而提高了状态机功能的正确性,不需要通过窄脉冲生成模块产生自时钟信号从而降低硬件开销。

4.为实现上述目的,本发明提供了如下方案:

5.一种异步主从自时钟数据变化检测器,包括:

6.主锁存器、从锁存器和多输入异或门;所述主锁存器的输出端分别与所述从锁存器的输入端和所述多输入异或门的输入端连接,所述主锁存器的使能输入端与所述多输入异或门的使能输出端连接,所述从锁存器的输出端与所述多输入异或门的输入端连接,所述从锁存器的使能输入端与所述多输入异或门的使能输出端连接。

7.可选的,所述多输入异或门的位宽为n位。

8.可选的,所述多输入异或门包括:n个两输入异或门和一个n输入或门;n个所述两输入异或门的输入端为所述多输入异或门的输入端,n个所述两输入异或门的输出端均与所述n输入或门的输入端连接,所述n输入或门的输出端为所述多输入异或门的使能输出端。

9.根据本发明提供的具体实施例,本发明公开了以下技术效果:本发明异步主从自时钟数据变化检测器包括:主锁存器、从锁存器和多输入异或门;主锁存器的输出端分别与从锁存器的输入端和多输入异或门的输入端连接,主锁存器的使能输入端与多输入异或门的使能输出端连接,从锁存器的输出端与多输入异或门的输入端连接,从锁存器的使能输入端与多输入异或门的使能输出端连接,基于主从锁存器和异或门相对基于状态转换表方法生成的异步自时钟生成器具有结构简单固定,不产生毛刺,响应速度快且对输入数据毛刺不敏感的优点,提高了状态机功能的正确性,相对于输入变化检测电路增加了主从结构,所以不需要通过窄脉冲生成模块电路产生自时钟信号,可以降低硬件开销。

附图说明

10.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

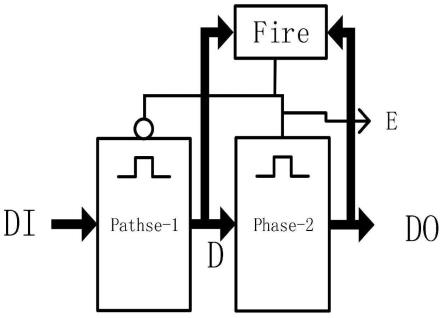

11.图1为本发明实施例提供的一种异步主从自时钟数据变化检测器的结构示意图;

12.图2为本发明实施例提供的多输入异或门的结构示意图。

13.符号说明:

14.phase-1-主锁存器、phase-2-从锁存器、fire-多输入异或门、di-主锁存器的输入端、d-主锁存器的输出端、do-从锁存器的输出端、e-多输入异或门的使能输出端。

具体实施方式

15.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

16.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

17.本发明公开了一种可以产生异步自时钟信号的基于主从锁存器和异或门的数据变化检测器,如图1所示,包括主锁存器phase-1、从锁存器phase-2和多输入异或门fire;所述主锁存器的输入端为异步主从自时钟数据变化检测器的输入端,所述主锁存器的输出端d分别与所述从锁存器phase-2的输入端和多输入异或门fire的输入端连接,所述主锁存器phase-1的使能输入端与所述多输入异或门的使能输出端e连接,所述从锁存器的输出端do与所述多输入异或门fire的输入端连接,所述从锁存器phase-2的使能输入端与所述多输入异或门的使能输出端e连接,多输入异或门的使能输出端e为异步主从自时钟数据变化检测器的输出端,具体的:主锁存器phase-1,数据输入连接锁存器的输入端di,d连接从锁存器phase-2的数据输入端和多输入异或门fire的数据输入端,使能输入连接多输入异或门的使能输出端e。从锁存器phase-2,数据输入连接d,数据输出连接do和多输入异或门fire的数据输入,使能输入连接多输入异或门的使能输出端e。多输入异或门fire,数据输入连接d和do,e连接主锁存器phase-1的使能输入和从锁存器phase-2的使能输入。

18.在实际应用中,所述多输入异或门fire的位宽为n位。

19.在实际应用中,如图2所示,多输入异或门fire包括:n个两输入异或门和一个n输入或门;n个所述两输入异或门的输入端为所述多输入异或门fire的输入端,n个所述两输入异或门的输出端均与所述n输入或门的输入端连接,所述n输入或门的输出端为所述多输入异或门的使能输出端e,n个两输入异或门分别对比对应位数的输入数据d和输出数据do是否有差异,对比结果通过n输入或门产生自时钟使能输出e。

20.本发明公开了一种异步主从自时钟数据变化检测器,主要用于异步状态机的自时钟信号产生,输入数据变化检测和毛刺过滤,具体功能如下,当本发明提供的异步主从自时钟数据变化检测器的di和do相同时,本发明提供的异步主从自时钟数据变化检测器处于加

载状态(相位1),此时主锁存器phase-1为导通状态,从锁存器phase-2为锁存状态。当di发生变化且与当前输出数据不同时,输入数据通过主锁存器phase-1到达其输出d,此时多输入异或门的使能输出端e产生高电平使得主锁存器phase-1锁存,从锁存器phase-2导通,本发明提供的异步主从自时钟数据变化检测器进入开火状态(相位2)。当数据通过从锁存器phase-2导通传输到do,多输入异或门的使能输出端e产生低电平使得主锁存器phase-1导通,从锁存器phase-2锁存,本发明提供的异步主从自时钟数据变化检测器重新回到加载状态。上述过程中多输入异或门的使能输出端e产生的脉冲输出就是变化的数据所捆绑的自时钟信号。

21.由于主锁存器phase-1导通时数据输入到输出,从锁存器phase-2导通时数据输入到输出和多输入异或门fire的数据输入到使能输出都存在延迟,所以通过调节多输入异或门的使能输出端e上的延迟大小,可以过滤掉数据输入毛刺,可以对一定宽度以下的毛刺数据不敏感,从而也可以起到对输入数据的低通滤波的作用。

22.由于多输入异或门fire的每个输入到输出的路径长度相等,所以多输入异或门fire的自时钟信号输出不会产生毛刺。

23.本发明有以下技术效果:

24.相对基于状态转换表方法生成的异步自时钟生成器具有结构简单固定,不产生毛刺,响应速度快且对输入数据毛刺不敏感的优点,提高了状态机功能的正确性。相对于输入变化检测电路增加了主从结构,所以不需要通过窄脉冲生成模块电路产生自时钟信号降低了硬件开销。

25.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

26.本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1