振动器件的制作方法

1.本发明涉及振动器件。

背景技术:

2.专利文献1公开了一种石英振子,该石英振子是经由金属凸块将石英振动元件固定在封装上的振动器件。

3.专利文献1:日本特开2016-127469号公报

4.但是,在专利文献1记载的振动器件中,金属凸块的弹性模量(杨氏模量)较高且较硬,因此,例如容易因如下的热应力而发生塑性变形,所述热应力是因石英振动元件和封装的线膨胀系数差而产生的。存在这样的问题:当金属凸块塑性变形时,在石英振动元件中产生不需要的振动和频率滞后,从而振动特性劣化。

技术实现要素:

5.振动元件具有:基座,其具有处于正反关系的第1面和第2面;振动元件,其相对于所述基座位于所述第1面侧,具有振动基板和配置在所述振动基板的所述基座侧的面上的电极;导电层,其配置在所述第1面,具有与所述电极接合的接合部;以及应力缓和层,其介于所述基座与所述导电层之间,在俯视所述基座时,至少一部分与所述接合部重叠,所述应力缓和层具有从所述导电层露出的露出部。

附图说明

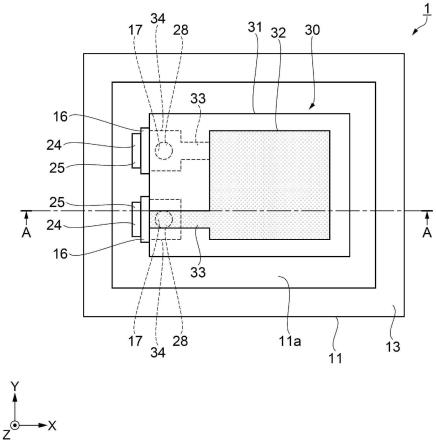

6.图1是示出第1实施方式的振动器件的概要结构的俯视图。

7.图2是图1中的a-a线剖视图。

8.图3是示出振动器件的概略构造的俯视图。

9.图4是示出第2实施方式的振动器件的概要结构的俯视图。

10.图5是示出第3实施方式的振动器件的概要结构的俯视图。

11.图6是示出第4实施方式的振动器件的概要结构的俯视图。

12.图7是图6中的b-b线剖视图。

13.图8是示出第5实施方式的振动器件的概要结构的俯视图。

14.图9是图8中的c-c线剖视图。

15.图10是示出第5实施方式的振动器件的概要结构的俯视图。

16.标号说明

17.1、1a、1b、1c、1d振动器件;10封装;11基座;11a第1面;11b第2面;12盖;13接合部件;14外部端子;15绝缘膜;16导电层;17接合部;18布线部;19连接部;20贯穿孔;21贯穿电极;22布线;24应力缓和层;25露出部;27凹部;28导电性部件;29内部空间;30振动元件;31振动基板;32激励电极;33引线电极;34电极;66集成电路;67振荡电路。

具体实施方式

18.1.第1实施方式

19.首先,参照图1、图2以及图3,对第1实施方式的振动器件1进行说明。

20.另外,在图1中,为了便于说明振动器件1的内部结构,图示了取下盖12的状态。另外,在图3中,为了便于说明振动器件1的内部结构,图示了取下盖12和振动元件30的状态。另外,为了便于说明,在以后的各图中,作为相互正交的3个轴,图示了x轴、y轴以及z轴。另外,将沿着x轴的方向称为“x方向”,将沿着y轴的方向称为“y方向”,将沿着z轴的方向称为“z方向”。另外,将各轴的箭头侧称为“正侧”,将与箭头相反的一侧称为“负侧”。另外,也将z方向正侧称为“上”,将z方向负侧称为“下”。另外,在本实施方式中,x方向为第1方向,y方向为第2方向。

21.如图1及图2所示,振动器件1具有:由基座11和盖12构成的封装10;以及收纳于封装10的内部空间29内的振动元件30。

22.封装10具有基座11和与基座11接合的盖12,在形成于基座11与盖12之间的内部空间29中收纳有振动元件30。

23.基座11是包含单晶硅的半导体基板,特别是在本实施方式中为硅基板。另外,基座11没有特别限定,可以使用硅以外的半导体基板,例如锗、砷化镓、磷化镓、氮化镓、碳化硅等的半导体基板,也可以使用陶瓷基板那样的半导体基板以外的基板。

24.基座11为板状,具有配置有振动元件30的第1面11a和与第1面11a处于正反关系的第2面11b。另外,在基座11的除了与盖12的接合区域以外的表面上形成有绝缘膜15。

25.在基座11的第1面11a配置有:导电层16,其具有经由金属凸点等导电性部件28与配置在振动元件30的振动基板31的基座11侧的面上的电极34接合的接合部17;以及应力缓和层24,其介于基座11与导电层16之间,如图2和图3所示,在俯视即从z方向观察基座11时,至少一部分与接合部17重叠。另外,配置在第1面11a上是指接合在第1面11a上。因此,在第1面11a上依次层叠并接合有应力缓和层24、导电层16、导电性部件28、电极34。

26.导电层16具有作为与导电性部件28接合的区域的接合部17、配置于基座11的第1面11a的布线部18、以及连接接合部17和布线部18的连接部19。

27.应力缓和层24包含树脂材料而形成,作为树脂材料的例子,是环氧树脂、丙烯酸树脂、聚酰亚胺树脂、酚醛树脂等具有耐热性的材料。通过在基座11与导电层16之间夹设弹性模量比导电层16或导电性部件28小的柔软的应力缓和层24,能够得到较高的应力缓和效果,能够抑制起因于振动元件30与封装10的线膨胀系数差而产生的导电层16或导电性部件28的塑性变形导致的振动元件30的不需要的振动或频率滞后的产生或振动特性的劣化。

28.此外,在从z方向俯视时,应力缓和层24在作为第1方向的x方向的负侧具有从导电层16露出的露出部25。因此,与导电层16覆盖应力缓冲层24的整体而形成的情况相比,能够抑制经由导电性部件28接合振动元件30的电极34和导电层16时施加的热冷却时产生的应力缓冲层24的变形所引起的导电层16的龟裂或断线。

29.另外,在本实施方式中,经由导电性部件28接合导电层16和电极34,但也可以直接接合导电层16和电极34。此时,导电层16的接合部17是与电极34接合的区域。

30.在基座11的第2面11b形成有经由电极34、导电层16等与振动元件30的激励电极32电连接的外部端子14。

31.另外,在基座11上形成有在厚度方向上贯穿基座11的一对贯穿孔20。在贯穿孔20内填充导电性材料,形成贯穿电极21。另外,如图2和图3所示,在基座11的第1面11a配置有与振动元件30电连接的导电层16。导电层16经由贯穿电极21及形成于基座11的第2面11b的布线22与外部端子14电连接。因此,通过从外部端子14施加电压,能够经由激励电极32使振动元件30振动,能够从外部端子14向外部输出振动信号。

32.收纳在内部空间29中的振动元件30位于基座11的第1面11a侧,具有振动基板31、使振动基板31振动的激励电极32、向外部输出振动信号并配置在振动基板31的基座11侧的面上的电极34、以及将激励电极32和电极34电连接的引线电极33。

33.振动元件30经由导电性部件28配置在封装10的第1面11a上。另外,作为振动基板31,可使用at切石英基板、sc切石英基板、bt切石英基板等。

34.盖12与基座11同样是硅基板。由此,基座11和盖12的线膨胀系数相等,抑制了由热膨胀引起的热应力的产生,成为具有优异振动特性的振动器件1。此外,能够通过半导体工艺形成振动器件1,因此,能够高精度地制造振动器件1,并且能够实现其小型化。但是,盖12没有特别限定,也可以使用硅以外的半导体基板,例如锗、砷化镓、磷化镓、氮化镓、碳化硅等的半导体基板。另外,例如也可以使用可伐合金等的金属基板、玻璃基板等非半导体基板的基板。

35.盖12具有带底的凹部27,凹部27在基座11侧开口,在内部收纳振动元件30。而且,盖12在其下表面经由接合部件13与基座11接合。因此,盖12与基座11一起形成收纳振动元件30的内部空间29。另外,基座11和盖12的接合方法也可以不通过接合部件13,而是利用基座11或盖12包含的金属之间的扩散的扩散接合等接合方法。

36.另外,内部空间29是气密的,为减压状态,优选为更接近真空的状态。由此,粘性阻力减少,振动元件30的振荡特性提高。但是,内部空间29的环境没有特别限定,例如可以是封入氮或氩等惰性气体的环境,也可以不是减压状态而是大气压状态或加压状态。

37.如上所述,本实施方式的振动器件1在基座11与导电层16之间配置有弹性模量比导电层16、导电性部件28小且柔软的应力缓和层24,因此,能够得到较高的应力缓和效果,能够抑制因振动元件30与封装10的线膨胀系数差而产生的导电层16、导电性部件28的塑性变形引起的振动元件30的不需要的振动、频率滞后的产生以及振动特性的劣化。

38.另外,应力缓冲层24具有从导电层16露出的露出部25,所以,与导电层16覆盖应力缓冲层24的整体而形成的情况相比,能够抑制在经由导电性部件28接合振动元件30的电极34和导电层16时施加的热冷却时产生的应力缓冲层24的变形所引起的导电层16和应力缓冲层24的紧贴度的降低导致的剥离、以及龟裂导致的断线。

39.2.第2实施方式

40.接下来,参照图4对第2实施方式的振动器件1a进行说明。另外,在图4中,为了便于说明振动器件1a的内部结构,图示了取下盖12和振动元件30的状态。

41.本实施方式的振动器件1a与第1实施方式的振动器件1相比,具有从导电层16a的接合部17起分别向作为第1方向的x方向的正侧以及负侧延伸的第1连接部191以及第2连接部192,应力缓和层24a的露出部25a位于接合部17的y方向两侧,除此以外,与第1实施方式的振动器件1相同。另外,以与上述第1实施方式的不同点为中心进行说明,对相同的事项标注相同的标记,并省略其说明。

42.如图4所示,振动器件1a具有从导电层16a的接合部17向x方向的正侧延伸并与第1布线部181连接的第1连接部191、以及从导电层16a的接合部17向x方向的负侧延伸并与第2布线部182连接的第2连接部192。另外,应力缓和层24a的露出部25a位于接合部17的y方向两侧。

43.通过采用这种结构,能够提高导电层16a与应力缓和层24a的紧贴度,能够得到与第1实施方式的振动器件1相同的效果。

44.3.第3实施方式

45.接下来,参照图5,对第3实施方式的振动器件1b进行说明。另外,在图5中,为了便于说明振动器件1b的内部结构,图示了取下盖12和振动元件30的状态。

46.本实施方式的振动器件1b与第1实施方式的振动器件1相比,具有从导电层16b的接合部17分别向作为第1方向的x方向的正侧以及负侧延伸的第1连接部191以及第2连接部192、和从导电层16b的接合部17分别向作为与第1方向相交的第2方向的y方向的正侧以及负侧延伸的第3连接部193以及第4连接部194,应力缓和层24b的露出部25b位于应力缓和层24b的上表面的四角处,除此以外,与第1实施方式的振动器件1相同。另外,以与上述第1实施方式的不同之处为中心进行说明,对相同的事项标注相同的标记,并省略其说明。

47.如图5所示,振动器件1b具有从导电层16b的接合部17向x方向的正侧延伸并与第1布线部181连接的第1连接部191、从导电层16b的接合部17向x方向的负侧延伸并与第2布线部182连接的第2连接部192、从导电层16b的接合部17向y方向的正侧延伸并与第3布线部183连接的第3连接部193、从导电层16b的接合部17向y方向的负侧延伸并与第4布线部184连接的第4连接部194。另外,应力缓和层24b的露出部25b位于应力缓和层24b的上表面的四角。

48.通过采用这种结构,能够进一步提高导电层16b与应力缓和层24b的紧贴度,能够得到与第1实施方式的振动器件1相同的效果。

49.4.第4实施方式

50.接下来,参照图6以及图7,对第4实施方式的振动器件1c进行说明。另外,在图6中,为了便于说明振动器件1c的内部结构,图示了取下盖12和振动元件30的状态。

51.本实施方式的振动器件1c与第1实施方式的振动器件1相比,第1应力缓和层241和第2应力缓和层242一体化,第1应力缓和层241和第2应力缓和层242的露出部25c配置在第1导电层161和第2导电层162之间,除此以外,与第1实施方式的振动器件1相同。另外,以与上述第1实施方式的不同点为中心进行说明,对相同的事项标注相同的标记,并省略其说明。

52.如图6和图7所示,振动器件1c具有经由导电性部件28与第1电极341接合的第1导电层161、经由导电性部件28与第2电极342接合的第2导电层162、介于基座11和第1导电层161之间的第1应力缓和层241以及介于基座11和第2导电层162之间的第2应力缓和层242,第1应力缓和层241和第2应力缓和层242一体化。另外,第1应力缓和层241和第2应力缓和层242的露出部25c位于第1导电层161和第2导电层162之间。

53.通过采用这种结构,能够使应力缓和层241、242的制造变得容易,进一步实现小型化,能够得到与第1实施方式的振动器件1相同的效果。

54.5.第5实施方式

55.接下来,作为第5实施方式的振动器件1d的一例,列举具有使振动元件30振荡的振

荡电路67的振荡器,参照图8、图9以及图10进行说明。另外,在图8中,为了便于说明振动器件1d的内部结构,图示了取下盖52的状态。另外,在图10中,为了便于说明振动器件1d的内部结构,图示了取下盖52和振动元件30的状态。

56.本实施方式的振动器件1d与第1实施方式的振动器件1相比,在基座51的第2面51b形成有包括振荡电路67的集成电路66,除此以外,与第1实施方式的振动器件1相同。另外,以与上述第1实施方式的不同点为中心进行说明,对相同的事项标注相同的标记,并省略其说明。

57.如图8以及图9所示,振动器件1d具有:封装50,其由基座51、经由接合部件53与基座51接合的盖52构成;以及收纳在封装50的内部空间60的振动元件30。

58.基座51及盖52是包含单晶硅的半导体基板,特别是在本实施方式中为硅基板。另外,基座51及盖52没有特别限定,也可以使用硅以外的半导体基板,例如锗、砷化镓、磷化镓、氮化镓、碳化硅等的半导体基板。

59.基座51为板状,具有配置有振动元件30的第1面51a和与第1面51a处于正反关系的第2面51b。另外,在基座51的除了与盖52的接合区域以外的表面形成有绝缘膜55。

60.在基座51的第1面51a层叠配置有应力缓和层24和导电层16,经由导电性部件28与振动元件30接合。

61.在基座51的第2面51b配置有包含与振动元件30电连接的振荡电路67的集成电路66。通过在基座51上形成集成电路66,能够有效利用基座51。特别是,通过在第2面51b形成集成电路66,与在第1面51a形成集成电路66的情况相比,没有与盖52的接合区域,相应地能够较宽地确保集成电路66的形成空间。但是,集成电路66也可以不形成于基座51的第2面51b,而形成于第1面51a。

62.集成电路66包括振荡电路67,振荡电路67与振动元件30电连接,使振动元件30振荡而生成时钟信号等振荡信号。集成电路66除了振荡电路67之外还可以包含电路。该电路例如可列举处理来自振荡电路67的输出信号的处理电路,这样的处理电路例如可列举pll电路。

63.在第2面51b形成有布线层62、绝缘层63、钝化膜64以及端子层65层叠而成的层叠体61。而且,形成于第2面51b的未图示的多个有源元件经由布线层62包含的布线56电连接而构成集成电路66。另外,端子层65具有与振荡电路67电连接的多个安装端子54。另外,在图示的结构中,层叠体61包含1个布线层62,但不限于此,多个布线层62也可以隔着绝缘层63层叠。即,布线层62和绝缘层63可以交替层叠多次。由此,例如能够提高电路内的布线56的走线、多个安装端子54的设置的自由度。

64.另外,在基座51形成有沿厚度方向贯穿基座51的一对贯穿孔57。在贯穿孔57内填充导电性材料,形成贯穿电极58。另外,如图9及图10所示,在第1面51a侧的贯穿电极58上配置有与振动元件30电连接的导电层16。因此,导电层16能够经由贯穿电极58与振荡电路67电连接,能够使振动元件30振荡。

65.盖52具有带底的凹部59,凹部59在基座51侧开口,在内部收纳振动元件30。而且,盖52在其下表面经由接合部件53与基座51接合。由此,盖52与基座51一起形成收纳振动元件30的内部空间60。

66.另外,内部空间60是气密的,为减压状态,优选为更接近真空的状态。由此,粘性阻

力减少,振动元件30的振荡特性提高。但是,内部空间60的环境没有特别限定,例如可以是封入了氮或氩等惰性气体的环境,也可以不是减压状态而是大气压状态或加压状态。

67.通过采用这种结构,能够实现具有振荡电路67的振动器件1d的小型化,能够得到与第1实施方式的振动器件1相同的效果。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1