一种与合路器融合的电压模PAM-4驱动器

一种与合路器融合的电压模pam-4驱动器

技术领域

1.本技术涉及集成电路设计技术领域,特别是涉及一种与合路器融合的电压模pam-4驱动器。

背景技术:

2.电压模驱动器具有高线性、高摆幅特点,在pam-4(four pulse amplitude modulation,四电平脉冲调制)调制的高速串口发射机中得到了广泛应用。传统结构如图1所示,合路器将低速并行输入转换为一路串行输出,然后由驱动器发送到信道上。驱动器输入节点a、b、c、d处于全速率传输状态(即数据率等于波特率),要求此节点处的带宽不小于奈奎斯特频率。然而由于节点处存在寄生电容(主要包括驱动器输入级栅电容、合路器输出漏极电容),并且为实现阻抗匹配,驱动器往往选用大尺寸反相器,进一步增大了寄生电容,限制了带宽的提升,使得传统结构无法满足日益飞涨的数据传输速度的要求。

技术实现要素:

3.基于此,为解决上述技术问题,本发明提出了一种缓解寄生电容限制带宽的与合路器融合的电压模pam-4驱动器。

4.第一电压模支路,第二电压模支路,第三电压模支路,第四电压模支路以及负载;第一电压模支路和第二电压模支路构成正极差分信号输出端,第三电压模支路和第四电压模支路构成负极差分信号输出端;电压模支路包括:三态门选择器组和匹配阻抗,匹配阻抗一端与三态门选择器组的输出端连接,匹配阻抗另一端与负载连接;通过时钟电平的控制,实现三态门选择器组中三态门的通导,通过电压模支路输出阻抗的大小确定合成输出的权重。

5.在其中一个实施例中,还包括nrz信号输出端和多相时钟信号输出端:三态门选择器组输入端分别与nrz信号输出、时钟信号输出端连接;三态门在时钟信号输出为高电平时通导,在时钟信号输出为低电平时产生高阻输出。

6.在其中一个实施例中,第一电压模支路包括:三态门选择器组一端与nrz信号输出端中的l_d端正极连接,获取信号;三态门选择器组另一端与匹配阻抗r1连接,输出正极信号。

7.在其中一个实施例中,第二电压模支路包括:三态门选择器组一端与nrz信号输出端中的m_d端正极连接,获取信号;三态门选择器组另一端与匹配阻抗r2连接,输出正极信号。

8.在其中一个实施例中,第一电压模支路和第二电压模支路为并联结构;第一电压模支路输出阻抗为第二电压模支路输出阻抗的2倍,通过时钟电平的控制,第二电压模支路和第一电压模支路按照2:1的权重合成输出正极差分信号。

9.在其中一个实施例中,第三电压模支路包括:三态门选择器组一端与nrz信号输出端中的l_d端负极连接,获取信号;三态门选择器组另一端与匹配阻抗r3连接,输出负极信

号。

10.在其中一个实施例中,第四电压模支路包括:三态门选择器组一端与nrz信号输出端中的m_d端负极连接,获取信号;三态门选择器组另一端与匹配阻抗r4连接,输出负极信号。

11.在其中一个实施例中,第三电压模支路和第四电压模支路为并联结构;第三电压模支路输出阻抗为第四电压模支路输出阻抗的2倍,通过时钟电平的控制,第四电压模支路和第三电压模支路按照2:1的权重合成输出负极极差分信号。

12.在其中一个实施例中,还包括匹配阻抗rl;将并行的正极差分信号和负极差分信号转换为一路串行差分输出信号,在匹配阻抗rl端进行叠加后,发送到信道上。

13.在其中一个实施例中,三态门选择器组可以是两个及以上三态门组成,一般是2的偶数倍;三态门之间采用并联结构。

14.上述结构与传统结构中数据流先经过合路器,再经过驱动器不同,本发明中采用三态门选择器组和匹配阻抗组成四条支路,通过时钟电平的控制,实现三态门选择器组中三态门选择器的导通,因此在两相时钟的控制下,每条支路由三态门选择器的输出直接驱动匹配阻抗,产生正极差分输出信号和负极差分输出信号,差分输出信号在负载上叠加,完成并串转换再输出到信号道上;本发明消除了全速中间节点,缓解了寄生电容限制带宽对数据传输速度的限制。相对传统结构,省去了大尺寸反相器,降低面积消耗,同时降低了动态功耗。

附图说明

15.图1为传统电压模pam-4驱动器。

16.图2为本发明提出的电压模pam-4驱动器原理图。

17.图3为本发明提出的电压模pam-4驱动器具体应用场景图。

具体实施方式

18.为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

19.为了便于理解,对基础概念进行解释。nrz信号是不归零编码,采用高、低两种信号电平来表示数字逻辑信号的1、0,每个时钟周期可以传输1bit的逻辑信息;而pam-4也叫做四电平脉冲幅度调制,是一种调制技术,采用4个不同的信号电平来进行信号传输。当采用一定的规则,将二进制中的逻辑信号转换为用四个不同的电平来进行信号输出时,使每个时钟周期可以传输的逻辑信息变成了2bit,翻了一倍,从而提高带宽数据传输速率。

20.三态门选择器是一个三态电路,可以提供三种不同输出值:逻辑“0”,逻辑“1”和高阻态,高阻态主要用来将逻辑门同系统其他部分加以隔离。所以当其输入高电位时接通,输入低电位时断开。

21.匹配阻抗是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。不会有信号反射回来源点,用以获得最大的效率。

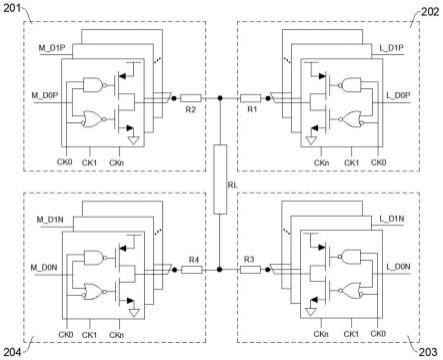

22.在其中一个实施例中,如图2所示,提出了一种电压模pam-4驱动器原理图,包括:

第一电压模支路201,第二电压模支路202,第三电压模支路203,第四电压模支路204以及负载rl;第一电压模支路201和第二电压模支路202构成正极差分信号输出端,第三电压模支路203和第四电压模支路204构成负极差分信号输出端;电压模支路包括:三态门选择器组和匹配阻抗,匹配阻抗一端与三态门选择器组的输出端连接,匹配阻抗另一端与负载连接;通过时钟电平的控制,实现三态门选择器组中三态门的通导,通过匹配阻抗的大小确定三态门选择器组合成输出的权重。

23.值得说明的是,本发明中四个电压模支路结构均相同;第一电压模支路和第二电压模支路连接nrz信号正极端,其中第一电压模支路输出阻抗是第二电压模支路输出阻抗的2倍,所以在时钟信号的控制下,按照2:1的权重输出正极差分信号vop;第三电压模支路和第四电压模支路为对称结构,只是其连接nrz信号负极端,在时钟信号的控制下,按照2:1的权重输出负极差分信号von。

24.其中涉及的“第一”、“第二”等描述仅代表命名方式,不区分大小和先后顺序,不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量;所说的电压模输出阻抗为三态门和与之相连的匹配阻抗整体的输出阻抗。

25.还包括nrz信号输出端和多相时钟信号输出端:三态门选择器组输入端分别与nrz信号输出、所述时钟信号输出端连接;三态门在时钟信号输出为高电平时通导,在时钟信号输出为低电平时产生高阻输出。

26.第一电压模支路包括:三态门选择器组一端与nrz信号输出端中的l_d端正极连接,根据三态门是否导通,获取信号;三态门选择器组另一端与匹配阻抗r1连接,输出l_d端的正极信号。

27.第二电压模支路包括:三态门选择器组一端与nrz信号输出端中的m_d端正极连接,根据三态门是否导通,获取信号;三态门选择器组另一端与匹配阻抗r2连接,输出m_d端的正极信号。

28.第一电压模支路和第二电压模支路为并联结构;第一电压模支路输出阻抗为第二电压模支路输出阻抗的2倍,通过时钟电平的控制,第二电压模支路和第一电压模支路按照2:1的权重合成输出正极差分信号。

29.第三电压模支路包括:三态门选择器组一端与nrz信号输出端中的l_d端负极连接,根据三态门是否导通,获取信号;三态门选择器组另一端与匹配阻抗r3连接,输出l_d端的负极信号。

30.第四电压模支路包括:三态门选择器组一端与nrz信号输出端中的m_d端负极连接,根据三态门是否导通,获取信号;三态门选择器组另一端与匹配阻抗r4连接,输出m_d端的负极信号。

31.第三电压模支路和第四电压模支路为并联结构;第三电压模支路输出阻抗为第四电压模支路输出阻抗的2倍,通过时钟电平的控制,第四电压模支路和第三电压模支路按照2:1的权重合成输出负极差分信号。

32.还包括匹配阻抗rl;将并行的正极差分信号和负极差分信号转换为一路串行差分输出信号,在匹配阻抗rl处进行叠加后,发送到信道上。

33.三态门选择器组可以是两个及以上三态门组成,一般是2的偶数倍;三态门之间采用并联结构。

34.在其中一个实施例中,如图3所示,对合路器融合的电压模pam-4驱动器具体应用场景进行详细说明:

35.参见图3,三态门sel1\sel2与匹配阻抗r1组成第一电压模支路,输出阻抗为150欧姆;三态门sel3\sel4与匹配阻抗r2组成第二电压模支路,输出阻抗为75欧姆;三态门sel5\sel6与匹配阻抗r3组成第三电压模支路,输出阻抗为150欧姆;三态门sel7\sel8与匹配阻抗r4组成第四电压模支路,输出阻抗为75欧姆,差分输出负载rl=100欧姆。根据电阻分压规律,第二电压模支路和第四电压模支路在合成输出信号时,其权重为第一电压模支路和第三电压模支路的2倍,从而可以完成nrz信号合成pam-4输出信号的功能。

36.其中涉及的“sel1”、“sel2”等描述仅代表命名方式,不区分大小和先后顺序,不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。

37.本发明结构还包括nrz信号输出端和两相时钟信号输出端,其中nrz输入信号为:m_d0p/m_d0n、m_d1p/m_d1n、l_d0p/l_d0n、l_d1p/l_d1n四对差分信号,两相时钟信号为:输入时钟为0相位的时钟ck0和输入时钟为180的时钟ck180。

38.三态门sel1\sel2输入端与匹配阻抗r1连接,三态门sel1输入端与l_d0p端、时钟ck0端连接;三态门sel2输入端与l_d1p端、时钟ck180端连接。

39.三态门sel3\sel4输入端与匹配阻抗r2连接,三态门sel3输入端与m_d0p端、时钟ck0端连接;三态门sel4输入端与m_d1p端、时钟ck180端连接。

40.三态门sel5\sel6输入端与匹配阻抗r3连接,三态门sel5输入端与l_d0n端、时钟ck0端连接;三态门sel6输入端与l_d1n端、时钟ck180端连接。

41.三态门sel7\sel8输入端与匹配阻抗r4连接,三态门sel7输入端与m_d0n端、时钟ck0端连接;三态门sel8输入端与m_d1n端、时钟ck180端连接。

42.以sel1\sel2进行说明三态门工作原理:当时钟ck0为高电平时,ck180为低电平,sel2输出高阻,sel1导通,l_d0p被选通到输出端v1p;同理,当ck0为低电平时,ck180为高电平,l_d1p被选通到输出端v1p。因此,在两相时钟ck0/ck180的控制下,sel1\sel2实现了2:1合路器。

43.同理,增加三态门数量,通过多相时钟的控制,也可以实现同原理的多重合路器功能。

44.本发明pam-4驱动器的整体工作原理为:当时钟ck0为高电平时,三态门sel1、三态门sel3导通,m_d0p和l_d0p按照2:1的权重合成输出正极差分信号vop;三态门sel5、三态门sel7导通,m_d0n和l_d0n按照2:1的权重合成输出负极差分信号von。

45.当时钟ck180为高电平时,三态门sel2、三态门sel4导通,m_d1p和l_d1p按照2:1的权重合成输出正极差分信号vop;三态门sel6、三态门sel8导通,m_d1n和l_d1n按照2:1的权重合成输出负极差分信号von。

46.正极差分信号vop和负极差分信号von完成并串转换为一路串行差分输出信号,在匹配阻抗rl端进行叠加后,发送到信道上。

47.以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

48.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并

不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1