一种叠层式碳纳米管三维集成电路及制作方法

本发明涉及新型碳纳米管薄膜晶体管电路的三维集成应用领域,具体为一种叠层式碳纳米管三维集成电路及制作方法。

背景技术:

1、随着传统半导体电子器件逐步逼近其工艺制程的物理极限,不仅器件集成度的提升受到限制,同时芯片内互连线的增加将带来了显著的电路延迟和噪声,影响了信号的传输速度和时序控制,严重限制了芯片性能进一步提升[1]。借助键合、外延或硅通孔等三维构筑技术,可以在垂直方向上增加器件数目,大幅缩减芯片子系统之间的互连线长度,从而提高芯片集成度和性能[2]。然而,现有的三维集成电路一般每一层内的电路仍采用传统的平面电路结构,限制了电路面积的进一步缩减[3]。因此,发展新型叠层式三维集成电路构筑技术,实现集成电路的三维叠层构建,是进一步提升系统集成度的关键。

2、在集成电路领域,碳纳米管被认为是下一代电子器件构筑材料之一。由于其具备低温制备工艺特性[4],可以通过层层转移与印刷方法构筑三维电子器件,为实现叠层式三维集成电路提供了坚实的材料基础。近年来,国内外研究小组在单片集成三维多功能电子系统[5]、共栅型双层柔性碳纳米管cmos逻辑电路[6]、双层碳纳米管环形振荡器[7]等领域取得了突破性的进展。然而,上述碳纳米管三维集成电路并没有实现叠层式构建,在电路面积缩减方面仍有较大的提升空间。限制叠层式构建的主要原因在于:(1)碳纳米管由于特殊的管状中空结构以及高的比表面积,极易吸附气体与液体分子,与多种材料产生掺杂效应,从而造成器件和电路难以具备足够的均匀性和稳定性。(2)垂直结构三维集成电路中,器件尺寸、金属电极与互连线等因素容易造成层间电容不能得到有效控制,导致不同层间器件性能的相互影响难以避免。

3、参考文献:

4、[1]c.s.tan,r.j.gutmann and l.r.reif.springer,new york,2008.

5、[2]j.h.ahn,h.s.kim,j.a.rogers,et al.science 2006,314,1754-1757.

6、[3]m.d.bishop,h.-s.p.wong,s.mitra,et al.ieee micro 2019,39,16-27.

7、[4]m.vinet,p.batude,c.tabone,et al.microelectron.eng.2011,88,331–335.

8、[5]m.m.shulaker,g.hills,r.s.park,et al.nature 2017,547,74-78.

9、[6]y.zhao,q.li,x.xiao,et al.acs nano 2016,10,2193–2202.

10、[7]y.xie,z.zhang,d.zhong,et al.nano research 2019,12,1810-1816.

技术实现思路

1、本发明的目的是提供一种叠层式碳纳米管三维集成电路及制作方法,采用高疏水性聚四氟乙烯作为隔离层,结合工艺要求和特点,突破隔断层通孔图形化、互连线形成、碳纳米管薄膜连续转移等关键技术,实现多层三维集成电路的叠层构筑。

2、本发明的技术方案:

3、一种叠层式碳纳米管三维集成电路,组成电路的所有器件单元在垂直方向上逐个堆叠,每一个器件单元作为一层,衬底之上的相邻两层器件单元之间通过加入聚四氟乙烯层与氧化铝层共同构成的隔离层进行分离。

4、所述的叠层式碳纳米管三维集成电路,碳纳米管三维集成电路的器件单元由衬底之上的碳纳米管薄膜晶体管构成,碳纳米管薄膜晶体管为两层以上,每层碳纳米管薄膜晶体管包括源极、漏极、半导体沟道、栅绝缘层和栅极。

5、所述的叠层式碳纳米管三维集成电路,源极、漏极和栅极采用钛/金复合层,钛层厚度为4~6nm,金层厚度为40~60nm。

6、所述的叠层式碳纳米管三维集成电路,半导体沟道由高纯度半导体性碳纳米管薄膜构成,其纯度≥99.99wt%。

7、所述的叠层式碳纳米管三维集成电路,栅绝缘层材料为氧化铝,栅绝缘层厚度为30~60nm。

8、所述的叠层式碳纳米管三维集成电路,碳纳米管薄膜晶体管的结构类型包括埋栅或顶栅型。

9、所述的叠层式碳纳米管三维集成电路,衬底选用硬质或柔性衬底。

10、所述的叠层式碳纳米管三维集成电路的制作方法,包括如下步骤:

11、(1)在衬底上制作电路第一层器件单元的栅极;

12、(2)使用原子层沉积制备栅绝缘层并采用光刻技术进行图形化;

13、(3)制作电路第一层器件单元的源极和漏极;

14、(4)采用水浴沉积技术,制作半导体性碳纳米管薄膜沟道材料,并进行图形化;

15、(5)采用旋涂技术在第一层器件单元上制备聚四氟乙烯层,并加热固化,然后通过原子层沉积制备氧化铝层,共同构成聚四氟乙烯/氧化铝隔离层;

16、(6)采用光刻与刻蚀技术进行互连通孔图形化;

17、(7)采用光刻技术与金属化工艺同时完成下一层器件单元的栅极与层间互连线的自组装;

18、(8)重复步骤(2)至(7),直到完成目标三维集成电路所需要的层数,并采用金属化工艺进行最后一层与第一层器件单元的电学连接。

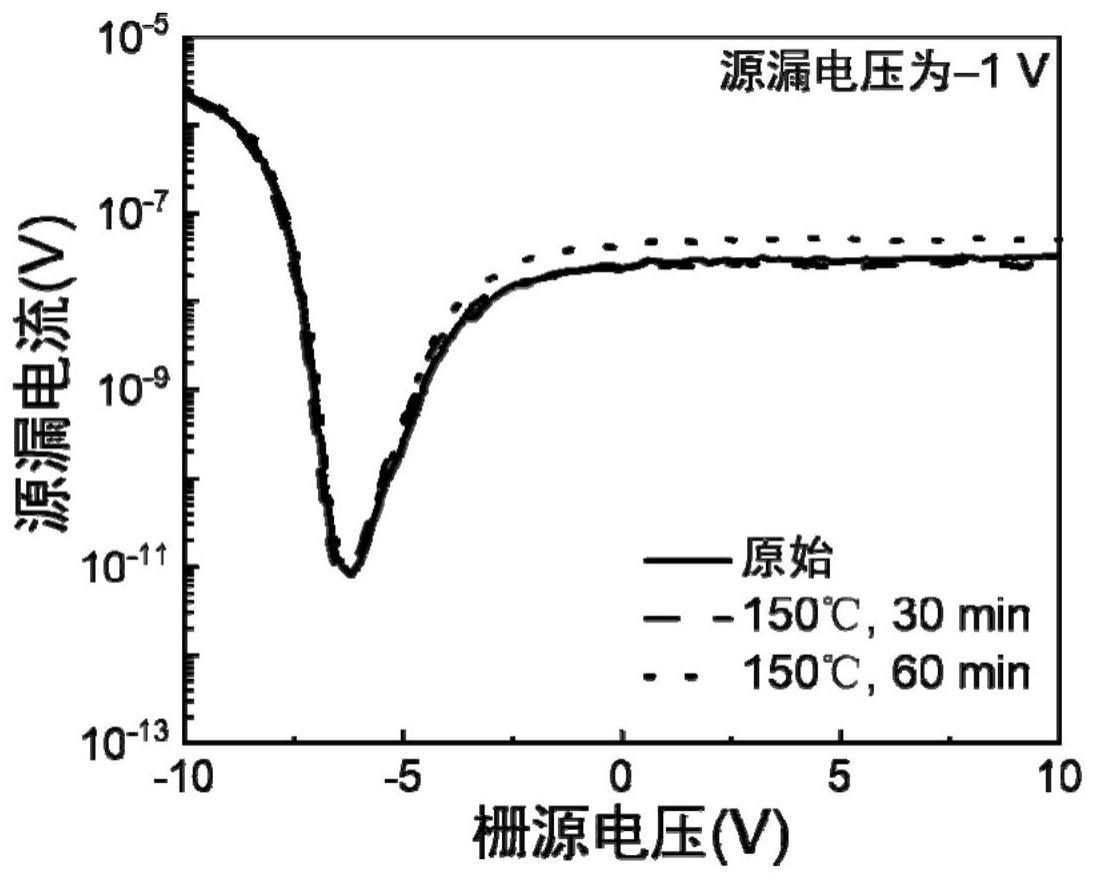

19、所述的叠层式碳纳米管三维集成电路的制作方法,步骤(5)中,通过控制旋涂转速调节聚四氟乙烯的厚度,通过调控固化温度与时间调节聚四氟乙烯的粘合度,提高稳定性;其中,旋涂转速为1000~2000rpm,时间50~60s,固化温度为150~200℃,时间为10~60min。

20、所述的叠层式碳纳米管三维集成电路的制作方法,步骤(5)的聚四氟乙烯/氧化铝隔离层中,聚四氟乙烯层厚度为100~150nm,氧化铝层厚度为50~70nm;采用反应离子刻蚀技术,同时刻蚀聚四氟乙烯与氧化铝形成互连通孔。

21、本发明的设计思想:

22、随着半导体器件尺寸逼近物理极限,发展三维集成电路以突破传统平面电路的维度限制,对于进一步提升器件集成度具有重要意义。碳纳米管薄膜具有低温制备和易于转移的特性,被认为是构建三维集成电路的理想材料。然而,由于缺乏有效的器件设计和构筑方法,不同层间器件性能的相互影响难以避免,已有的碳纳米管三维晶体管器件在集成度方面仍难以满足应用要求。

23、本发明利用高纯度半导体性碳纳米管水溶液制备的碳纳米管薄膜作为沟道材料,利用具有良好绝缘性、疏水性与化学稳定性的聚四氟乙烯作为隔离层材料,考察不同层器件的性能差异及层间器件的相互作用,阐明隔离层材料类型与叠层式碳纳米管三维集成电路构筑的关联关系,通过材料选择抑制环境因素对碳纳米管薄膜沟道的影响,构建出层层垂直堆叠于单一器件单元之上的叠层式碳纳米管三维集成电路,揭示影响碳纳米管薄膜晶体管器件性能的关键因素与科学规律,以及碳纳米管薄膜晶体管稳定性与环境因素的内在关联,实现电路平面结构向三维结构的直接转换,为碳基三维集成电路集成度的持续提升提供新策略。另外,本发明通过沉积氧化铝改善聚四氟乙烯亲疏水性,使其兼容于cmos工艺,从而可利用光刻和金属化工艺实现层间互连线的自组装,进一步简化制备工艺。

24、本发明的优点及有益效果是:

25、1)本发明利用高疏水性的聚四氟乙烯作为隔离层,抑制环境因素对碳纳米管薄膜沟道的影响,提高器件稳定性,实现多层三维集成电路的叠层构筑,有效缩减电路版图面积,为碳基三维集成电路集成度的持续提升提供新策略,推动器件集成度的进一步提升和柔性电子器件的发展。

26、2)本发明提出通过沉积氧化铝改善聚四氟乙烯表面亲疏水性的技术方法,提升聚四氟乙烯与cmos工艺兼容性,有益于互连通孔图形化与互连线自组装,为高集成度碳基电子器件及系统的研制提供科学方案。

- 还没有人留言评论。精彩留言会获得点赞!