分路混合器电流传送器的制作方法

分路混合器电流传送器

1.本技术是分案申请,原申请的申请号是201980033792.3,原申请日是2019年06月13日,原申请的全部内容通过引用结合在本技术中。

2.相关申请案交叉申请

3.本技术要求2018年6月13日提交美国专利局、发明名称为“分路混合器电流传送器”、申请号为16/007,711的美国非临时专利申请的优先权,该申请通过引用整体并入本文。

技术领域

4.本公开大体涉及电子电路和方法,并且特别涉及分路混合器电流传送器电路和相关方法。

背景技术:

5.电流传送器是用于将电流从第一电路传送到第二电路的电子放大器。电流传送器防止了第二电路不期望地加载第一电路的输出电流而干扰第一电路的操作。电流传送器可以具有单位电流增益,在这种情况下,电流传送器不改变通过的电流的幅值。理想的电流传送器具有无穷大的输出阻抗和零输入阻抗。当然,理想的电流传送器无法用现实世界的物理组件来实现。但是,在电流传送器中可以实现高输出阻抗和低输入阻抗。在本文中,在输出端具有电阻性负载的电流传送器称为跨阻放大器。跨阻放大器(trans-impedance amplifier,tia)是一种接收电流并输出电压的放大器。换句话说,tia是电流电压转换器。

6.电流传送器有多种用途,其中一种是用在射频(radio frequency,rf)收发器中。直接转换接收器(direct conversion receiver,dcr)可以用在rf收发器中用于接收rf信号。所述dcr使用由本地振荡器驱动的同步检测来解调进入无线电信号,本地振荡器的频率非常接近或等于预期信号的载波频率。在dcr中,将rf馈入混频器,本地振荡器的频率接近所接收的信号的频率,从而产生解调输出。dcr可以包括一个或多个电流传送器。

技术实现要素:

7.根据本公开的一个方面,提供了一种装置,所述装置包括电流传送器,所述电流传送器包括具有第一差分输入的第一级、具有第二差分输入的第二级以及位于所述第一级与所述第二级之间的电流传送器输出端。所述第一级和所述第二级用于以推挽方式操作以在所述电流传送器输出端处提供输出信号。所述装置还包括与所述电流传送器耦合的第一混频器。所述第一混频器用于根据输入信号和具有第一频率的第一振荡器信号产生第一混频器信号。所述第一混频器用于向所述第一差分输入提供所述第一混频器信号。所述装置还包括与所述电流传送器耦合的第二混频器。所述第二混频器用于根据所述输入信号和同样具有所述第一频率的第二振荡器信号产生第二混频器信号。所述第二混频器用于向所述第二差分输入提供所述第二混频器信号。

8.可选地,在前述方面中,所述第一级包括第一公共栅极/基极差分放大器,所述第

一公共栅极/基极差分放大器包括所述第一差分输入和与所述电流传送器输出端连接的第一差分输出。所述第二级包括第二公共栅极/基极差分放大器,所述第二公共栅极/基极差分放大器包括所述第二差分输入和与所述电流传送器输出端连接的第二差分输出。

9.可选地,在任一前述方面中,所述第一公共栅极/基极差分放大器包括一对pmos晶体管,每个pmos晶体管具有栅极和源极。所述一对pmos晶体管的栅极连接在一起。所述第二公共栅极/基极差分放大器包括一对nmos晶体管,每个nmos晶体管具有栅极和源极。所述一对nmos晶体管的栅极连接在一起。

10.可选地,在任一前述方面中,所述一对pmos晶体管的第一构件的源极是所述第一差分输入的正极输入端,所述一对pmos晶体管的第二构件的源极是所述第一差分输入的负极输入端,所述一对nmos晶体管的第一构件的源极为所述第二差分输入的正极输入端,所述一对nmos晶体管的第二构件的源极为所述第二差分输入的负极输入端。

11.可选地,在任一前述方面中,所述第一公共栅极/基极差分放大器包括一对pnp晶体管,每个pnp晶体管具有基极。所述一对pnp晶体管的基极连接在一起。第二公共栅极/基极差分放大器包括一对npn晶体管,每个npn晶体管具有基极。所述一对npn晶体管的基极连接在一起。

12.可选地,在任一前述方面中,所述装置还包括与所述电流传送器输出端和所述第一公共栅极/基极差分放大器耦合的共模电压控制电路。所述共模电压控制电路用于控制电流传送器输出端处的共模电压。

13.可选地,在任一前述方面中,所述第一混频器为第一下混频器,所述第二混频器为第二下混频器。

14.可选地,在任一前述方面中,所述第一混频器包括第一输入端子和第二输入端子,所述第二混频器包括第三输入端子和第四输入端子。所述装置还包括与所述第一输入端子连接的第一信号耦合电容器,以及与所述第二输入端子连接的第二信号耦合电容器。所述第一信号耦合电容器和所述第二信号耦合电容器用于将所述输入信号耦合到所述第一混频器。所述装置还包括与所述第三输入端子连接的第三信号耦合电容器,以及与所述第四输入端子连接的第四信号耦合电容器。所述第三信号耦合电容器和所述第四信号耦合电容器用于将所述输入信号耦合到所述第二混频器。

15.可选地,在任一前述方面中,所述第一级和所述第二级形成ab类放大器。

16.可选地,在任一前述方面中,所述装置还包括组件,所述组件用于向所述第一混频器和所述第二混频器提供所述输入信号,所述输入信号为射频(radio frequency,rf)信号;所述装置还包括低通滤波器,所述低通滤波器与所述电流传送器输出端耦合,所述电流传送器用于向所述低通滤波器提供所述输出信号。

17.可选地,在任一前述方面中,所述第一振荡器信号和所述第二振荡器信号具有相同的相位。

18.根据本公开的另一方面,提供了一种处理输入信号的方法。所述方法包括:向第一混频器提供具有第一频率的第一振荡器信号;向第二混频器提供具有第二频率的第二振荡器信号,所述第二频率与所述第一频率相同。所述方法还包括:根据所述输入信号和所述第一振荡器信号产生第一混频器输出信号;根据所述输入信号和所述第二振荡器信号产生第二混频器输出信号;向电流传送器的第一级的第一差分输入提供所述第一混合器输出信

号;向所述电流传送器的第二级的第二差分输入提供所述第二混频器输出信号;以推挽方式操作所述电流传送器的所述第一级和所述第二级,以从所述电流传送器的电流传送器输出端产生输出信号。

19.可选地,在任一前述方面中,以所述推挽方式操作所述电流传送器的所述第一级和所述第二级以从所述电流传送器产生输出信号包括:将所述第一级和所述第二级用作ab类放大器。

20.可选地,在任一前述方面中,以所述推挽方式操作所述电流传送器的所述第一级和所述第二级以从所述电流传送器产生所述输出信号包括:所述第一级向所述电流传送器输出端提供第一电流,用于输出大于180度但小于360度的输出信号;所述第二级从所述电流传送器输出端中吸收第二电流,用于输出大于180度但小于360度的输出信号。

21.可选地,在任一前述方面中,根据所述输入信号和所述第一振荡器信号产生所述第一混频器输出信号包括根据射频(radio frequency,rf)信号产生第一基带信号;以及根据所述输入信号和所述第二振荡器信号产生所述第二混频器输出信号包括根据所述射频(radiofrequency,rf)信号产生第二基带信号。

22.根据本公开的另一方面,提供了一种射频(radio frequency,rf)接收器,所述射频接收器包括:电流传送器,所述电流传送器包括具有第一极性的第一对晶体管,每个晶体管具有控制端子、输入端端子和输出端端子。所述第一对晶体管的控制端子相互连接。所述电流传送器还包括第二对晶体管,所述第二对晶体管具有与所述第一极性相反的第二极性。所述第二对晶体管中的每一个晶体管都具有控制端子、输入端子和输出端子。所述第二对晶体管的控制端子相互连接。所述第一对晶体管和所述第二对晶体管配置为使得:所述第一对晶体管的第一构件的输出端子和所述第二对晶体管的第一构件的输出端子耦合在一起,所述第一对晶体管的第二构件的输出端子和所述第二对晶体管的第二构件的输出端子耦合在一起。所述rf接收器还包括第一下混频器,所述第一下混频器具有第一射频信号输入端、第一振荡器信号输入端和第一基带信号输出端。所述第一基带信号输出端连接在所述第一对晶体管的输入端子之间。所述rf接收器还包括第二下混频器,所述第二下混频器具有第二射频信号输入端、第二振荡器信号输入端和第二基带信号输出端。所述第二基带信号输出端连接在所述第二对晶体管的输入端子之间。所述rf接收器还包括射频信号电路,所述射频信号电路用于向所述第一射频信号输入端和所述第二射频信号输入端提供相同的射频信号。所述rf接收器还包括电路,所述电路用于向所述第一振荡器信号输入端提供具有第一频率的第一振荡器信号,并向所述第二振荡器信号输入端提供具有与所述第一频率相同的频率的第二振荡器信号。所述第一振荡器信号和所述第二振荡器信号具有相同的相位。所述rf接收器还包括用于输出电流的电流传送器差分输出。所述电流传送器差分输出具有第一节点,所述第一节点与所述第一对晶体管的第一构件的输出端子和所述第二对晶体管的第一构件的输出端子耦合。所述电流传送器差分输出具有第二节点,所述第二节点与所述第一对晶体管的第二构件的输出端子和所述第二对晶体管的第二构件的输出端子耦合。

23.可选地,在任一前述方面中,所述rf接收器还包括一对级联晶体管,其中,所述一对级联晶体管的第一构件耦合在具有所述第一极性的所述第一对晶体管的所述第一构件的所述输出端子与具有所述第二极性的所述第二对晶体管的所述第一构件的所述输出端

子之间,其中,所述一对级联晶体管的第二构件耦合在具有所述第一极性的所述第一对晶体管的所述第二构件的所述输出端子与具有所述第二极性的所述第二对晶体管的所述第二构件的所述输出端子之间。

24.可选地,在任一前述方面中,所述第一对晶体管为pmos晶体管,所述第二对晶体管为nmos晶体管,所述一对级联晶体管为pmos晶体管。

25.可选地,在任一前述方面中,所述第一对晶体管为pmos晶体管,所述第二对晶体管为nmos晶体管,所述一对级联晶体管为nmos晶体管。

26.可选地,在任一前述方面中,所述一对级联晶体管是第一对级联晶体管。所述rf接收器还包括第二对级联晶体管,其中,所述第二对级联晶体管的第一构件耦合在所述第一对级联晶体管的所述第一构件与具有所述第二极性的所述第二对晶体管的所述第一构件的所述输出端子之间,其中,所述第二对级联晶体管的所述第二构件耦合在所述第一对级联晶体管的所述第二构件与具有所述第二极性的所述第二对晶体管的所述第二构件的所述输出端子之间。

27.发明内容简单介绍了一些概念,在具体实施方式中会进一步描述这些概念。发明内容不旨在提供专利申请所要求保护的主题的关键特征或基本特征,也不旨在确定专利申请所要求保护的主题范围。专利申请所要求保护的主题不限于解决背景技术中提到的任何或所有问题的实现方式。

附图说明

28.本公开的各个方面以示例方式说明,并且不受附图的限制,附图中相同的附图标记指示相同的元件。

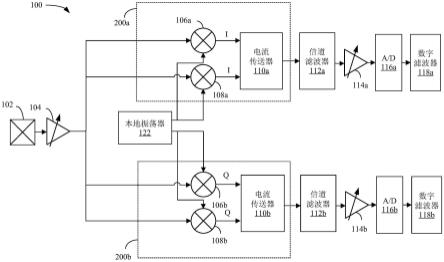

29.图1为直接转换接收器(direct conversion receiver,dcr)的实施例的框图。

30.图2为具有电流传送器和一对混频器的分路混合器电流传送器(split-mixer current conveyer,smcc)电路的一个实施例的框图。

31.图3为smcc电路的一个实施例的示意图。

32.图4为具有一对级联晶体管的smcc电路的一个实施例的示意图。

33.图5为具有两对级联晶体管的smcc电路的一个实施例的示意图。

34.图6a为在第二级中具有一对级联晶体管的smcc电路的一个实施例的示意图。

35.图6b为在第二级中具有一对级联晶体管的smcc电路中的整体连接的一个实施例的示意图。

36.图7为具有混频器和两个信号耦合电容器的电路的一个实施例的示意图。

37.图8为具有共模电压控制电路的smcc电路的示意图。

38.图9为操作smcc电路的过程的一个实施例的流程图。

39.图10为操作dcr中的电流传送器的过程的一个实施例的流程图。

40.图11示出了用户设备的示例细节,可以实现smcc电路的实施例。

41.图12示出了可以包含smcc电路的实施例的示例基站。

42.图13示出了用于传送数据的无线网络。

具体实施方式

43.现在将参考附图描述本公开,附图大体涉及具有电流传送器的电路以及操作电路的方法。在一个实施例中,所述电路用于直接转换接收器中。所述电路的一个实施例具有两个混频器和具有两个差分输入的电流传送器。所述两个混频器处理相同的输入信号(可以是rf信号)。所述两个混频器还接收相同的频率振荡器信号。例如,可以将相同的本地振荡器信号用作两个混频器的振荡器输入。所述两个混频器的输出信号输入到电流传送器的相应差分输入。在一个实施例中,所述两个混频器是下混频器。

44.在具有电流传送器(带有一对混频器)的电路的实施例中,所述电流传送器具有低输入阻抗和高输出阻抗。在一个实施例中,电流传送器将电流从所述一对混频器传递到下游电路。所述下游电路的一个示例是信道滤波器。所述电流传送器防止所述下游电路不期望地加载混频器而干扰所述混频器的操作。

45.电流传送器的实施例在广泛的频率范围内具有良好的线性。需要注意的是,一些电流传送器可以用于同时处理一个频率的期望信号和不同频率的不希望信号的系统中。例如,直接转换接收器可以处理一个频率的期望信号和另一个频率的阻塞信号。此外,所述期望信号可以具有比所述不希望(例如,阻塞)信号小得多的幅值。在一些传统的电流传送器中,当所述电流传送器同时处理期望信号和幅值大于所述期望信号的阻塞信号时,所述期望信号的增益减小。在具有电流传送器(具有一对混频器)的电路的实施例中,所述电流传送器能够同时处理期望信号和幅值大于所述期望信号的阻塞信号,而不会显著降低所述期望信号的增益。

46.具有电流传送器和一对混频器的电路的实施例具有低功耗。当电流传送器正在处理的信号较小时,所述电流传送器可以具有较小的偏置电流。例如,如果没有阻塞信号,或者所述阻塞信号具有较小的幅值,则所述电流传送器可以在较小的偏置电流下有效操作。因此,这节省了功率。当所述电流传送器处理的信号较大时,所述电流传送器可以自动增加其偏置电流,使得可以在不失真或不衰减所需信号的情况下处理较大的信号。例如,如果存在具有所述比期望信号更大幅值的阻塞信号,则所述电流传送器可以增加偏置电流(相对于不存在或更小的阻塞信号)。在一个实施例中,电流传送器包括ab类放大器,其提供高效操作和低功率耗散。

47.具有电流传送器和一对混频器的电路的实施例使用小的管芯面积。在一个实施例中,每对混频器在其信号输入端处具有两个信号耦合电容器。所述信号耦合电容器可以用于将rf信号耦合到混频器的输入端。在一个实施例中,所述信号耦合电容器在所述混频器的高频侧,这允许它们比所述信号耦合电容器在所述混频器的低频侧时更小。更小的信号耦合电容器可以节省管芯面积。

48.应理解,本公开的当前实施例可以以许多不同形式实现,权利要求的范围不应被解释为受限于本文阐述的实施例。相反,提供这些实施例是为了使本公开彻底和完整,并将本发明实施例的概念充分传达给本领域技术人员。事实上,本公开旨在涵盖包括在由所附权利要求书定义的本公开的精神和范围内的这些实施例的替代物、修改和等同物。此外,在本公开的当前实施例的以下详细描述中,阐述了许多具体细节,以便提供透彻的理解。但是,本领域普通技术人员应清楚的是,可以在没有这些具体细节的情况下实践本公开的当前实施例。

49.图1示出了直接转换接收器(direct conversion receiver,dcr)100的一个实施例的框图。所述dcr 100还可以称为零差接收器或零中频(intermediate frequency,if)接收器。所述dcr 100包括两个分路混合器电流传送器(split-mixer current conveyer,smcc)电路(200a、200b),所述电路各自具有电流传送器(110a、110b)。smcc电路200a具有电流传送器110a和两个混频器(106a、108a)。smcc电路200b具有电流传送器110b和两个混频器(106b、108b)。所述电流传送器(110a、110b)能够同时处理期望信号和幅值大于所述比期望信号的阻塞信号,而不会显著降低所述期望信号的增益。在一个实施例中,smcc电路(200a、200b)各自占据小的管芯面积。在一个实施例中,smcc电路(200a、200b)具有低功耗。

50.所述dcr 100使用本地振荡器122驱动的同步检测来解调进入射频(radio frequency,rf)信号。所述本地振荡器122的频率可以非常接近或等于所述期望信号的载波频率。需要注意的是,由于本地振荡器122的频率可以处于或非常接近所述期望信号的载波频率,所以所述本地振荡器122的噪声可以注入到rf信号处理中。所述smcc电路(200a、200b)的实施例能够在没有衰减的情况下让所述期望信号通过,尽管存在这样的噪声。所述本地振荡器122是用于提供振荡器信号的电路的一个示例。需要注意的是,在一个实施例中,所述本地振荡器122提供多个振荡器信号,每个振荡器信号具有相同的频率。如将在下文中更充分地描述的那样,将各种振荡器信号提供到混频器106a、106b、108a、108b。

51.射频(radio frequency,rf)输入端102用于接收rf输入信号。在一个实施例中,所述rf输入端102包括集成电路(integrated circuit,ic)上的输入引脚。作为一例,所述rf输入信号的频率可以是大约2ghz。但是,所述射频信号频率可以高于或低于2ghz。此外,所述rf输入信号可以包含同相(i)分量和正交(q)分量。附加地,所述rf输入端102与低噪声放大器(low noise amplifier,lna)104耦合。在一个实施例中,所述lna 104是可变增益放大器。所述混频器(106a、108a、106b和108b)分离所述rf输入信号的i分量和q分量。所述i分量和所述q分量由相似的组件分别处理。

52.将所述lna(104)的rf输出提供给所述smcc电路200a和所述smcc电路200b。所述smcc电路200a包括两个混频器(106a、108a)以及电流传送器110a,如上所述。所述smcc电路200b包括两个混频器(106b、108b)以及电流传送器110b,如上所述。所述混频器(106a、106b、108a、108b)是图1的实施例中下混频器。所述本地振荡器(122)提供多个振荡器信号,每个振荡器信号具有相同的频率。提供给混频器106a和108a的振荡器信号与提供给混频器106b和108b的振荡器信号相位相差90度。这样,将所述rf信号分成i和q分量。需要注意的是,在本文中,附图标记200可以用于指代smcc电路200a或smcc电路200b。此外,所述smcc电路200不限于处理所述rf信号的i分量或q分量。

53.现在将论述所述i分量信号的处理。需要注意的是,所述q分量信号的处理是类似的,下面将进行简要论述。所述smcc电路200a中的每个混频器106a和108a输入输入rf信号。因此,所述smcc电路200a中的混频器106a和108a各自处理相同的输入信号。所述本地振荡器122向所述smcc电路200a中的每个混频器106a和108a提供振荡器信号。这两个振荡器信号具有相同的频率。在一个实施例中,提供给混频器106a和108a的这两个振荡器信号具有相同的频率和相同的相位。

54.在一个实施例中,每个混频器(106a、108a)是下混频器,用于将相对高频的输入rf信号转换为基带信号。所述混频器106a和108a分别将所述输入rf信号的i分量转换为基带

信号。例如,所述基带信号可以具有从大约180khz到大约20mhz的频率范围。在一个实施例中,所述smcc电路200a中的混频器106a和108a是高线性无源开关低阻抗混频器。

55.所述smcc电路200a还具有电流传送器110a。所述电流传送器110a与信道滤波器112a耦合。在一个实施例中,所述电流传送器110a是具有单位增益的电子放大器。所述电流传送器110a具有两个输入端和一个输出端。在一个实施例中,所述两个输入端均是差分输入。在一个实施例中,所述输出端是差分输出。所述电流传送器110a的每一个输入端接收混频器(106a或108a)中的一个的输出。图2、3、4、5、6a、6b和8示出了可用于实现所述smcc电路200a或200b的若干实施例。

56.所述信道滤波器112a可以是衰减给定频率之上的频率的低通滤波器(low pass filter,lpf)。所述信道滤波器112a与可变增益放大器114a耦合。可变增益放大器(variable gain amplifier,vga)114a与模数转换器(analog-to-digital,a/d)116a耦合。所述a/d 116a与数字滤波器118a耦合。在一个示例中,所述数字滤波器118a在数字信号处理器(digital signal processor,dsp)中实现。

57.可以以与所述rf信号的i分量类似的方式处理所述rf信号的q分量。所述q分量由所述smcc电路200b产生,所述smcc电路200b可以以与所述smcc电路200a类似的方式操作。所述q分量由所述信道滤波器112b、所述可变增益放大器114b、所述a/d 116b和所述数字滤波器118b处理。

58.在一个实施例中,所述lna 104、所述本地振荡器122、所述混频器(106a、106b、108a、108b)、所述电流传送器(110a、110a)、所述信道滤波器(112a、112b)和所述可变增益放大器(114a、114b)集成在单个集成电路上。但是,不需要所述lna 104、所述本地振荡器122、所述混频器(106a、106b、108a、108b)、所述电流传送器(110a、110a)、所述信道滤波器(112a、112b)和所述可变增益放大器(114a、114b)都在同一集成电路上。在一个实施例中,所述本地振荡器122位于与所述smcc电路(200a、200b)不同的集成电路上。在一个实施例中,将所述本地振荡器122的振荡器信号提供给具有smcc电路200a和200b的集成电路。在一个实施例中,包含smcc电路200a和200b的集成电路具有用于向所述混频器(106a、106b、108a、108b)中的每一个提供(或路由)输入振荡器信号的电路。

59.需要注意的是,图1中的dcr 100具有每个信道的单个混频步长。所述smcc电路200的一个实施例也可以用于其它类型的无线电接收器,包括(但不限于)每个信道具有多于一个单一混频步长的那些无线电接收器。例如,超外差接收器可以具有将进入无线信号改变为中频(其可以高于或低于所述进入无线信号的频率)的混频器。在对中频信号进行处理后,所述超外差接收器的混频器可以将处理后的中频信号转换为基带信号。

60.图2是具有电流传送器110和一对混频器(106、108)的smcc电路200的一个实施例的框图。所述smcc电路200可以用于图1的dcr 100中的smcc电路200a或200b。需要注意的是,所述电流传送器110可以用于图1的dcr 100中的电流传送器110a或110b。还需要注意的是,在本文中,当不具体地指代电流传送器110a或110b时,附图标记110用于所述电流传送器110。图2的smcc电路200不限于用于图1的dcr 100中。此外,图2的smcc电路200不限于用于dcr中。例如,所述smcc电路200也可以用于超外差接收器中。

61.所述电流传送器110具有第一级202a和第二级202b。需要注意的是,所述第一级202a也可以称为第一差分级202a,第二级202b也可以称为第二差分级202b。所述第一级

202a具有正极输入端子(input1+)204a和负极输入端子(input1-)206a。在一个实施例中,所述输入端子(204a、206a)一起形成所述第一级202a的差分输入。所述第一级202a具有正极输出端子(output1+)208a和负极输出端子(output1-)210a。在一个实施例中,所述输出端子(208a、210a)一起形成所述第一级202a的差分输出。所述第二级202b具有正极输入端子(input2+)204b和负极输入端子(input2-)206b。在一个实施例中,所述输入端子(204b、206b)一起形成所述第二级202b的差分输入。所述第二级202b具有正极输出端子(output2+)208b和负极输出端子(output2-)210b。在一个实施例中,所述输出端子(208b、210b)一起形成所述第二级202b的差分输出。

62.在一个实施例中,所述第一级202a包括第一公共栅极差分放大器,所述第二级202b包括第二公共栅极差分放大器。公共栅极差分放大器可以包含金属氧化物半导体场效应晶体管(metal oxide semiconductor field effect transistor,mosfet)。所述第一公共栅极差分放大器中的晶体管与所述第二公共栅极差分放大器中的晶体管极性相反。例如,在一个实施例中,所述第一公共栅极差分放大器中的晶体管为nmos,所述第二公共栅极差分放大器中的晶体管为pmos。在另一实施例中,所述第一公共栅极差分放大器中的晶体管为pmos,所述第二公共栅极差分放大器中的晶体管为nmos。需要注意的是,在所述第一公共栅极差分放大器为pmos,所述第二公共栅极差分放大器中的晶体管为nmos的情况下,电压(vpower+和vpower-)的极性可以相反。结合图3、4、5、6a、6b和8示出和描述了所述第一级202a和所述第二级202b包括所述第一公共栅极差分放大器和所述第二公共栅极差分放大器的几个实施例。

63.在一个实施例中,所述第一级202a包括第一公共基极差分放大器,所述第二级202b包括第二公共基极差分放大器。公共基极差分放大器包含双极结晶体管(bipolar junction transistor,bjt)。所述第一公共基极差分放大器中的bjt晶体管与所述第二公共基极差分放大器中的bjt晶体管极性相反。例如,在一个实施例中,所述第一公共基极差分放大器中的bjt晶体管为pnp,所述第二公共基极差分放大器中的bjt晶体管为npn。在另一实施例中,所述第一公共基极差分放大器中的bjt晶体管为npn,所述第二公共基极差分放大器中的bjt晶体管为pnp。

64.在本文中,术语“公共栅极差分放大器/公共基极差分放大器”是指给定级202a或202b中的差分放大器是公共栅极差分放大器,或者替代地,是公共基极差分放大器。在一个实施例中,所述第一级202a和所述第二级202b都是公共栅极或都是公共基极。例如,所述第一级202a包括第一公共栅极差分放大器且所述第二级202b包括第二公共栅极差分放大器,或者替代地,所述第一级202a包括第一公共基差分放大器且所述第二级202b包括第二公共基差分放大器。在一个实施例中,一个级是公共栅极且另一个级是公共基极。例如,所述第一级202a可以包括公共栅极差分放大器且所述第二级202b可以包括公共基极差分放大器,或者替代地,所述第一级202a可以包括公共基极差分放大器且第二级202b可以包括公共栅极差分放大器。此外,所述第一公共栅极/基极差分放大器中的晶体管具有与所述第二公共栅极/基极差分放大器中的晶体管相反的极性(例如,nmos与pmos或npn与pnp)。需要注意的是,mos晶体管的栅极和bjt晶体管的基极都是控制端子的示例。换句话说,本文的术语“控制端子”是指mos晶体管的栅极或bjt晶体管的基极。

65.所述电流传送器110具有电流传送器正极输出端子230a以及电流传送器负极输出

端子230b。在一个实施例中,所述电流传送器输出端子(230a、230b)一起形成所述电流传送器的差分输出。所述电流传送器正极输出端子230a提供v_out+,而所述电流传送器负极输出端子230b提供v_out-。在所述正极输出端子230a处标记电流转换器输出电流i_out+。在所述负极输出端子230b处标记电流转换器输出电流i_out-。在所述smcc电路200用于所述dcr 100的实施例中,所述电流传送器输出端子(230a、230b)与所述信道滤波器112连接。需要注意的是,附图标记112可以用于指代信道滤波器112a或信道滤波器112b。需要注意的是,如果在所述电流传送器输出端子(230a、230b)之间存在电阻性负载,则所述电流传送器110可以称为tia。如本文中所述,tia是接收电流(例如,i_sig)并输出电压(例如,v_out)的放大器。需要注意的是,与所述电流传送器输出端子(230a、230b)连接的组件的输入阻抗可以认为是电阻性负载。例如,在所述smcc电路200用于所述dcr 100的实施例中,所述信道滤波器112的输入阻抗可以认为是所述电流传送器输出端子(230a、230b)处的电阻性负载。

66.需要注意的是,在一个实施例中,所述第一级202a的正极输出端子208a、所述第二级202b的正极输出端子208b以及所述电流传送器正极输出端子230a位于同一节点。同样地,在一个实施例中,所述第一级202a的负极输出端子210a、所述第二级202b的负极输出端子210b以及所述电流传送器负极输出端子230b位于同一节点。需要注意的是,在一个实施例中,v_out+等于所述第一级202a的正极输出端子208a处的电压,并且等于所述第二级202b的正极输出端子208b处的电压。同样地,在一个实施例中,v_out-等于所述第一级202a的负极输出端子210a处的电压,并且等于所述第二级202b的负极输出端子210b处的电压。

67.在pmos晶体管或pnp晶体管的情况下,所述第一差分级202a可以连到接正电源(vpower+)。在nmos晶体管或npn晶体管的情况下,所述第二差分级202b可以与负电源(vpower-)连接。负电源可能接地。

68.所述第一混频器106具有输入端子(212、214),所述输入端子(212、214)用于接收输入信号,并将所述输入信号提供给所述第一混频器106内的电组件。所述输入端子212和所述输入端子214一起接收输入信号(v_sig)。所述输入信号可以是rf信号。所述输入端子212接收v_sig+,而所述输入端子214接收v_sig-。在所述smcc电路200用于所述dcr 100的实施例中,所述lna 104向所述输入端子(212、214)提供v_sig。也就是说,所述lna 104向所述输入端子212提供v_sig+,并且向所述输入端子214提供v_sig-。所述第一混频器106具有振荡器信号输入端子220。可以将振荡器信号提供给所述振荡器信号输入端子220。在一个实施例中,所述本地振荡器122提供所述振荡器信号(参见图1)。

69.所述第一混频器106具有混频器输出端子(232、234)。所述混频器输出端子232与所述第一差分级202a的正极输入端子204a连接。所述混频器输出端子234与所述第一差分级202a的负极输入端子206a连接。所述第一混频器106在所述混频器输出端子(232、234)处产生输出信号(或第一混频器信号),所述输出信号具有的频率取决于所述输入信号v_sig的频率和所述振荡器的信号的频率。在一个实施例中,所述第一混频器106是下混频器。在一个实施例中,所述第一混频器106将所述输入端子(212、214)上接收的rf信号下变频为振荡器信号频率。

70.所述第二混频器108具有输入端子(222、224),所述输入端子(222、224)用于接收输入信号,并将所述输入信号提供给所述第二混频器108中的电组件。所述输入端子222和所述输入端子224一起接收输入信号(v_sig)。需要注意的是,这是提供给所述第一混频器

106的相同信号。所述输入端子222接收v_sig+,而所述输入端子224接收v_sig-。在所述smcc电路200用于所述dcr 100的实施例中,所述lna 104向所述输入端子(222、224)提供v_sig。也就是说,所述lna 104向所述输入端子222提供v_sig+,并且向所述输入端子224提供v_sig-。所述第一混频器108具有振荡器信号输入端子248。可以将振荡器信号提供给所述振荡器信号输入端子248。在一个实施例中,所述本地振荡器122提供所述振荡器信号(参见图1)。需要注意的是,提供给所述第一混频器106和所述第二混频器108的振荡器信号各自具有相同的频率。

71.所述第二混频器108具有混频器输出端子(242、244)。所述混频器输出端子242与所述第二差分级202b的正极输入端子204b连接。所述混频器输出端子244与所述第二差分级202b的负极输入端子206b连接。所述第二混频器108在所述混频器输出端子(242、244)处产生输出信号(或第二混频器信号),所述输出信号具有的频率取决于所述输入信号v_sig的频率和所述振荡器的信号的频率。在一个实施例中,所述第二混频器108是下混频器。在一个实施例中,所述第二混频器108将所述输入端子(222、224)上接收的rf信号下变频为振荡器信号频率。

72.图2中标记了几个电流。所述第一混频器106的混频器输出端子232向所述第一差分级202a的正极输入端子204a提供输入电流i_sig1+。所述第一混频器106的混频器输出端子234向所述第一差分级202a的负极输入端子206a提供输入电流i_sig1-。

73.所述第二混频器108的混频器输出端子242从所述第二差分级202b的正极输入端子204b接收输入电流i_sig2+。所述第二混频器106的混频器输出端子234从所述第二差分级202b的负极输入端子206b接收输入电流i_sig2-。

74.需要注意的是,所述第一级202a和所述第二级202b都能够处理所述输入信号电流(i_sig)。通过处理所述输入信号电流(i_sig),意味着所述级通过在相应的输出端子(例如,230a、230b)处实现电流的变化来响应输入端子(例如204a、204b、206a、206b)处的输入信号电流的幅值的变化。但是,这并不意味着这两个级将必然彼此传导相同幅值的电流。换句话说,在给定时间点,一个级可以传导比另一个级更大的电流。每当电流传送器产生非零输出信号电流时,两个级(202a、202b)输出的电流的幅值可以不同。例如,在一个实施例中,i_sig1+和i_sig2+之间的差值(减去任何损耗)等于230a处的输出电流i_out+。同样地,在一个实施例中,i_sig1-和i_sig2-之间的差值(减去任何损耗)等于230b处的输出电流i_out-。

75.在一个实施例中,所述第一级202a和所述第二级202b以推挽方式操作。通过以推挽方式操作,所述电流传送器110能够处理比所述电流传送器110的静态偏置电流更大的信号电流。例如,所述第一级202a可以向电流传送器输出端子(230a、230b)之间的负载(图2中未描绘)提供电流,并且所述第二级202b可以从所述负载吸收电流。但是,如上所述,这并不意味着这两个级将必然彼此传导相同幅值的电流。在一个实施例中,所述第一级202a向所述电流传送器输出端提供电流,用于输出大于180度但小于360度的输出信号;此外,所述第二级202b可以从所述电流传送器输出端吸收电流,用于输出大于180度但小于360度的输出信号。

76.在一个实施例中,所述电流传送器110用作ab类放大器。通过用作ab类放大器,所述电流传送器110能够处理比所述电流传送器110的静态偏置电流更大的输入信号电流。相

对于所述静态偏置电流需要与待处理的最大输入信号电流一样大的电路,这允许所述电流传送器110使用较小的静态偏置电流。通过能够使用更小的静态偏置电流,电流和功率都得到了节省。

77.在一个实施例中,所述电流传送器110是全差分电流传送器。全差分电流传送器是指具有差分输入和差分输出的电流传送器。所述电流传送器110也可以称为双差分输入/单差分输出电流传送器。

78.图3是smcc电路200的一个实施例的示意图。图3的smcc电路200可以用于图1dcr100中的smcc电路200a或200b。图3的smcc电路200是图2的smcc电路200的一个实施例。在图3的实施例中,所述第一差分级202a和所述第二差分级202b包括公共栅极差分放大器。

79.所述第一差分级202a包括第一pmos晶体管302、第二pmos晶体管304、第一电阻器306和第二电阻器308。所述第一pmos晶体管302的栅极和所述第二pmos晶体管304的栅极连接在一起。可以将偏置电压vp_bias施加到所述第一pmos晶体管302的栅极和所述第二pmos晶体管304的栅极。在一个实施例中,所述第一pmos晶体管302的源极是所述第一级202a的正极输入端子204a。在一个实施例中,所述第二pmos晶体管304的源极是所述第一级202a的负极输入端子206a。所述第一pmos晶体管302的源极和所述第二pmos晶体管304的源极也可以称为输入端子。在一个实施例中,所述第一pmos晶体管302的漏极是所述第一级202a的正极输出端子208a。在一个实施例中,所述第二pmos晶体管304的漏极是所述第一级202a的负极输出端子210b。所述第一pmos晶体管302的漏极和所述第二pmos晶体管304的漏极也可以称为输出端子。所述第一电阻器306连接在所述第一pmos晶体管302的源极与可以施加偏置电压v_bias的端子310之间。所述第二电阻器308连接在所述第二pmos晶体管304的源极与所述可以施加偏置电压v_bias的端子310之间。

80.所述第一电阻器306和所述第二电阻器308的电阻值以及v_bias的幅值和通过所述电阻器(306、308)的静态偏置电流可以用于在所述第一差分输入子(204a、206a)处建立共模工作电压。在一个实施例中,将所述第一电阻器306替换为偏置为电流源的晶体管,将所述第二电阻器308替换为偏置为电流源的晶体管。

81.所述第二差分级202b具有对称配置(相对于所述第一差分级202a),但使用第一nmos晶体管312和第二nmos晶体管314。所述第一nmos晶体管312的栅极和所述第二nmos晶体管314的栅极连接在一起。可以将偏置电压vn_bias施加到所述第一nmos晶体管312的栅极和所述第二nmos晶体管314的栅极。在一个实施例中,通过所述nmos晶体管(312、314)的栅极上的栅极偏置电压(vn_bias)建立所述静态偏置电流。需要注意的是,在所述电流传送器的每个“分支”中可能具有单独的静态偏置电流。例如,一个静态偏置电流可以通过第一电阻器306、第一pmos晶体管302、第一nmos晶体管312和第三电阻器316。另一静态偏置电流可以通过所述第二电阻器308、所述第二pmos晶体管304、所述第二nmos晶体管314和第四电阻器318。需要注意的是,所述电阻器306和所述电阻器308的较大电阻引导较大比例的信号电流电流i_sig+和isig1-通过所述晶体管302和所述晶体管304(与通过所述电阻器(306、308)相反)。

82.在一个实施例中,所述第一nmos晶体管312的源极是所述第二级202b的正极输入端子204b。在一个实施例中,所述第二nmos晶体管314的源极是所述第二级202b的负极输入端子206b。所述第一nmos晶体管312的源极和所述第二nmos晶体管314的源极也可以称为输

入端子。在一个实施例中,所述第一nmos晶体管312的漏极是所述第二级202b的正极输出端子208b。在一个实施例中,所述第二nmos晶体管314的漏极是所述第二级202b的负极输出端子210b。所述第一nmos晶体管312的漏极和第二nmos晶体管314的漏极也可以称为输出端子。所述第三电阻器316连接在所述第一nmos晶体管312的源极与地320之间。所述第四电阻器318连接在所述第二nmos晶体管314的源极与地320之间。

83.所述第三电阻器316和所述第四电阻器318的电阻值可以用于建立所述第二差分输入子(204b、206b)之间的共模工作电压。可以通过所述静态偏置电流以及所述第三电阻器316和所述第四电阻器318的电阻值建立共模工作电压。需要注意的是,图8示出了smcc电路200的一个实施例,所述smcc电路200具有用于在电流传送器输出端处设置共模工作电压的电路元件。需要注意的是,通过使用所述第三电阻器316和第四电阻器318的更大的电阻,可以将更多的信号电流(i_sig2)从所述nmos晶体管(312、314)传递至所述第二混频器108(与通过所述电阻器(316、318)相反)。

84.在一个实施例中,将所述第三电阻器316替换为偏置为电流源的晶体管,将所述第四电阻器318替换为偏置为电流源的晶体管。作为电流源偏置的晶体管可以具有非常高的电阻,这有利于将非常大百分比的信号电流(i_sig2)从所述nmos晶体管(312、314)传递到所述第二混频器108。需要注意的是,如果电流源替代所述电阻器(306、308、316、318),则可以使用类似的方案来建立共模工作电压。在一个实施例中,所述第一级202a的电流源或所述第二级202b中的电流源设置为任意值。然后,将其它电流源设置为一个值,以建立期望的共模输出电压。所述级202a的差分输入的共模电压可以通过所述第一pmos晶体管302的栅极和所述第二pmos晶体管304的栅极上的偏置电压vp_bias建立。所述第二级202b的差分输入的共模电压可以通过所述第一nmos晶体管312的栅极和所述第二nmos晶体管314的栅极上的偏置电压vn_bias建立。

85.对图3的smcc电路200论述现在将进行到混频器(106、108)。所述第一混频器106与第一信号耦合电容器216和第二信号耦合电容器218连接,以允许所述第一混频器106接收所述输入信号v_sig。第一信号耦合电容器216和第二信号耦合电容器218一起接收所述输入信号(v_sig),并将所述输入信号耦合到所述第一混频器106。所述输入信号可以是rf信号的分量。所述第一信号耦合电容器216接收v_sig+,而所述第二信号耦合电容器218接收v_sig-。在所述smcc电路200用于所述dcr 100的实施例中,所述lna 104向第一信号耦合电容器216提供v_sig+,并向第二信号耦合电容器218提供v_sig-。所述第一混频器106接收振荡器信号(osc1)。在一个实施例中,所述本地振荡器122提供所述振荡器信号(参见图1)。所述第一混频器106通过所述振荡器信号(osc1)的频率改变所述输入信号(v_sig)的频率。在一个实施例中,所述第一混频器106是通过所述振荡器信号(osc1)的频率降低所述输入信号(v_sig)的频率的下混频器。在一个实施例中,所述第一混频器106是通过所述振荡器信号(osc1)的频率增加所述输入信号(v_sig)的频率的上混频器。

86.所述第一混频器106向所述第一pmos晶体管302的源极提供电流i_sig1+(在一个实施例中,所述第一pmos晶体管302是所述第一差分级202a的正极输入端子204a)。所述第一混频器106向所述第二pmos晶体管304的源极提供电流i_sig1-(在一个实施例中,所述第二pmos晶体管304是所述第一差分级202a的负极输入端子206a)。需要注意的是,所述第一信号耦合电容器216和所述第二信号耦合电容器218可以认为是所述第一混频器106的一部

分,或者替代地,可以认为是所述第一混频器106的外部构件。

87.所述第二混频器108与第三信号耦合电容器226和第四信号耦合电容器228连接,以允许所述第二混频器108接收所述输入信号v_sig。所述第三信号耦合电容器226和所述第四信号耦合电容器228一起接收所述输入信号(v_sig),并将所述输入信号耦合到所述第二混频器108。需要注意的是,这是提供给与所述第一混频器106连接的所述第一信号耦合电容器216和所述第二信号耦合电容器218的相同的输入信号。所述第三信号耦合电容器226接收v_sig+,而所述第四信号耦合电容器228接收v_sig-。在所述smcc电路200用于所述dcr100的实施例中,所述lna 104向所述第三信号耦合电容器226提供v_sig+,并向所述第四信号耦合电容器228提供v_sig-。所述第二混频器108接收振荡器信号(osc2)。需要注意的是,术语“osc”在同时指代osc1和osc2时,或者在不具体指代osc1或osc2时,可以使用。在一个实施例中,所述本地振荡器122提供所述振荡器信号(参见图1)。需要注意的是,提供给所述第一混频器106的振荡器信号和提供给所述第二混频器108的振荡器信号具有相同的频率。因此,由于所述第一混频器106和所述第二混频器108接收相同的输入信号(v_sig)并具有相同的频率振荡器信号,所以所述第二混频器108输出的信号与所述第一混频器106输出的信号具有相同的频率。在一个实施例中,提供给所述第一混频器106的振荡器信号和提供给所述第二混频器108的振荡器信号具有相同的频率和相同的相位。但是,并不要求相位相同。

88.在一个实施例中,所述第一混频器106和所述第二混频器108均为通过所述振荡器信号(osc)的频率降低所述输入信号(v_sig)的频率的下混频器。在一个实施例中,所述第一混频器106和所述第二混频器108均为通过所述振荡器信号(osc)的频率增加所述输入信号(v_sig)的频率的上混频器。

89.需要注意的是,在一个实施例中,所述第一级202a的第一差分输入的正极输入端子204a处的dc(直流)电压高于所述第二级202b的第二差分输入的正极输入端子204b处的dc电压。同样地,在一个实施例中,所述第一级202a的第一差分输入的负极输入端子206a处的dc电压高于所述第二级202b的第二差分输入的负极输入端子206b处的dc电压。还需要注意的是,所述第一差分输入与所述第一混频器106连接,所述第二差分输入与所述第二混频器108连接。因此,在一个实施例中,所述第一混频器106的输出端处的dc电压高于所述第二混频器108的输出端处的dc电压。但是,所述第一混频器106和所述第二混频器108接收相同的输入信号(v_sig)。在一个实施例中,所述信号耦合电容器(216、218、226、228)阻挡所述输入信号(v_sig)的dc电压电平,以适应在所述电流传送器110的第一差分输入和第二差分输入处的不同dc电压。

90.所述第二混频器108从所述第一nmos晶体管312的源极(在一个实施例中,为所述第二差分级202b的正极输入端子204b)接收电流i_sig2+。所述第二混频器108从所述第二nmos晶体管314的源极(在一个实施例中,为所述第二差分级202b的输入端206b)接收电流i_sig2-。需要注意的是,所述第三信号耦合电容器226和所述第四信号耦合电容器228可以认为是所述第二混频器108的一部分,或者替代地,可以认为是所述第二混频器108的外部构件。

91.需要注意的是,在所述第一混频器106为下混频器的实施例中,所述信号耦合电容器(216、218)位于所述第一混频器106的高频侧。同样地,在所述第二混频器108为下混频器

的实施例中,所述信号耦合电容器(226、228)位于所述第二混频器108的高频侧。所述信号耦合电容器(216、218、226、228)在所述混频器(106、108)的高频侧允许所述信号耦合电容器(216、218、226、228)比放置在所述混频器(106、108)的低频侧时要小。在所述混频器(106、108)的低频侧放置信号耦合电容器的示例是将信号耦合电容器放置在所述混频器(106、108)与所述电流传送器的差分输入之间(假设混频器(106、108)是下混频器)。

92.所述电流传送器110具有位于所述第一pmos晶体管302和所述第一nmos晶体管312之间的电流传送器正极输出端子230a。更具体地,所述电流传送器正极输出端子230a位于所述第一pmos晶体管302的漏极与所述第一nmos晶体管312的漏极之间。在图3的实施例中,所述第一pmos晶体管302的漏极直接与所述第一nmos晶体管312的漏极连接。但是,在所述第一pmos晶体管302的漏极与所述第一nmos晶体管312的漏极之间可以存在一个或多个电路元件。

93.在一些实施例中,所述第一级202a的正极输出端子208a直接与所述第二级202b的正极输出端子208b连接。因此,在一些实施例中,所述电流传送器正极输出端子230a直接与所述第一级202a的正极输出端子208a和所述第二级202b的正极输出端子208b连接。

94.所述电流传送器110具有位于所述第二pmos晶体管304与所述第二nmos晶体管314之间的电流传送器负极输出端子230b。更具体地,所述电流传送器负极输出端子230b位于所述第二pmos晶体管304的漏极与所述第二nmos晶体管314的漏极之间。在图3的实施例中,所述第二pmos晶体管304的漏极直接与所述第二nmos晶体管314的漏极连接。但是,在所述第二pmos晶体管304的漏极与所述第二nmos晶体管314的漏极之间可以存在一个或多个电路元件。

95.在一些实施例中,所述第一级202a的负极输出端子210a直接与所述第二级202b的负极输出端子210b连接。因此,在一些实施例中,所述电流传送器负极输出端子230b直接与所述第一级202a的负极输出端子210a和所述第二级202b的负极输出端子210b连接。

96.需要注意的是,图3的电流传送器110具有低输入阻抗。需要注意的是,图3的电流传送器110具有高输出阻抗。这种情况是因为所述电流传送器110是串联操作的两个公共栅极放大器的组合。在一个实施例中,公共栅极放大器具有输入晶体管的1/gm数量级的低输入阻抗,同时表现出晶体管的输出阻抗数量级的高输出阻抗。

97.通过以推挽方式操作,所述电流传送器110能够处理比所述电流传送器110的静态偏置电流更大的信号电流。例如,通过所述第一电阻器306的静态偏置电流可以小于没有电流传送器削波的输入信号电流(i_sig1+)。同样地,通过所述第二电阻器308的静态偏置电流可以小于没有电流传送器削波的信号电流(i_sig1-)。同样地,通过所述第三电阻器316的静态偏置电流可以小于没有电流传送器削波的信号电流(i_sig2-)。同样地,通过所述第四电阻器318的静态偏置电流可以小于没有电流传送器削波的信号电流(i_sig2-)。因此,相对于所述静态偏置电流需要与待处理的最大输入信号电流一样大的电路,可以使用较小的静态偏置电流。使用更小的静态偏置电流,电流和功率都得到了节省。

98.需要注意的是,图3的smcc电路200的实施例在所述第一级202a或所述第二级202b中均不使用级联晶体管。不使用级联晶体管时,所述smcc电路200可以在较低的电源电压下工作。在一些实施例中,将级联晶体管添加到所述第一级202a和/或所述第二级202b。添加级联晶体管有助于改善所述第一第二差分输入和/或所述第二差分输入与所述电流传送器

输出端之间的隔离度,增加所述电流传送器的输出阻抗,并降低电流传送器输入阻抗对电流传送器负载的依赖性。

99.图4是在所述第一级202a中具有一对级联晶体管的smcc电路200的一个实施例的示意图。所述smcc电路200可以用于图1的dcr 100中。在一个实施例中,具有相同属性(需要注意的是,由于制造过程的限制等原因,可能存在一些差异)的两个smcc电路200用于图1中的smcc 200a和smcc 200b。图4的smcc电路200是图2的smcc电路200的一个实施例。图4的实施例与图3的实施例类似,但是在所述第一差分级202a上增加了一对pmos级联晶体管(402、404)。所述一对pmos级联晶体管(402、404)有助于改善所述第一级202a的第一差分输入与所述电流传送器的差分输出之间的隔离度。

100.所述第一pmos级联晶体管402的栅极与所述第二pmos级联晶体管404的栅极连接。可以将偏置电压vpc_bias施加到所述pmos级联晶体管(402、404)的栅极。所述第一pmos级联晶体管402的源极与所述第一pmos晶体管302的漏极连接。所述第二pmos级联晶体管404的源极与所述第二pmos晶体管304的漏极连接。在一个实施例中,所述第一级202a的正极输出端子208a位于所述第一pmos级联晶体管402的漏极处。在一个实施例中,所述第一级202a的负极输出端子210a位于所述第二pmos级联晶体管404的漏极处。

101.需要注意的是,在图4的实施例中,所述第一级202a的正极输出端子208a、所述第二级202b的正极输出端子208b以及所述电流传送器正极输出端子230a位于同一节点。同样地,在图4的实施例中,所述第一级202a的负极输出端子210a、所述第二级202b的负极输出端子210b以及所述电流传送器负极输出端子230b位于同一节点。换言之,所述第一级202a的正极输出端子208a直接与所述第二级202b的正极输出端子208b连接,所述电流传送器正极输出端子230a位于该接合处。类似地,所述第一级202a的负极输出端子210a直接与所述第二级202b的负极输出端子210b连接,所述电流传送器负极输出端子230b位于该接合处。

102.图5为具有两对级联晶体管的smcc电路200的一个实施例的示意图。图5的smcc电路200可以用于图1的dcr 100中。在一个实施例中,具有相同属性(需要注意的是,由于制造过程的限制等原因,可能存在一些差异)的两个smcc电路200用于图1中的smcc 200a和smcc 200b。图5的smcc电路200是图2的smcc电路200的一个实施例。图5的实施例与图4的实施例类似,但是在所述第二差分级202b上增加了一对nmos级联晶体管(512、514)。所述一对nmos级联晶体管(512、514)有助于提高所述第二级202b的第二差分输入与所述电流传送器的差分输出之间的隔离度,增加所述电流传送器的输出阻抗,并降低所述电流传送器输入阻抗对所述电流传送器负载的依赖性。

103.所述第一nmos级联晶体管512的栅极与所述第二nmos级联晶体管514的栅极连接。可以将偏置电压vnc_bias施加到所述nmos级联晶体管(512、514)的栅极。所述第一nmos级联晶体管512的源极与所述第一nmos晶体管312的漏极连接。所述第二nmos级联晶体管514的源极与所述第二nmos晶体管314的漏极连接。所述第一nmos级联晶体管512的漏极与所述第一pmos级联晶体管402的漏极连接。所述第二nmos级联晶体管514的漏极与所述第二pmos级联晶体管404的漏极连接。

104.在一个实施例中,所述第二级202b的正极输出端子208b位于所述第一nmos级联晶体管512的漏极处。在一个实施例中,所述第二级202b的负极输出端子210b位于所述第二nmos级联晶体管514的漏极处。需要注意的是,在图5的实施例中,所述第一级202a的正极输

出端子208a、所述第二级202b的正极输出端子208b以及所述电流传送器正极输出端子230a位于同一节点。同样地,在图5的实施例中,所述第一级202a的负极输出端子210a、所述第二级202b的负极输出端子210b以及所述电流传送器负极输出端子230b位于同一节点。换言之,所述第一级202a的正极输出端子208a直接与所述第二级202b的正极输出端子208b连接,所述电流传送器正极输出端子230a位于该接合处。类似地,所述第一级202a的负极输出端子210a直接与所述第二级202b的负极输出端子210b连接,所述电流传送器负极输出端子230b位于该接合处。

105.图6a为在第二级中具有一对级联晶体管的smcc电路200的一个实施例的示意图。图6a的smcc电路200可以用于图1的dcr 100中。在一个实施例中,具有相同属性(需要注意的是,由于制造过程的限制等原因,可能存在一些差异)的两个smcc电路200用于图1中的smcc 200a和smcc 200b。图6a的smcc电路200是图2的smcc电路200的一个实施例。图6a的实施例与图5的实施例类似,但是在所述第一差分级202a中不具有一对pmos级联晶体管(402、404)。所述一对nmos级联晶体管(512、514)有助于提高所述第二级202b的第二差分输入与所述电流传送器的差分输出之间的隔离度,增加所述电流传送器的输出阻抗,并降低所述电流传送器输入阻抗对所述电流传送器负载的依赖性。

106.所述第一nmos级联晶体管512的漏极与所述第一pmos晶体管302的漏极连接。所述第二nmos级联晶体管514的漏极与所述第二pmos晶体管304的漏极连接。

107.需要注意的是,在图6a的实施例中,所述第一级202a的正极输出端子208a、所述第二级202b的正极输出端子208b以及所述电流传送器正极输出端子230a位于同一节点。同样地,在图6a的实施例中,所述第一级202a的负极输出端子210a、所述第二级202b的负极输出端子210b以及所述电流传送器负极输出端子230b位于同一节点。换言之,所述第一级202a的正极输出端子208a直接与所述第二级202b的正极输出端子208b连接,所述电流传送器正极输出端子230a位于该接合处。类似地,所述第一级202a的负极输出端子210a直接与所述第二级202b的负极输出端子210b连接,所述电流传送器负极输出端子230b位于该接合处。

108.图6b是在第二级202b中具有一对级联晶体管的smcc电路200中的整体连接的一个实施例的示意图。图6b的smcc电路200可以用于图1中的dcr 100中。在一个实施例中,具有相同属性(需要注意的是,由于制造过程的限制等原因,可能存在一些差异)的两个smcc电路200用于图1中的smcc 200a和smcc 200b。所述第一nmos晶体管312的本体与所述第二nmos晶体管314的源极连接。同样地,所述第二nmos晶体管314的本体与第一nmos晶体管312的源极连接。所述nmos晶体管(312、314)的本体的这种交叉耦合可以降低所述电流传送器的输入阻抗。降低电流传送器的输入阻抗可以改善所述电流传送器的性能。需要注意的是,在pmos侧也可以使用类似的本体交叉耦合。

109.所述第一nmos级联晶体管512的本体与其源极连接。同样地,所述第二nmos级联晶体管514的本体与其源极连接。将所述本体与所述nmos级联晶体管(512、514)的源极连接是可选的,并且所述nmos晶体管(312、314)的本体交叉耦合时不必这样做。

110.图7是具有混频器和两个信号耦合电容器(216、218)的电路700的一个实施例的示意图。所述两个信号耦合电容器(216、218)可以认为是混频器的一部分。但是,为了论述的目的,所述信号耦合电容器(216、218)将论述为与所述混频器的输入端(212、214)连接。将结合所述混频器106的附图标记来描述混频器,但是也可以用于混频器108。

111.所述第一输入端子212与所述信号耦合电容器216连接。所述第二输入端子214与所述信号耦合电容器218连接。所述信号耦合电容器216接收v_sig+,而所述信号耦合电容器218接收v_sig-。所述信号耦合电容器(216、218)将所述输入信号耦合到所述输入端子(212、214)。因此,所述输入端子212和214一起接收所述输入信号(v_sig)。所述输入信号可以是rf信号的分量。

112.振荡器信号正极输入端子220a接收osc+。振荡器信号负极输入端子220b接收osc-。因此,所述振荡器信号正极输入端子220a和所述振荡器信号负极输入端子220b一起接收所述振荡器信号(osc)。在一个实施例中,所述振荡器信号由本地振荡器(图1,122)提供。所述振荡器信号正极输入端子220a与第一振荡器电容器708连接。所述振荡器信号负极输入端子220b与第二振荡器电容器710连接。所述第一振荡器电容器708与第一混频电阻器702连接,可以向所述第一混频电阻器702提供偏置电压vfm_bias1。所述第二振荡器电容器710与第二混频电阻器716连接,可以向所述第二混频电阻器716提供偏置电压vfm_bias2。

113.第一对nmos晶体管(704、706)与所述第一输入端子212连接。更具体地,所述nmos晶体管704的源极与所述第一输入端子212连接,所述nmos晶体管706的源极与所述第一输入端子212连接。所述nmos晶体管704的栅极与所述第一混频电阻器702以及所述第一振荡器电容器708连接。所述nmos晶体管704的漏极与所述混频器正极输出端子232连接。所述nmos晶体管706的漏极与所述混频器负极输出端子234连接。

114.第二对nmos晶体管(712、714)与所述第二输入端子214连接。更具体地,所述nmos晶体管712的源极与所述第二输入端子214连接,所述nmos晶体管714的源极与所述第二输入端子214连接。所述nmos晶体管714的栅极与所述第一混频电阻器702连接。所述nmos晶体管712的漏极与所述混频器正极输出端子232连接。所述nmos晶体管714的漏极与所述混频器负极输出端子234连接。所述nmos晶体管712的栅极与所述nmos晶体管706的栅极连接。所述nmos晶体管712的栅极还与所述第二混频电阻器716以及所述第二振荡器电容器710连接。

115.图8为具有共模电压控制电路的smcc电路的示意图。图8的smcc电路200可以用于图1的dcr 100中。在一个实施例中,具有相同属性(需要注意的是,由于制造过程的限制等原因,可能存在一些差异)的两个smcc电路200用于图1中的smcc 200a和smcc 200b。图8的电流传送器110类似于图5中的电流传送器,但是增加了共模电压控制电路800,所述共模电压控制电路800在电流传送器输出端子(230a、230b)处设置共模电压。所述共模电压控制电路800包括第一共模电阻器804、第二共模电阻器806和运算放大器802。所述第一共模电阻器804连接在所述电流传送器正极输出端子230a与所述运算放大器802的一个输入端之间。该输入端可以是所述运算放大器的不可逆输入端。所述第二共模电阻器806连接在所述电流传送器负极输出端子230b与所述第一共模电阻器804所连接的运算放大器802的同一输入端之间。将参考电压(vref)提供给所述运算放大器802的另一输入端。可以选择vref的幅值以在所述电流传送器输出端子(230a、230b)处建立共模操作电压。例如,vref的值可以是大约v_bias的一半。所述运算放大器802的输出端与所述第一nmos晶体管312的栅极和所述第二nmos晶体管314的栅极连接。

116.需要注意的是,尽管图3、4、5、6a、6b、7和8中描绘的是mosfet,但其它类型的晶体管可用于所述电流传送器110和所述混频器(106、108)中。在一个实施例中,使用bjt代替

mosfet。例如,nmos晶体管可以用npn晶体管代替,pmos晶体管可以用pnp晶体管代替。

117.图9是操作smcc电路的流程900的一个实施例。所述流程900可以用于操作图1、2、3、4、5、6a、6b或8所示出的任一smcc电路200。

118.步骤902包括向第一混频器106和第二混频器108提供振荡器信号。提供给所述第一混频器106的振荡器信号与提供给所述第二混频器108的振荡器信号具有相同的频率。提供给所述第一混频器106的振荡器信号与提供给所述第二混频器108的振荡器信号具有相同的频率和相位。在一个实施例中,所述振荡器信号由本地振荡器(图1,122)提供。作为一个示例,所述本地振荡器122输出振荡器信号(osc),所述振荡器信号输入到所述第一混频器106和所述第二混频器108。

119.步骤904包括向所述第一混频器106和所述第二混频器108提供输入信号。需要注意的是,相同的输入信号输入到所述第一混频器106和所述第二混频器108。在一个实施例中,所述输入信号是rf信号。例如,所述rf信号可以由放大器(例如,lna 104)提供。更一般地,所述输入信号由rf信号电路提供。

120.在一个实施例中,所述第一混频器106和所述第二混频器108都是下混频器。因此,在一个实施例中,所述第一混频器106和所述第二混频器108各自通过所述振荡器的信号的频率降低所述输入信号的频率。需要注意的是,所述第一混频器106和所述第二混频器108将各自输出端具有相同频率的信号。

121.步骤906包括将第一混频器输出信号和第二混频器输出信号提供给所述电流传送器110的相应第一差分输入和第二差分输入。结合图2、3、4、5、6a、6b或8中的任一图,所述第一混频器输出信号可以输入到所述第一级202a的第一差分输入,所述第一级202a具有正极输入端子204a和负极输入端子206a。结合图2、3、4、5、6a、6b或8中的任一图,所述第二混频器输出信号可以输入到所述第二级202b的第二差分输入,所述第二级202b具有正极输入端子204b和负极输入端子206b。

122.步骤908包括从所述电流传送器110输出信号。结合图2、3、4、5、6a、6b或8中任一图,可以从电流传送器输出端输出所述电流传送器输出信号,所述电流传送器输出端包括电流传送器正极输出端子230a和电流传送器负极输出端子230b。

123.步骤908可以包括以推挽方式操作所述电流传送器110的第一级202a和第二级202b以从所述电流传送器产生输出信号。步骤908可以包括将所述电流传送器110的第一级202a和第二级202b用作ab类放大器。

124.图10是操作dcr 100中的电流输送器的流程1000的一个实施例的流程图。所述流程1000可以与在图1中描绘的dcr 100一起使用,但不限于图1的dcr 100。需要注意的是,为了便于说明,这些步骤是按照一定的顺序描述的。

125.步骤1002包括产生第一本地振荡器信号和与所述第一本地振荡器信号相位相差90度的第二本地振荡器信号。所述本地振荡器信号可以由本地振荡器122产生。

126.步骤1004包括将所述第一本地振荡器信号输入i信道下混频器,并将所述第二本地振荡器信号输入q信道下混频器。结合图1的实施例,所述第一本地振荡器信号可以输入到混频器(106a、108a),所述第二本地振荡器信号可以输入到混频器(106b、108b)。

127.步骤1006包括接收rf信号。结合图1,所述rf信号由射频(radio frequency,rf)输入端102接收。所述rf信号可以输入到lna 104。

128.首先论述对所述rf信号的i分量的处理。需要注意的是,对所述rf信号的q分量的处理是类似的。步骤1010a包括将所述rf信号输入第一i信道下混频器以产生第一基带信号。例如,所述rf信号可以输入到混频器106a,所述混频器106a输出对应于所述rf信号的i分量的第一基带信号。

129.步骤1012a包括将所述rf信号输入第二下混频器以产生第二基带信号。例如,所述rf信号可以输入到混频器108a,所述混频器108a输出也对应于所述rf信号的i分量的第二基带信号。需要注意的是,所述混频器106a和所述混频器108a可以各自接收相同的rf信号。

130.步骤1014a包括向i信道电流传送器的第一差分输入提供所述第一基带信号。结合图1,所述第一混频器106a向所述电流传送器110a输出基带信号。结合图2、3、4、5、6a、6b或8中任一图,所述第一混频器106将其输出信号提供给所述第一级202a的第一差分输入,所述第一级202a具有正极输入端子204a和负极输入端子206a。

131.步骤1016a包括向i信道电流传送器的第二差分输入提供第二基带信号。结合图1,所述第二混频器108a向所述电流传送器110a输出基带信号。结合图2、3、4、5、6a、6b或8中任一图,所述第二混频器108将其输出信号提供给所述第二级202b的第二差分输入,所述第二级202b具有正极输入端子204b和负极输入端子206b。

132.步骤1018a包括所述电流传送器为所述i信道提供输出信号(例如,输出电流、输出电压)。结合图1,所述电流传送器110a将其输出信号提供给信道滤波器112a。结合图2、3、4、5、6a、6b或8中任一图,可以从电流传送器输出端输出所述电流传送器输出信号,所述电流传送器输出端包括电流传送器正极输出端子230a和电流传送器负极输出端子230b。

133.对所述q分量的处理可以类似于上面对i分量的描述。步骤1010b包括将所述rf信号输入第一q信道下混频器以产生第一基带信号。例如,所述rf信号可以输入到所述混频器106b,所述混频器106b输出对应于所述rf信号的q分量的第一基带信号。

134.步骤1012b包括将所述rf信号输入第二q信道下混频器以产生第二基带信号。例如,所述rf信号可以输入到所述混频器108b,所述混频器108b输出也对应于所述rf信号的q分量的第二基带信号。需要注意的是,所述混频器106b和所述混频器108b可以各自接收相同的rf信号。

135.步骤1014b包括向q信道电流传送器的第一差分输入提供所述第一基带信号。结合图1,所述第一混频器106b向所述电流传送器110b输出基带信号。结合图2、3、4、5、6a、6b或8中任一图,所述第一混频器106将其输出信号提供给所述第一级202a的第一差分输入,所述第一级202a具有正极输入端子204a和负极输入端子206a。

136.步骤1016b包括向所述q信道电流传送器的第二差分输入提供所述第二基带信号。结合图1,所述第二混频器108b向所述电流传送器110b输出基带信号。结合图2、3、4、5、6a、6b或8中任一图,所述第二混频器108将其输出信号提供给所述第二级202b的第二差分输入,所述第二级202b具有正极输入端子204b和负极输入端子206b。

137.步骤1018b包括所述电流传送器为所述q信道提供输出信号(例如,输出电流、输出电压)。结合图1,所述电流传送器110b将其输出信号提供给信道滤波器112b。结合图2、3、4、5、6a、6b或8中任一图,可以从电流传送器输出端输出所述电流传送器输出信号,所述电流传送器输出端包括电流传送器正极输出端子230a和电流传送器负极输出端子230b。

138.如本文中所述,smcc电路200的实施例可以在接收器中实现,例如但不限于图1的

dcr100。smcc电路200的一个实施例在用户设备(user equipment,ue)中实现,所述用户设备可以用于传输和/或接收无线信号或有线信号。ue可以是任何合适的终端用户设备,可以包括如下设备(或可以称为):用户设备、无线发送/接收单元(ue)、移动台、固定或移动用户单元、寻呼机、蜂窝电话、个人数字助理(personal digital assistant,pda)、智能手机、笔记本电脑、触摸板、无线传感器、可穿戴设备或消费类电子设备。

139.图11示出了ue 1100的示例细节,其可以实现smcc电路200的实施例。所述ue 1100可以例如是移动电话,但可以是其它示例中的其它设备,例如台式计算机、膝上型计算机、平板电脑、手持计算设备、汽车计算设备和/或其它计算设备。如图所示,示例性ue 1100示出为包括至少一个发射器1102、至少一个接收器1104、存储器1106、至少一个处理器1108和至少一个输入/输出设备1112。在一个实施例中,所述接收器1104包含smcc 200。

140.所述处理器1108可以实现所述ue 1100的各种处理操作。例如,所述处理器1108可以执行信号编码、数据处理、功率控制、输入/输出处理或任何其它能够使所述ue 1100在通信系统(如图13的通信系统1300)中操作的功能。所述处理器1108可以包括用于执行一个或多个操作的任何合适的处理或计算设备。例如,所述处理器1108可以包括微处理器、微控制器、数字信号处理器、现场可编程门阵列或专用集成电路。

141.所述发射器1102用于调制数据或其它内容,以通过至少一个天线1110进行发送。发射器1102还可以用于在将rf信号提供给所述天线1110进行发送之前,对这些rf信号进行放大、滤波和变频。所述发射器1102可以包括用于产生用于无线传输的信号的任何合适的结构。

142.接收器1104可以用于将至少一个天线1110所接收的数据或其它内容解调。所述接收器1104还可以用于对通过所述天线1110接收的rf信号进行放大、滤波和变频。所述接收器1104可以包括用于处理无线接收的信号的任何合适的结构。所述天线1110包括用于发送和/或接收无线信号的任何合适的结构。相同的天线1110可以用于发射和接收rf信号,或者替代地,不同的天线1110可以用于发射信号和接收信号。

143.可以理解,一个或多个发射器1102可以用于所述ue 1100中,一个或多个接收器1104可以用于所述ue 1100中,一个或多个天线1110可以用于所述ue 1100中。虽然示出为单独的块或组件,但至少一个发射器1102和至少一个接收器1104可以组合成收发器。因此,本可以示出收发器的单个块,而不是示出图11中的所述发射器1102的单独的块和所述接收器1104的单独的块。

144.所述ue 1100还包括一个或多个输入/输出设备1112。所述输入/输出设备1112便于与用户进行交互。每个输入/输出设备1112包括用于向用户提供信息或从用户接收信息的任何合适的结构,如扬声器、麦克风、小键盘、键盘、显示器或触摸屏。

145.此外,所述ue 1100包括至少一个存储器1106。所述存储器1106存储所述ue 1100使用、生成或收集的指令和数据。例如,所述存储器1106可以存储一个或多个处理器1108执行的软件或固件指令以及用于减少或消除进入信号中的干扰的数据。每个存储器1106包括任何合适的易失性和/或非易失性存储和检索设备。可以使用任何合适类型的存储器,例如随机存取存储器(random access memory,ram)、只读存储器(read-only memory,rom)、硬盘、光盘、用户识别模块(subscriber identity module,sim)卡、记忆棒、安全数字(secure digital,sd)存储卡等。

146.smcc电路200的一个实施例在基站(base station,bs)中实现。基站可以包括若干众所周知的设备中的一个或多个,如基站(base transceiver station,bts)、node-b(nodeb)、演进型nodeb(enb)、下一代(第五代)(5g)nodeb(gnb)、家庭nodeb、家庭enodeb、站点控制器、接入点(access point,ap),或无线路由器,或服务器、路由器、交换机或具有有线网络或无线网络的处理实体。

147.图12示出了可以包含smcc电路200的实施例的示例bs 1200。如图所示,所述bs 1200包括至少一个处理器1208、至少一个发射器1202、至少一个接收器1204、一个或多个天线1210和至少一个存储器1206。所述处理器1208实现所述bs 1200的各种处理操作,例如信号编码、数据处理、功率控制、输入/输出处理或任何其它功能。每个处理器1208包括用于执行一个或多个操作的任何合适的处理或计算设备。例如,每个处理器1208可以包括微处理器、微控制器、数字信号处理器、现场可编程门阵列或专用集成电路。

148.每个发射器1202包括用于产生信号以无线发送到一个或多个ue 1100或其它设备的任何合适的结构。每个接收器1204包括用于处理从一个或多个ue 1100或其它设备无线接收的信号的任何合适的结构。所述接收器1204可以包括smcc电路200。

149.虽然示出为单独的块或组件,但至少一个发射器1202和至少一个接收器1204可以组合成收发器。每个天线1210包括用于发送和/或接收无线信号的任何合适的结构。虽然共用天线1210在这里示出为与发射器1202和接收器1204耦合,但一个或多个天线1210可以与一个或多个发射器1202耦合,一个或多个单独的天线1210可以与一个或多个接收器1204耦合。每个存储器1206包括任何合适的易失性和/或非易失性存储和检索设备。

150.所述ue 1100和/或所述基站1200可以用于无线网络中,以用于传送数据,例如,图13中所示出的通信系统1300。参考图13,例如,所述通信系统1300包括用户设备1100a、1100b和1100c、无线接入网(radio access network,ran)1320a和1320b、核心网1330、公共交换电话网(public switched telephone network,pstn)1340、因特网1350和其它网络1360。其它或替代网络包括私有和公共数据包网络,包括公司内部网。虽然该图中示出了一定数量的这些组件或元件,但是所述系统1300中可以包括任何数量的这些组件或元件。

151.在一个实施例中,所述无线网络可以是第五代(fifth generation,5g)网络,其包括至少一个5g基站,所述5g基站采用正交频分复用(orthogonal frequency-division multiplexing,ofdm)和/或非ofdm以及短于1ms(例如100微秒或200微秒)的传输时间间隔(transmission time interval,tti),以与通信设备进行通信。通常,基站也可以指enb和5g bs(gnb)中的任一个。此外,所述网络还可以包括网络服务器,用于处理通过至少一个enb或gnb从所述通信设备接收的信息。

152.所述系统1300使多个无线用户能够发送和接收数据和其它内容。所述系统1300可以实现一种或多种信道接入方法,例如但不限于码分多址(code division multiple access,cdma)、时分多址(time division multiple access,tdma)、频分多址(frequency division multiple access,fdma)、正交fdma(orthogonal fdma,ofdma)或单载波fdma(single-carrier fdma,sc-fdma)。

153.用户设备(user equipment,ue)1100a、1100b和1100c(可以单独称为ue 1100,或者统称为ue 1100)用于在所述系统1300中操作和/或通信。例如,ue 1100可以用于发送和/或接收无线信号或有线信号。每个ue 1100表示任何合适的终端用户设备,并可以包括如下

设备(或可以称为):用户设备、无线发送/接收单元(ue)、移动台、固定或移动用户单元、寻呼机、蜂窝电话、个人数字助理(personal digital assistant,pda)、智能手机、笔记本电脑、触摸板、无线传感器、可穿戴设备或消费类电子设备。

154.在所描述的实施例中,所述ran 1320a和所述ran 1320b分别包括一个或多个基站(base station,bs)(1200a、1200b)。所述ran 1320a和所述ran 1320b可以单独称为ran 1320,或者统称为ran 1320。类似地,所述基站(base station,bs)1200a和所述基站1200b可以单独称为基站(bs)1200,或者统称为基站(bs)1200。所述bs 1200中的每一个用于与所述ue 1100中的一个或多个进行无线接口,以使得能够接入所述核心网1330、所述pstn 1340、所述互联网1350和/或其它网络1360。例如,所述基站(base stations,bs)1200可以包括若干众所周知的设备中的一个或多个,例如基站(base transceiver station,bts)、node-b(nodeb)、演进型nodeb(enb)、下一代(第五代)(5g)nodeb(gnb)、家庭nodeb、家庭enodeb、站点控制器、接入点(access point,ap),或无线路由器,或服务器、路由器、交换机或具有有线网络或无线网络的处理实体。

155.在一个实施例中,所述bs 1200a构成所述ran 1320a的一部分,所述ran 1320a可以包括一个或多个其它bs 1200、元件和/或设备。类似地,所述bs 1200b构成所述ran 1320b的一部分,所述ran 1320b可以包括一个或多个其它bs 1200、元件和/或设备。每个bs 1200都在特定地理区域(有时称为“小区”)内操作以发送和/或接收无线信号。在一些实施例中,可以采用多输入多输出(multiple-input multiple-output,mimo)技术,每个小区有多个收发器。

156.所述bs 1200使用无线通信链路通过一个或多个空口(未示出)与所述ue 1100中的一个或多个进行通信。所述空口可以利用任何合适的无线接入技术。

157.预期所述系统1300可以使用多个信道接入功能,包括例如其中所述bs 1200和所述ue1100用于实现长期演进无线通信标准(long term evolution,lte)、lte高级(lte advanced,lte-a)和/或lte多媒体广播多播服务(multimedia broadcast multicast service,mbms)的方案。在其它实施例中,所述基站1200和所述用户设备1100a至1100c用于实现umts、hspa或hspa+标准和协议。当然,可以使用其它多接入方案和无线协议。

158.所述ran 1320与所述核心网1330通信,以向所述ue 1100提供语音、数据、应用、基于ip的语音传输(voice over internet protocol,voip)或其它服务。应理解,所述ran 1320和/或所述核心网1330可以与一个或多个其它ran(未示出)直接或间接通信。所述核心网1330还可以用作其它网络(例如pstn 1340、互联网1350和其它网络1360)的网关接入。此外,一些或全部ue 1100可以包括使用不同无线技术和/或协议经由不同无线链路与不同无线网络通信的功能。

159.所述ran 1320还可以包括毫米波和/或微波接入点(access point,ap)。所述ap可以是所述bs 1200的一部分,或者可以位于远离所述bs 1200的位置。所述ap可以包括但不限于连接点(毫米波连接点)或能够进行毫米波通信的bs 1200(例如,毫米波基站)。毫米波ap可以在从24ghz到100ghz等频率范围内发送和接收信号,但不要求在该整个范围内工作。如本文所使用的,术语“基站”用于指基站和/或无线接入点。

160.虽然图13示出了通信系统的一个示例,但是可以对图13进行各种更改。例如,所述通信系统1300可以按任何合适配置包括任何数量的用户设备、基站、网络或其它组件。还应

理解,术语“用户设备”可以指在蜂窝或移动通信系统中与无线网络节点通信的任何类型的无线设备。用户设备的非限制性示例是目标设备、设备到设备(device-to-device,d2d)用户设备、机器类型用户设备或能够进行机器到机器(machine-to-machine,m2m)通信的用户设备、笔记本电脑、pda、ipad、平板电脑、移动端子、智能手机、笔记本电脑嵌入设备(laptop embeddedequipment,lee)、笔记本电脑加载设备(laptop mounted equipment,lme)和usb加密狗。

161.为了本文目的,需要注意的是,图中所描绘的各种特征的尺寸不一定是按比例绘制的。

162.为了本文目的,说明书中可以引用“实施例”、“一个实施例”、“一些实施例”或“另一实施例”来描述不同的实施例或同一实施例。

163.为了本文目的,连接可以是直接连接或间接连接(例如通过一个或多个其它部分)。在某些情况下,当一个元件描述为与另一个元件连接或耦合时,所述元件可以直接与另一个元件连接或通过相关元件间接与另一个元件连接。当一个元件描述为直接与另一个元件连接时,所述元件和另一个元件之间没有相关元件。“通信中”的两个设备是直接或间接连接的,这样它们之间可以进行电子信号的通信。

164.为了本文目的,术语“根据”可理解为“至少部分根据”。

165.为了本文目的,除非另有说明,否则使用“第一”对象、“第二”对象和“第三”对象等数字术语是出于识别目的用于识别不同的对象,而不是意味着对象的排序。

166.为了本文目的,术语“一组”对象可以指一个或多个对象的“一组”。

167.应理解,本主题可以具体体现为许多不同的形式且不应解释为仅限于本文所阐述的实施例。相反,提供这些实施例是为了使本主题彻底和完整,并将本公开充分传达给本领域技术人员。事实上,本主题旨在覆盖包括在由所附权利要求书限定的本主题公开的精神和范围内的这些实施例的替代物、修改和等同物。另外,在以下本主题细描述中,阐述了许多特定细节以便提供对本主题的透彻理解。但是,本领域普通技术人员将清楚到,可以在没有这样具体细节的情况下实践本技术请求保护的主题。

168.呈现对本公开的描述是为了说明和描述,并不旨在按照所公开形式对本公开穷举或限于本公开。在不偏离本公开的范围和精神的情况下,多种修改和变体对本领域技术人员而言是显而易见的。选择和描述本公开的各个方面以便更好地解释本公开的原理和实际应用,并且使本领域普通技术人员能够理解本公开和适合预期特定用途的各种修改。

169.虽然已经以特定于结构特征和/或方法动作的语言描述了主题,但是应理解,所附权利要求书中定义的主题不必局限于上文描述的具体特征或动作。而是,公开上述具体特征和动作作为实现权利要求的示例形式。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1