基于功能重构器件的可编程多功能微波系统及时序控制方法

1.本发明涉及射频微波电路技术领域,尤其是一种基于功能重构器件的可编程多功能微波系统及时序控制方法。

背景技术:

2.由射频微波电路构成的脉冲雷达或脉冲无线通讯系统在军事和民用方面有重要作用,广泛用于5g通信、卫星通信、雷达探测和可移动设备等。传统的射频微波电路实现方法是根据需求先设计单个器件,然后将多个不同功能的器件连接在一起,电路总体积为所有器件体积之和。当系统复杂时,所需要的的器件种类和数量急剧上升,器件种类的增加增大了设计难度,器件数量的增加增大了电路体积,这就导致了电路结构复杂、体积较大、难以实现小型化的问题。传统微波器件的功能在设计时就已经确定下来,功能不可修改,功能的单一性导致了传统微波器件应用范围有限,发生故障后只能用同种器件替换,器件的通用性和可替代性较差。

3.综上所述,现有技术存在以下不足:电路体积较大,由于传统的射频微波电路与系统是将多个不同功能的器件连接在一起,电路系统的整体体积是所有功能器件体积之和,所需功能越多时,电路体积越大;微波系统不可编程,由于传统的微波器件功能单一,无法根据应用场景灵活地改变功能,应用范围较窄,不同功能的器件无法通用,使得射频微波电路模块的通用性和可替代性较差。

技术实现要素:

4.本发明的首要目的在于提供一种实现整体电路小型化、提高器件结构复用率的基于功能重构器件的可编程多功能微波系统。

5.为实现上述目的,本发明采用了以下技术方案:一种基于功能重构器件的可编程多功能微波系统,包括:

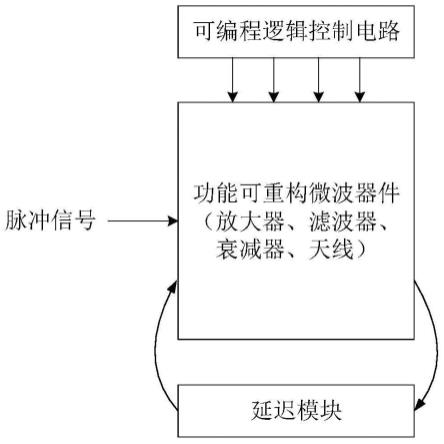

6.功能可重构微波器件,用于在可编程逻辑控制电路的控制下重构出天线、滤波器、功分器和耦合器四种功能;

7.延迟模块,用于延迟和储存脉冲信号;

8.可编程逻辑控制电路,用于控制功能可重构微波器件的功能切换,根据微波系统的需求,发出指令信号使功能可重构微波器件重构出所需的功能;

9.所述功能可重构微波器件由第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管d4、放大器、滤波器、衰减器和天线组成,在可编程逻辑控制电路的控制下,功能可重构微波器件具有放大器、滤波器、衰减器和天线四种微波功能;所述延迟模块连接到功能可重构微波器件的输入输出端口,信号经功能可重构微波器件处理后,输入到延迟模块中,延迟模块起到延迟和储存信号的作用;所述可编程逻辑控制电路用来控制功能可重构微波器件的功能切换和延迟模块的接入与断开,信号在延迟模块储存的同时,功能可重构微波器件在可编程逻辑控制电路的控制下切换到下一个功能,然后信号再由延迟

模块重新输入到功能可重构微波器件,进行下一个功能的信号处理。

10.所述第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管d4的阳极接脉冲信号,第一pin二极管d1的阴极与放大器的输入端相连,第二pin二极管d2的阴极与滤波器的输入端相连,第三pin二极管d3的阴极与衰减器的输入端相连,第四pin二极管d4的阴极接天线。

11.所述可编程逻辑控制电路的输出端分别与第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管d4的阳极相连。

12.所述放大器、滤波器、衰减器的输出端与延迟模块的输入端相连,延迟模块的输出端分别与第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管d4的阳极相连。

13.本发明的另一目的在于提供一种基于功能重构器件的可编程多功能微波系统的时序控制方法,该方法包括:

[0014][0015][0016]

th+t

fd(n)

≤t

f(n)

≤td+t

fd(n)-t

fs(n+1)

[0017][0018][0019]

其中,t

f(n)

为第n个功能的持续时间,t

di

为延迟模块接入功能可重构微波器件输入端的持续时间,t

do

为延迟模块接入功能可重构微波器件输出端的持续时间,td为延迟模块的延迟时间,th为信号周期内脉冲电平持续时间,tk为信号周期内非脉冲电平持续时间,功能可重构微波器件包含n个功能,其中第i个功能处理信号的时间为t

fd(i)

,切换到第i个功能所需的功能切换时间为t

fs(i)

。

[0020]

由上述技术方案可知,本发明的有益效果为:第一,本发明实现了电路小型化:本发明将系统宏观结构由传统的不同功能的多个微波器件串联,变为功能可重构微波器件和延迟模块并联,系统规模由多种微波器件的组合,变为功能可重构微波器件和延迟模块两个器件的组合,功能可重构微波器件和延迟模块体积之和,小于原来不同功能的多个微波器件体积之和,实现了小型化;第二,本发明设计了可编程逻辑控制电路,提高了器件的通用性和可替代性:传统的微波器件功能单一,器件发生故障后只能用同种器件替代,本发明采用功能可重构微波器件,与传统器件相比,功能可重构微波器件在可编程逻辑控制电路控制下,功能可以编程,可以代替多个传统器件进行工作,具有很强的通用性和可替代性。

附图说明

[0021]

图1为传统的微波系统的结构示意图;

[0022]

图2本发明的结构示意图;

[0023]

图3为图1中功能可重构微波器件的结构示意图;

[0024]

图4为本发明实施例的时序逻辑图;

[0025]

图5为本发明实施例中放大器、滤波器和衰减器的信号波形图。

具体实施方式

[0026]

如图2、3所示,一种基于功能重构器件的可编程多功能微波系统,包括:

[0027]

功能可重构微波器件,用于在可编程逻辑控制电路的控制下重构出天线、滤波器、功分器和耦合器四种功能;

[0028]

延迟模块,用于延迟和储存脉冲信号;

[0029]

可编程逻辑控制电路,用于控制功能可重构微波器件的功能切换,根据微波系统的需求,发出指令信号使功能可重构微波器件重构出所需的功能;

[0030]

所述功能可重构微波器件由第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管d4、放大器、滤波器、衰减器和天线组成,在可编程逻辑控制电路的控制下,功能可重构微波器件具有放大器、滤波器、衰减器和天线四种微波功能;所述延迟模块连接到功能可重构微波器件的输入输出端口,信号经功能可重构微波器件处理后,输入到延迟模块中,延迟模块起到延迟和储存信号的作用;所述可编程逻辑控制电路用来控制功能可重构微波器件的功能切换和延迟模块的接入与断开,信号在延迟模块储存的同时,功能可重构微波器件在可编程逻辑控制电路的控制下切换到下一个功能,然后信号再由延迟模块重新输入到功能可重构微波器件,进行下一个功能的信号处理。

[0031]

所述第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管d4的阳极接脉冲信号,第一pin二极管d1的阴极与放大器的输入端相连,第二pin二极管d2的阴极与滤波器的输入端相连,第三pin二极管d3的阴极与衰减器的输入端相连,第四pin二极管d4的阴极接天线。

[0032]

所述可编程逻辑控制电路的输出端分别与第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管d4的阳极相连。

[0033]

所述放大器、滤波器、衰减器的输出端与延迟模块的输入端相连,延迟模块的输出端分别与第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管d4的阳极相连。

[0034]

如图1所示,传统的微波系统实现形式,放大器、滤波器、衰减器和天线依次连接在一起,共同构成微波电路。

[0035]

如图2所示,功能可重构微波器件可以实现放大器、滤波器、衰减器和天线四种微波功能,延迟模块起到延迟和储存信号的作用,可编程逻辑控制电路用来控制功能可重构微波器件的功能切换和延迟模块的接入与断开。

[0036]

如图3所示,利用pin二极管正向偏压时电路导通,反向偏压时电路截止的特性,由可编程逻辑控制电路输出高低电平,控制pin二极管的导通和断开,使微波系统的不同部分工作,进而实现功能可重构。

[0037]

脉冲雷达或脉冲无线通讯系统中,信号周期内脉冲电平持续时间较短,非脉冲电平持续时间较长,在非脉冲电平持续时间内,信号可以多次从功能可重构微波器件中输入输出,功能可重构微波器件分时依次对信号进行处理,相当于4个不同功能的器件分别对信号进行处理。

[0038]

本发明的工作过程如下:

[0039]

可编程逻辑控制电路控制功能可重构微波器件的功能切换和延迟模块的接入与断开,首先第一pin二极管d1导通,放大器工作,功能可重构微波器件切换到放大器功能,原信号输入到功能可重构微波器件中,功能可重构微波器件的放大器对信号进行处理,原信号的波形变为放大器信号的波形,信号经过放大器处理后,输出到延迟模块中,延迟模块可以将信号储存起来,延迟模块储存信号的同时,功能可重构微波器件在可编程逻辑控制电路的控制下,第二pin二极管d2导通,滤波器接入电路,功能可重构微波器件切换到滤波器功能,完成功能切换后,信号从延迟模块输入到功能可重构微波器件中,功能可重构微波器件的滤波器功能对信号进行处理,放大器信号的波形变为滤波器信号的波形,信号经过滤波器处理后,再次输出到延迟模块中,延迟模块储存信号的同时,功能可重构微波器件在可编程逻辑控制电路的控制下,第三pin二极管d3导通,衰减器接入电路,功能可重构微波器件切换到衰减器,完成功能切换后,信号从延迟模块输入到功能可重构微波器件中,功能可重构微波器件的衰减器对信号进行处理,滤波器信号的波形变为衰减器信号的波形,信号经过衰减器处理后,再次输出到延迟模块中,信号在延迟模块中的同时,功能可重构微波器件在可编程逻辑控制电路的控制下,第四pin二极管d4导通,天线接入电路,功能可重构微波器件切换到天线功能,完成功能切换后,信号从延迟模块输入到功能可重构微波器件中,天线工作,信号辐射出去。

[0040]

功能可重构微波器件加延迟模块的体积小于放大器、滤波器、衰减器和天线四个独立器件体积之和,实现了微波电路的小型化。

[0041]

如图4所示,t

f1

是放大器处理信号的时间,t

f2

是滤波器处理信号的时间,t

f3

是衰减器处理信号的时间,t

f4

是天线处理信号的时间。在脉冲信号的一个时间周期内,放大器、滤波器、衰减器和天线分别进行工作,对信号进行处理。

[0042]

如图5所示,功能可重构微波器件按照时间轴的逻辑时序,分别切换到放大器、滤波器、衰减器和天线功能,对信号进行处理,处理后的信号波形随之变化。

[0043]

微波系统时序控制规则如下:

[0044][0045][0046]

th+t

fd(n)

≤t

f(n)

≤td+t

fd(n)-t

fs(n+1)

[0047][0048][0049]

其中,t

f(n)

为第n个功能的持续时间,t

di

为延迟模块接入功能可重构微波器件输入端的持续时间,t

do

为延迟模块接入功能可重构微波器件输出端的持续时间,td为延迟模块的延迟时间,功能可重构微波器件包含n个功能,其中第i个功能处理信号的时间为t

fd(i)

,切换到第i个功能所需的功能切换时间为t

fs(i)

,th为信号周期内脉冲电平持续时间,tk为信号周期内非脉冲电平持续时间。

[0050]

所述延迟模块的延迟时间满足关系:其中,td是延迟模块的延迟时间,t

fs(i)

是切换到第i个功能所需的功能切换时间,th为信号周期内脉冲电平持续时间,tk为信号周期内非脉冲电平持续时间,t

fd(i)

是第i个功能处理信号的时间。

[0051]

设延迟模块的延迟时间为td,其中功能可重构微波器件中第n个功能处理信号的时间为t

fd(n)

,切换到第n个功能所需的时间为t

fs(n)

,设脉冲信号中有效信号的头部为首信号,有效信号的尾部为尾信号。

[0052]

首信号第1次输入功能可重构微波器件的时间为0,此时功能可重构微波器件处于第1个功能,首信号第1次从功能可重构微波器件1输出的时间为t

fd1

;

[0053]

首信号第2次输入功能可重构微波器件的时间为t

fd1

+td,此时功能可重构微波器件处于第2个功能,首信号第2次从功能可重构微波器件输出的时间为t

fd1

+td+t

fd2

;

[0054]

首信号第3次输入功能可重构微波器件的时间为t

fd1

+td+t

fd2

+td,此时功能可重构微波器件处于第3个功能,首信号第3次从功能可重构微波器件输出的时间为t

fd1

+td+t

fd2

+td+t

fd3

;

[0055]

……

[0056]

以此类推,首信号第n-1次输入功能可重构微波器件的时间为:(n-2)td+[t

fd1

+t

fd2

+

…

+t

fd(n-2)

],此时功能可重构微波器件处于第n-1个功能,首信号第n-1次从功能可重构微波器件输出的时间为:(n-2)td+[t

fd1

+t

fd2

+

…

+t

fd(n-1)

];

[0057]

首信号第n次输入功能可重构微波器件的时间为:(n-1)td+[t

fd1

+t

fd2

+

…

+t

fd(n-1)

],此时功能可重构微波器件处于第n个功能,首信号第n次从功能可重构微波器件输出的时间为:(n-1)td+[t

fd1

+t

fd2

+

…

+t

fd(n)

]。

[0058]

尾信号第1次输入功能可重构微波器件的时间为th,尾信号第1次从功能可重构微波器件输出的时间为th+t

fd1

;

[0059]

尾信号第2次输入功能可重构微波器件的时间为th+t

fd1

+td,尾信号第2次从功能可重构微波器件输出的时间为th+t

fd1

+td+t

fd2

;

[0060]

尾信号第3次输入功能可重构微波器件的时间为th+t

fd1

+td+t

fd2

+td,尾信号第3次从功能可重构微波器件输出的时间为th+t

fd1

+td+t

fd2

+td+t

fd3

;

[0061]

……

[0062]

以此类推,尾信号第n-1次输入功能可重构微波器件的时间为:th+(n-2)td+[t

fd1

+t

fd2

+

…

+t

fd(n-2)

],尾信号第n-1次从功能可重构微波器件输出的时间为:th+(n-2)td+[t

fd1

+t

fd2

+

…

+t

fd(n-1)

];

[0063]

尾信号第n次输入功能可重构微波器件的时间为:th+(n-1)td+[t

fd1

+t

fd2

+

…

+t

fd(n-1)

],尾信号第n次从功能可重构微波器件输出的时间为:th+(n-1)td+[t

fd1

+t

fd2

+

…

+t

fd(n)

]。

[0064]

为了使器件正常工作,当尾信号从功能可重构微波器件输出后,需要将器件切换到下一个功能,然后首信号才能再次输入到功能可重构微波器件,所以

[0065]

首信号第n次输入》尾信号第n-1次输出+第n个功能切换时间

[0066]

(n-1)td+[t

fd1

+t

fd2

+

…

+t

fd(n-1)

]

[0067]

》th+(n-2)td+[t

fd1

+t

fd2

+

…

+t

fd(n-1)

]+t

fs(n)

[0068]

td》th+t

fs(n)

[0069][0070]

为了使器件正常工作,当尾信号第n次输出后,器件需要复位,所以

[0071]

th+tk》th+(n-1)td+[t

fd1

+t

fd2

+

…

+t

fd(n)

]+t

fs1

[0072]

tk》(n-1)td+[t

fd1

+t

fd2

+

…

+t

fd(n)

]+t

fs1

[0073][0074]

为了使器件正常工作,在首信号第n次输入到尾信号第n次输出的这段时间,应使功能可重构微波器件处于第n个功能,因此功能可重构微波器件第n个功能的最短持续时间应满足:

[0075]

第n个功能的最短持续时间=尾信号第n次输出-首信号第n次输入

[0076]

min[t

f(n)

]=th+(n-1)td+[t

fd1

+t

fd2

+

…

+t

fd(n)

]-(n-1)td[0077]-[t

fd1

+t

fd2

+

…

+t

fd(n-1)

]

[0078]

min[t

f(n)

]=th+t

fd(n)

[0079]

考虑到实际情况,功能可重构微波器件可适当提前或延后打开功能,功能可重构微波器件第n个功能的最长持续时间应满足第n个功能的最长持续时间=首信号第n+1次输入-t

fs(n+1)-首信号第n次输入

[0080]

max[t

f(n)

]=n

·

td+[t

fd1

+t

fd2

+

…

+t

fd(n)

]-t

fs(n+1)-(n-1)td[0081]-[t

fd1

+t

fd2

+

…

+t

fd(n-1)

]

[0082]

max[t

f(n)

]=td+t

fd(n)-t

fs(n+1)

[0083]

所以,功能可重构微波器件第n个功能的持续时间t

f(n)

应满足:

[0084]

th+t

fd(n)

≤t

f(n)

≤td+t

fd(n)-t

fs(n+1)

[0085]

为了使器件正常工作,应保证延迟模块接入功能可重构微波器件输入输出端的时间不与信号处理的时间矛盾。

[0086]

延迟模块接入功能可重构微波器件输入端最短持续时间min(t

di

)为

[0087]

min(t

di

)=尾信号第n次输入-首信号第2次输入

[0088]

min(t

di

)=th+(n-1)td+[t

fd1

+t

fd2

+

…

+t

fd(n-1)

]-t

fd1-td[0089][0090]

延迟模块接入功能可重构微波器件输入端最长持续时间max(t

di

)为:

[0091]

max(t

di

)=th+t

k-尾信号第1次输入

[0092]

max(t

di

)=tk[0093]

所以,延迟模块接入功能可重构微波器件输入端持续时间t

di

应满足:

[0094][0095]

延迟模块接入功能可重构微波器件输出端最短持续时间min(t

do

)为:

[0096]

min(t

do

)=尾信号第n-1次输出-首信号第1次输出

[0097]

min(t

do

)=th+(n-2)td+[t

fd1

+t

fd2

+

…

+t

fd(n-1)

]-t

fd1

[0098][0099]

延迟模块接入功能可重构微波器件输出端最长持续时间max(t

do

)为:

[0100]

max(t

do

)=首信号第n次输出-首信号第1次输入

[0101]

max(t

do

)=(n-1)td+[t

fd1

+t

fd2

+

…

+t

fd(n)

]

[0102][0103]

所以,延迟模块接入功能可重构微波器件输出端持续时间t

do

应满足:

[0104][0105]

综上所述,本发明设计的可编程微波系统基于功能可重构微波器件,将传统电路大小由多个器件体积之和减小为功能可重构微波器件和延迟模块的体积之和,实现了小型化,功能可重构微波器件和延迟模块在可编程逻辑控制电路的控制下,实现可编程微波系统。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1