一种应用于高速运放的动态摆率增强电路的制作方法

1.本发明属于运算放大器领域,具体属于一种应用于高速运放的动态摆率增强电路。

背景技术:

2.集成电路产业是信息技术产业的核心,是支撑经济社会发展和保障国家安全的战略性、基础性和先导性产业。

3.随着电子技术的飞速发展,运算放大电路也得到广泛的应用,其中驱动器类高速放大器能够为后续adc或负载提供摆幅较大的高速信号,应用十分广泛。然而,其大信号带宽往往受到摆率的限制而无法提升,因此提升高速运放的摆率十分有必要。

技术实现要素:

4.为了解决现有技术中存在的问题,本发明提供一种应用于高速运放的动态摆率增强电路,能够提升运放的速率,尤其是在大信号输入情况下能够极大地提升运放的摆率。

5.为实现上述目的,本发明提供如下技术方案:

6.一种应用于高速运放的动态摆率增强电路,包括pnp三极管q1、pnp三极管q2、npn三极管q3、npn三极管q4、npn三极管q5、npn三极管 q6、pnp三极管q7、pnp三极管q8、pnp三极管q9、pnp三极管q10、 pnp三极管q11、电容c1、电容c2和电阻r1;

7.所述pnp三极管q1的基极与差分正输入端vip和电容c1的一端相连接,pnp三极管q1的集电极与gnd相连,pnp三极管q1的发射极与npn三极管q3的发射极相连接;

8.所述pnp三极管q2的基极与差分负输入端vin和电容c2的一端相连接, pnp三极管q2的集电极与gnd相连,pnp三极管q2的发射极与npn三极管q4的发射极相连接;

9.所述npn三极管q3的基极与npn三极管q3的集电极、电容c1的另一端、pnp三极管q9的集电极、npn三极管q5的基极相连接;

10.所述npn三极管q4的基极与npn三极管q4的集电极、电容c2的另一端、pnp三极管q10的集电极、npn三极管q6的基极相连接;

11.所述pnp三极管q9的基极与pnp三极管q10的基极、pnp三极管q11 的基极、pnp三极管q11的集电极、npn三极管q5的集电极、npn三极管 q6的集电极相连;

12.所述pnp三极管q9的发射极与vdd相连;pnp三极管q10的发射极与vdd相连;pnp三极管q11的发射极与vdd相连;npn三极管q5的发射极与npn三极管q6的发射极、电阻r1的一端相连;pnp三极管q7的发射极与pnp三极管q8的发射极、电阻r1的另一端相连,pnp三极管q7的基极与差分正输入端vip相连,pnp三极管q7的集电极与后续电路相连;pnp 三极管q8的基极与差分正输入端vin相连,pnp三极管q8的集电极与后续电路相连。

13.优选的,所述npn三极管q3、npn三极管q4、npn三极管q5和npn 三极管q6的版图面积相等。

14.优选的,所述pnp三极管q7和pnp三极管q8的版图面积相等,并且为pnp三极管q1和

pnp三极管q2版图面积的大于1的正整数倍。

15.优选的,所述pnp三极管q11的版图面积为2倍的pnp三极管q9和2 倍的pnp三极管q10。

16.优选的,所述后续电路为折叠共源共栅结构或套筒式放大器结构。

17.一种应用于高速运放的动态摆率增强电路,包括pmos管q1、pmos管 q2、nmos管q3、nmos管q4、nmos管q5、nmos管q6、pmos管 q7、pmos管q8、pmos管q9、pmos管q10、pmos管q11、电容c1、电容c2和电阻r1;

18.所述pmos管q1的栅极与差分正输入端vip和电容c1的一端相连接, pmos管q1的漏极与gnd相连,pmos管q1的源极与nmos管q3的源极相连接;

19.所述pmos管q2的栅极与差分负输入端vin和电容c2的一端相连接, pmos管q2的漏极与gnd相连,pmos管q2的源极与nmos管q4的源极相连接;

20.所述nmos管q3的栅极与nmos管q3的漏极、电容c1的另一端、 pmos管q9的漏极、nmos管q5的栅极相连接;

21.所述nmos管q4的栅极与nmos管q4的漏极、电容c2的另一端、 pmos管q10的漏极、nmos管q6的栅极相连接;

22.所述pmos管q9的栅极与pmos管q10的栅极、pmos管q11的栅极、pmos管q11的漏极、nmos管q5的漏极、nmos管q6的漏极相连;

23.所述pmos管q9的源极与vdd相连;pmos管q10的源极与vdd相连;pmos管q11的源极与vdd相连;nmos管q5的源极与nmos管q6 的源极、电阻r1的一端相连;pmos管q7的源极与pmos管q8的源极、电阻r1的另一端相连,pmos管q7的栅极与差分正输入端vip相连,pmos 管q7的漏极与后续电路相连;pmos管q8的栅极与差分正输入端vin相连, pmos管q8的漏极与后续电路相连。

24.优选的,所述nmos管q3、nmos管q4、nmos管q5和nmos管 q6的版图面积相等。

25.优选的,所述pmos管q7和pmos管q8的版图面积相等,并且为pmos 管q1和pmos管q2版图面积的大于1的正整数倍。

26.优选的,所述pmos管q11的版图面积为2倍的pmos管q9和2倍的 pmos管q10。

27.优选的,所述后续电路为折叠共源共栅结构或套筒式放大器结构。

28.与现有技术相比,本发明具有以下有益的技术效果:

29.本发明提供一种应用于高速运放的动态摆率增强电路,该电路能够使运放输入级的尾电流随输入差分信号的差值增大而增大,从而提升运放的速率,尤其是在大信号输入情况下能够极大地提升运放的摆率。pnp三极管q11的电流i会显著增大,从而增加信号响应速度,尤其是提升摆率。电路中的静态电流由设计决定,不会出现无工作点的状态,且静态电流值可以设计的较低。增加了电容c1和电容c2来耦合大信号,其电容值根据设计者对带宽和速率的要求决定。

30.进一步的,通过限定版图匹配时三极管基极面积都是整数倍关系,这样可以提升版图匹配度。

附图说明

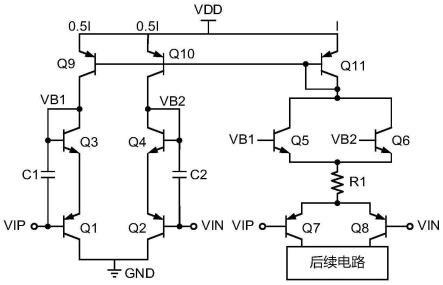

31.图1为本发明一种应用于高速运放的动态摆率增强电路原理图。

具体实施方式

32.下面结合具体的实施例对本发明做进一步的详细说明,所述是对本发明的解释而不是限定。

33.一种应用于高速运放的动态摆率增强电路,该电路包含7个pnp三极管, 4个npn三极管,2个电容,1个电阻。该电路能够使运放输入级的尾电流随输入差分信号的差值增大而增大,从而提升运放的速率,尤其是在大信号输入情况下能够极大地提升运放的摆率。

34.如图1所示,该电路包含7个pnp三极管,4个npn三极管,2个电容, 1个电阻。pnp三极管q1的基极与差分正输入端vip和电容c1的一端相连, pnp三极管q1的集电极与gnd相连,pnp三极管q1的发射极与npn三极管q3的发射极相连;pnp三极管q2的基极与差分负输入端vin和电容c2的一端相连,pnp三极管q2的集电极与gnd相连,pnp三极管q2的发射极与npn三极管q4的发射极相连;npn三极管q3的基极与npn三极管q3的集电极、电容c1的另一端、pnp三极管q9的集电极、npn三极管q5的基极相连(该连线图中命名为vb1)相连;npn三极管q4的基极与 npn三极管q4的集电极、电容c2的另一端、pnp三极管q10的集电极、 npn三极管q6的基极相连(该连线图中命名为vb2)相连;pnp三极管q9 的基极与pnp三极管q10的基极、pnp三极管q11的基极、pnp三极管 q11的集电极、npn三极管q5的集电极、npn三极管q6的集电极相连; pnp三极管q9的发射极与vdd相连;pnp三极管q10的发射极与vdd相连;pnp三极管q11的发射极与vdd相连;npn三极管q5的发射极与npn 三极管q6的发射极、电阻r1的一端相连;pnp三极管q7的发射极与pnp 三极管q8的发射极、电阻r1的另一端相连,pnp三极管q7的基极与差分正输入端vip相连,pnp三极管q7的集电极与后续电路相连;pnp三极管 q8的基极与差分正输入端vin相连,pnp三极管q8的集电极与后续电路相连。其中pnp三极管q9,q10,q11为电流镜结构,为方便理解所以在图中画出了具体的器件类型,其也可替换为带源级负反馈的电流镜、mos结构电流镜等结构,并不影响本专利的核心内容,在本发明中未对这些组合的情况进行穷举行的描述仅仅是处于省略篇幅和节约资源的考虑。因此,本发明并不局限于文中公开的特定实施例,这些组合也包含在权利要求内。

35.后续电路可以是折叠共源共栅结构,也可以是套筒式放大器结构,为和该专利技术相配合,建议后续电路的偏置电流也由pnp三极管q11产生。

36.图1中所示的三极管基极的版图面积具有如下的比例关系: q3=q4=q5=q6,q7=q8=n*q1=n*q2,q11=2*q9=2*q10。其中n为大于1 的正整数,可以自行设计,其与尾电流静态值相关,是三极管的电流的关键参数,可以理解为mos管的宽长比。版图匹配时三极管基极面积都是整数倍关系,这样可以提升版图匹配度。通过限定一定的倍数关系可以决定偏置电流的大小,pnp三极管q11的电流表达式与该比值有关。

37.在输入共模情况下,vip=vin=vcm,pnp三极管q11的电流i= (vbe2+vbe4-vbe5-vbe7)/r1=vt*lnn/r1,因此静态电流可以根据设计n 和r1的值来决定;在出现差分输出信号时,假设vip》vin,pnp三极管q11 的电流i=(vip+vbe2+vbe4-vbe5-vbe7-vin)/r1=(vip-vin+vt*lnn)/r1,由于vt*lnn一般不超过100mv,因此此时pnp三极管q11的电流i会显著增大,从而增加信号响应速度,尤其是提升摆率。

38.需要注意的是,由于pnp三极管q9,pnp三极管q10电流有限,当大信号变化迅速时,vb1和vb2响应有可能跟不上,因此增加了电容c1和电容 c2来耦合大信号,其电容值根据设计者对带宽和速率的要求决定。

39.此电路可能存在简并工作点,pnp三极管q9、pnp三极管q10、pnp 三极管q11存在无电流状态,设计者可以为pnp三极管q11增加一股弱下拉电流来解决此问题。

40.由于高速运放往往是由三极管实现的,因此本专利实施例采用三极管来说明,电路原理图中的三极管也可换为mos管,不影响摆率增强的基本原理。

41.本发明的一种应用于高速运放的动态摆率增强电路,包括pmos管q1、 pmos管q2、nmos管q3、nmos管q4、nmos管q5、nmos管q6、 pmos管q7、pmos管q8、pmos管q9、pmos管q10、pmos管q11、电容c1、电容c2和电阻r1。

42.pmos管q1的栅极与差分正输入端vip和电容c1的一端相连接,pmos 管q1的漏极与gnd相连,pmos管q1的源极与nmos管q3的源极相连接。

43.pmos管q2的栅极与差分负输入端vin和电容c2的一端相连接,pmos 管q2的漏极与gnd相连,pmos管q2的源极与nmos管q4的源极相连接。

44.nmos管q3的栅极与nmos管q3的漏极、电容c1的另一端、pmos 管q9的漏极、nmos管q5的栅极相连接。

45.nmos管q4的栅极与nmos管q4的漏极、电容c2的另一端、pmos 管q10的漏极、nmos管q6的栅极相连接。

46.pmos管q9的栅极与pmos管q10的栅极、pmos管q11的栅极、pmos 管q11的漏极、nmos管q5的漏极、nmos管q6的漏极相连。

47.pmos管q9的源极与vdd相连;pmos管q10的源极与vdd相连; pmos管q11的源极与vdd相连;nmos管q5的源极与nmos管q6的源极、电阻r1的一端相连;pmos管q7的源极与pmos管q8的源极、电阻 r1的另一端相连,pmos管q7的栅极与差分正输入端vip相连,pmos管 q7的漏极与后续电路相连;pmos管q8的栅极与差分正输入端vin相连, pmos管q8的漏极与后续电路相连。

48.本发明为高速运放提供动态摆率增强能力,使尾电流随输入信号增大而增大。静态电流由设计决定,不会出现无工作点的状态,且静态电流值可以设计的较低。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1