布线电路基板和其制造方法与流程

1.本发明涉及布线电路基板和其制造方法。

背景技术:

2.公知有一种具备多孔质绝缘树脂薄膜和导电层的布线电路基板(例如参照下述专利文献1。)。在专利文献1所记载的布线电路基板中,导电层具有多个布线。在专利文献1中,多个布线部的厚度相同。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2019-123851号公报

技术实现要素:

6.发明要解决的问题

7.根据用途和目的,有时在厚度方向上对布线电路基板进行按压。在该情况下,多孔质绝缘树脂薄膜中的与多个布线部重叠的多个部分因按压而厚度统一地变动。那样一来,存在多个布线中的各布线的电特性统一地变动这样的不良。

8.本发明提供与第2布线部的电特性的变动相比能够抑制第1布线部的电特性的变动的布线电路基板和其制造方法。

9.用于解决问题的方案

10.本发明(1)包含一种布线电路基板,其中,该布线电路基板朝向厚度方向上的一侧依次具备多孔质绝缘层和导体层,所述导体层具有第1布线部和比所述第1布线部厚的第2布线部。

11.在该布线电路基板中,第2布线部比第1布线部厚。换言之,第1布线部比第2布线部薄。

12.因此,当在厚度方向上对布线电路基板进行按压时,同多孔质绝缘层的在厚度方向上与第2布线部重叠的部分相比,多孔质绝缘层的在厚度方向上与第1布线部重叠的部分承受较小的按压压力。因此,同多孔质绝缘层的在厚度方向上与第2布线部重叠的部分的厚度的变动相比,能够抑制多孔质绝缘层的在厚度方向上与第1布线部重叠的部分的厚度的变动。

13.其结果,与第2布线部的电特性的变动相比,能够抑制第1布线部的电特性的变动。

14.本发明(2)包含(1)所述的布线电路基板,其中,所述第2布线部在与所述厚度方向正交的方向上相互隔开间隔地配置有两个,所述第1布线部配置在两个所述第2布线部之间。

15.在该布线电路基板中,在按压时,多孔质绝缘层的在厚度方向上与两个第2布线部重叠的部分能够均衡地承受较大的按压压力。因此,多孔质绝缘层的与配置在两个第2布线部之间的第1布线部重叠的部分承受更小的按压压力。因此,同多孔质绝缘层的在厚度方向

上与第2布线部重叠的部分的厚度的变动相比,能够进一步抑制多孔质绝缘层的在厚度方向上与第1布线部重叠的部分的厚度的变动。

16.本发明(3)包含(1)或(2)所述的布线电路基板,其中,该布线电路基板还具备配置于所述多孔质绝缘层的厚度方向上的另一侧的面的接地层,所述接地层具有在沿厚度方向投影时与所述第1布线部重叠的第3布线部和与所述第2布线部重叠的第4布线部,所述第4布线部比所述第3布线部厚。

17.在该布线电路基板中,由于接地层具有与第1布线部重叠的第3布线部和与第2布线部重叠且比第3布线部厚的第4布线部,因此,当在厚度方向上对布线电路基板进行按压时,同多孔质绝缘层的在厚度方向上与第2布线部重叠的部分相比,多孔质绝缘层的在厚度方向上与第1布线部重叠的部分承受更小的按压压力。因此,同多孔质绝缘层的在厚度方向上与第2布线部重叠的部分的厚度的变动相比,能够进一步抑制多孔质绝缘层的在厚度方向上与第1布线部重叠的部分的厚度的变动。

18.本发明(4)包含(3)所述的布线电路基板,其中,所述多孔质绝缘层具有在厚度方向上贯通所述多孔质绝缘层的通孔,该布线电路基板还具备导体连接部,该导体连接部填充于所述通孔且与所述导体层和所述接地层接触。

19.本发明(5)包含(1)至(4)中任一项所述的布线电路基板,其中,该布线电路基板还具备粘接层和覆盖绝缘层,所述覆盖绝缘层隔着所述粘接层从厚度方向上的一侧覆盖所述导体层和所述多孔质绝缘层。

20.本发明(6)包含一种布线电路基板的制造方法,其中,该布线电路基板的制造方法具备:第1工序,在该第1工序中,将具有第1布线部和比所述第1布线部厚的第2布线部的导体层配置于多孔质绝缘层的厚度方向上的一侧的面;以及第2工序,在该第2工序中,将覆盖绝缘层隔着粘接层压于所述导体层和所述多孔质绝缘层。

21.在该制造方法中,在第2工序中,即使将覆盖绝缘层隔着粘接层压于导体层和多孔质绝缘层而对多孔质绝缘层作用有较大的按压压力,同多孔质绝缘层的在厚度方向上与第2布线部重叠的部分的厚度的变动相比,也能够抑制多孔质绝缘层的在厚度方向上与第1布线部重叠的部分的厚度的变动。其结果,与第2布线部的电特性的变动相比,能够抑制第1布线部的电特性的变动。

22.发明的效果

23.根据本发明的布线电路基板和其制造方法,与第2布线部的电特性的变动相比,能够抑制第1布线部的电特性的变动。

附图说明

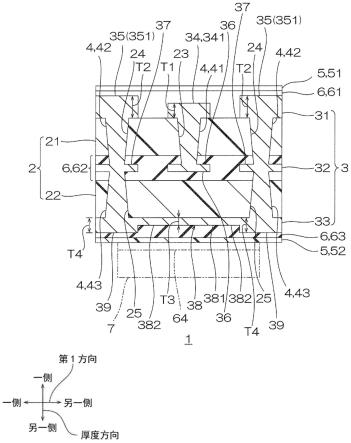

24.图1表示出本发明的一个实施方式的剖视图。

25.图2a~图2d是图1所示的布线电路基板的制造工序图。图2a是准备第1多孔质层叠体的工序。图2b是形成第1导通部的工序。图2c是形成第1镀层的工序。图2d是图案形成第2导体层的工序。

26.图3a~图3c是接续于图2d的布线电路基板的制造工序图。图3a是将第2多孔质层叠体贴合于第2导体层的工序。图3b是形成第2导通部和第3导通部的工序。图3c是形成第2镀层的工序。

27.图4a~图4b是接续于图3c的布线电路基板的制造工序图。图4a是图案形成第1镀层和第1基底层的工序。图4b是将第1覆盖层叠体和第2覆盖层叠体贴合起来的工序。

28.图5是布线电路基板的变形例的剖视图。

29.图6是布线电路基板的变形例的剖视图。

30.图7是布线电路基板的变形例的剖视图。

31.附图标记说明

32.1、布线电路基板;2、多孔质绝缘层;3、导体层;4、导体连接部;5、覆盖绝缘层;21、第1多孔质绝缘层;22、第2多孔质绝缘层;23、第1通孔;24、第2通孔;25、第3通孔;30、31、第1导体层;32、第2导体层;33、40、第3导体层(接地层);34、第1信号线(第1布线部);35、第1接地线(第2布线部);36、第2信号线;37、第2接地线;38、第3接地部(第3布线部);39、第4接地部(第4布线部);51、第1覆盖绝缘层;52、第2覆盖绝缘层。

具体实施方式

33.1.布线电路基板的一个实施方式

34.参照图1来说明本发明的布线电路基板的一个实施方式。

35.布线电路基板1具有厚度。布线电路基板1沿面方向延伸。面方向与厚度方向正交。布线电路基板1具有大致平板形状。

36.布线电路基板1在厚度方向上依次具备多孔质绝缘层2和导体层3。多孔质绝缘层2在厚度方向上依次具备第1多孔质绝缘层21和第2多孔质绝缘层22。导体层3在厚度方向上依次具备第1导体层31、第2导体层32和第3导体层33。具体而言,布线电路基板1朝向厚度方向上的一侧依次具备第3导体层33、第2多孔质绝缘层22、第2导体层32、第1多孔质绝缘层21和第1导体层31。另外,布线电路基板1还具备导体连接部4、覆盖绝缘层5和粘接层6。

37.2.多孔质绝缘层2

38.多孔质绝缘层2朝向厚度方向上的另一侧依次具备第1多孔质绝缘层21和第2多孔质绝缘层22。

39.2.1第1多孔质绝缘层21

40.第1多孔质绝缘层21具有厚度。第1多孔质绝缘层21沿面方向延伸。第1多孔质绝缘层21具有大致平板形状。第1多孔质绝缘层21具有第1通孔23和两个第2通孔24。

41.第1通孔23配置于第1多孔质绝缘层21的第1方向上的中间部。第1方向包含在面方向中。

42.一个第2通孔24与第1通孔23隔开间隔地配置于第1通孔23的第1方向上的一侧。另一个第2通孔24与第1通孔23隔开间隔地配置于第1通孔23的第1方向上的另一侧。另一个第2通孔24在第1方向上相对于第1通孔23配置于一个第2通孔24的相反侧。由此,一个第2通孔24、第1通孔23和另一个第2通孔24在第1方向上依次排列。也就是说,第1通孔23配置于两个第2通孔24之间。

43.第1通孔23和两个第2通孔24分别在厚度方向上贯通第1多孔质绝缘层21。第1多孔质绝缘层21中的分别划分出第1通孔23和两个第2通孔24的内周面沿着厚度方向延伸。上述内周面也可以具有截面积随着朝向厚度方向上的一侧去逐渐增大的锥形形状。

44.2.2第2多孔质绝缘层22

45.第2多孔质绝缘层22在厚度方向上配置于第1多孔质绝缘层21的另一侧。第2多孔质绝缘层22在厚度方向上与第1多孔质绝缘层21隔开间隔。

46.此外,第2多孔质绝缘层22借助后述的第2粘接层62粘接于第1多孔质绝缘层21。

47.第2多孔质绝缘层22具有厚度。第2多孔质绝缘层22沿面方向延伸。第2多孔质绝缘层22具有大致平板形状。第2多孔质绝缘层22具有两个第3通孔25。

48.两个第3通孔25各自在沿厚度方向投影时与两个第2通孔24分别重叠。两个第3通孔25在第1方向上相互隔开间隔地排列。

49.两个第3通孔25分别在厚度方向上贯通第2多孔质绝缘层22。第2多孔质绝缘层22中的分别划分出两个第3通孔25的内周面沿着厚度方向延伸。上述内周面也可以具有截面积随着朝向厚度方向上的另一侧去逐渐增大的锥形形状。

50.2.3多孔质绝缘层2的材料

51.作为多孔质绝缘层2的材料,可举出树脂。树脂并未限定。作为树脂,例如,可举出聚碳酸酯树脂、聚酰亚胺树脂、氟化聚酰亚胺树脂、环氧树脂、酚醛树脂、尿素树脂、三聚氰胺树脂、邻苯二甲酸二丙烯树脂、有机硅树脂、热固性聚氨酯树脂、氟树脂和液晶聚合物。优选举出聚酰亚胺树脂和液晶聚合物。

52.2.4多孔质绝缘层2的物理属性

53.多孔质绝缘层2为多孔质。多孔质绝缘层2具有独立气泡和/或连续气泡。

54.多孔质绝缘层2的孔隙率例如为50%以上,优选为60%以上,更优选为70%以上,进一步优选为80%以上。此外,多孔质绝缘层2的孔隙率例如小于100%,进一步为99%以下。在多孔质绝缘层2的材料为聚酰亚胺树脂的情况下,多孔质绝缘层2的孔隙率通过基于下述式的计算来求出。

55.多孔质绝缘层2的介电常数=空气的介电常数

×

孔隙率+聚酰亚胺的介电常数

×

(1-孔隙率)

56.在此,由于空气的介电常数为1,聚酰亚胺树脂的介电常数为3.5,因此,

57.多孔质绝缘层2的介电常数=孔隙率+3.5(1-孔隙率)

58.孔隙率(%)=[(3.5-多孔质绝缘层2的介电常数)/2.5]

×

100

[0059]

多孔质绝缘层2在频率60ghz下的介电常数例如为2.5以下,优选为1.9以下,更优选为1.6以下,另外例如超过1.0。多孔质绝缘层2的介电常数是通过使用频率60ghz的谐振器法来实测的。

[0060]

多孔质绝缘层2在频率60ghz下的介质耗散因数例如为0.006以下,另外例如超过0。多孔质绝缘层2的介质耗散因数是通过使用频率60ghz的谐振法来实测的。

[0061]

3.导体层3

[0062]

导体层3沿第2方向延伸。第2方向与厚度方向和第1方向交叉。具体而言,第2方向与厚度方向和第1方向正交。

[0063]

导体层3朝向厚度方向上的另一侧依次具备第1导体层31、第2导体层32和第3导体层33。

[0064]

3.1第1导体层31

[0065]

第1导体层31配置于第1多孔质绝缘层21的厚度方向上的一侧。具体而言,第1导体层31配置于第1多孔质绝缘层21的厚度方向上的一侧的面。第1导体层31具有作为第1布线

部的一个例子的第1信号线34和作为两个第2布线部的一个例子的两个第1接地线35。

[0066]

3.1.1第1信号线34

[0067]

第1信号线34沿第2方向传输信号。作为信号,例如,可举出差动信号。信号例如包含小于1a、进一步小于0.1a的小电流。第1信号线34配置于第1导体层31的第1方向上的中间部。第1信号线34配置于第1通孔23的厚度方向上的一侧。第1信号线34将第1通孔23的厚度方向上的一端部封堵。第1信号线34与第1多孔质绝缘层21的位于第1通孔23的周围的部分的厚度方向上的一侧的面接触。第1信号线34包含信号端子341。信号端子341配置于第1信号线34的第2方向上的端部。在信号端子341连接有未图示的外部基板的电极。

[0068]

第1信号线34比如下说明的第1接地线35薄。具体而言,第1信号线34的厚度t1例如为50μm以下,优选为35μm以下,更优选为18μm以下,另外例如为4μm以上。此外,第1信号线34的厚度t1是第1多孔质绝缘层21的厚度方向上的一侧的面与第1信号线34的厚度方向上的一侧的面之间的厚度方向上的长度。

[0069]

3.1.2两个第1接地线35

[0070]

两个第1接地线35分别使对第1信号线34造成影响的弱电流接地。弱电流例如包含小于1a、进一步小于0.1a的电流。两个第1接地线35分别配置于两个第2通孔24各自的厚度方向上的一侧。两个第1接地线35分别将两个第2通孔24各自的厚度方向上的一端部封堵。两个第1接地线35分别与第1多孔质绝缘层21的位于两个第2通孔24的周围的部分的厚度方向上的一侧的面接触。

[0071]

两个第1接地线35在第1方向上相互隔开间隔地配置。一个第1接地线35与第1信号线34隔开间隔地配置于第1信号线34的第1方向上的一侧。

[0072]

另一个第1接地线35与第1信号线34隔开间隔地配置于第1信号线34的第1方向上的另一侧。另一个第1接地线35在第1方向上相对于第1信号线34配置于一个第1接地线35的相反侧。由此,一个第1接地线35、第1信号线34和另一个第1接地线35在第1方向上隔开间隔地依次排列。也就是说,第1信号线34配置在两个第1接地线35之间。

[0073]

两个第1接地线35中的至少一个第1接地线35包含接地端子351。接地端子351配置于该第1接地线35的第2方向上的端部。在接地端子351连接有未图示的接地构件。

[0074]

两个第1接地线35均比第1信号线34厚。

[0075]

另一方面,若两个第1接地线35均为与第1信号线34相同的厚度,则通过后述的按压,多孔质绝缘层2的在厚度方向上与第1信号线34和第1接地线35重叠的部分的厚度会较大地变动,第1信号线34的电特性会较大地变动。具体而言,产生第1信号线34的特性阻抗的失配。

[0076]

两个第1接地线35的厚度t2例如为6μm以上,优选为20μm以上,更优选为40μm以上,另外例如为52μm以下。此外,第1接地线35的厚度t2是第1多孔质绝缘层21的厚度方向上的一侧的面与第1接地线35的厚度方向上的一侧的面之间的厚度方向上的长度。

[0077]

第1接地线35的厚度t2相对于第1信号线34的厚度t1的比(t2/t1)超过1,优选为1.2以上,更优选为1.4以上,进一步优选为1.6以上。第1接地线35的厚度t2相对于第1信号线34的厚度t1的比(t2/t1)的上限并未限定。比(t2/t1)的上限例如为13。

[0078]

3.2第2导体层32

[0079]

第2导体层32配置于第1多孔质绝缘层21的厚度方向上的另一侧。第2导体层32在

厚度方向上相对于第1多孔质绝缘层21配置于第1导体层31的相反侧。第2导体层32在厚度方向上配置于第1多孔质绝缘层21与第2多孔质绝缘层22之间。第2导体层32与第1导体层31电连接。第2导体层32具备第2信号线36和两个第2接地线37。

[0080]

3.2.1第2信号线36

[0081]

第2信号线36连同第1信号线34一起沿第2方向传输上述信号。第2信号线36在沿厚度方向投影时与第1信号线34重叠。第2信号线36在厚度方向上与第1信号线34电连接。

[0082]

3.2.2两个第2接地线37

[0083]

两个第2接地线37连同两个第1接地线35一起使对第1信号线34和第2信号线36造成影响的弱电流接地。两个第2接地线37分别与第2信号线36隔开间隔地配置于第2信号线36的第1方向上的一侧和另一侧。第2接地线37在沿厚度方向投影时与第1接地线35重叠。

[0084]

两个第2接地线37均具有与第2信号线36相同的厚度。

[0085]

3.3第3导体层33

[0086]

第3导体层33是接地层的一个例子。也就是说,第3导体层33连同上述第1接地线35和第2接地线37一起使对第1信号线34和第2信号线36造成影响的弱电流接地。

[0087]

第3导体层33配置于第2多孔质绝缘层22的厚度方向上的另一侧。具体而言,第3导体层33配置于第2多孔质绝缘层22的厚度方向上的另一侧的面。第3导体层33在厚度方向上相对于第2多孔质绝缘层22配置于第2导体层32的相反侧。第3导体层33具有作为第3布线部的一个例子的第3接地部38和作为第4布线部的一个例子的第4接地部39。

[0088]

3.3.1第3接地部38

[0089]

第3接地部38配置于第2多孔质绝缘层22的厚度方向上的另一侧的面的位于两个第3通孔25之间的部分。第3接地部38沿第1方向延伸。第3接地部38在沿厚度方向投影时与第1信号线34重叠。第3接地部38在沿厚度方向投影时包含第1信号线34。具体而言,第3接地部38包含重叠部分381和非重叠部分382。重叠部分381与第1信号线34重叠。非重叠部分382不与第1信号线34重叠。在本实施方式中,重叠部分381是第3接地部38的第1方向上的中间部。非重叠部分382分别从重叠部分381的第1方向上的一端部和另一端部向外侧延伸。第3接地部38为平板形状。

[0090]

第3接地部38比如下说明的第4接地部39薄。具体而言,第3接地部38的厚度t3例如为50μm以下,优选为35μm以下,更优选为18μm以下,另外例如为4μm以上。此外,第3接地部38的厚度t3是第2多孔质绝缘层22的厚度方向上的另一侧的面与第3接地部38的厚度方向上的另一侧的面之间的厚度方向上的长度。

[0091]

3.3.2第4接地部39

[0092]

两个第4接地部39分别配置于两个第3通孔25各自的厚度方向上的另一侧。两个第4接地部39分别将两个第3通孔25各自的厚度方向上的另一端部封堵。两个第4接地部39分别与第2多孔质绝缘层22的位于两个第3通孔25的周围的部分的厚度方向上的另一侧的面接触。

[0093]

两个第4接地部39在第1方向上相互隔开间隔地配置。两个第4接地部39分别具有平板形状。第4接地部39在沿厚度方向投影时与第1接地线35重叠。一个第4接地部39的厚度方向上的一侧部分与第3接地部38的第1方向上的一端部(非重叠部分382)连结。另一个第4接地部39的厚度方向上的一侧部分与第3接地部38的第1方向上的另一端部(非重叠部分

382)连结。由此,两个第4接地部39经由第3接地部38相互电连接。

[0094]

两个第4接地部39均比第3接地部38厚。若两个第4接地部39均比第3接地部38厚,则能够抑制因后述的按压而使多孔质绝缘层2的在厚度方向上与第3接地部38和第4接地部39重叠的部分的厚度较大地变动,能够抑制第1信号线34和第2信号线36的电特性较大地变动。

[0095]

两个第4接地部39的厚度t4例如为6μm以上,优选为20μm以上,更优选为40μm以上,另外例如为52μm以下。第4接地部39的厚度t4是第2多孔质绝缘层22的厚度方向上的另一侧的面与第4接地部39的厚度方向上的另一侧的面之间的在厚度方向上的长度。

[0096]

第4接地部39的厚度t4相对于第3接地部38的厚度t3的比(t4/t3)超过1,优选为1.2以上,更优选为1.4以上,进一步优选为1.6以上。第4接地部39的厚度t4相对于第3接地部38的厚度t3的比(t4/t3)的上限并未限定。比(t4/t3)的上限例如为13。

[0097]

3.4导体层3的材料

[0098]

导体层3的材料并未限定。作为导体层3的材料,例如,可举出铜、铁、银、金、铝、镍和它们的合金(不锈钢和青铜)。作为导体层3的材料,优选举出铜。

[0099]

4.导体连接部4

[0100]

导体连接部4在厚度方向上配置于第1导体层31与第2导体层32之间和第2导体层32与第3导体层33之间。导体连接部4配置于第1通孔23、第2通孔24和第3通孔25。导体连接部4具有第1导体连接部41、两个第2导体连接部42和两个第3导体连接部43。

[0101]

4.1第1导体连接部41

[0102]

第1导体连接部41的一部分(主要部分)填充于第1通孔23,第1导体连接部41的剩余部分(厚度方向上的另一端部)自第1通孔23朝向厚度方向上的另一侧突出。第1导体连接部41的厚度方向上的一端部与第1信号线34接触(连续)。第1导体连接部41的厚度方向上的另一端部与第2信号线36接触。由此,第1信号线34和第2信号线36经由第1导体连接部41电连接。因而,第1信号线34、第2信号线36和第1导体连接部41形成在剖视时呈大致字母i形状的信号路径。信号路径沿厚度方向和第2方向延伸。

[0103]

4.2第2导体连接部42

[0104]

第2导体连接部42的一部分(主要部分)填充于第2通孔24,第2导体连接部42的剩余部分(厚度方向上的另一端部)自第2通孔24朝向厚度方向上的另一侧突出。第2导体连接部42的厚度方向上的一端部与第1接地线35接触(连续)。第2导体连接部42的厚度方向上的另一端部与第2接地线37接触。由此,第1接地线35和第2接地线37经由第2导体连接部42电连接。

[0105]

4.3第3导体连接部43

[0106]

第3导体连接部43的一部分(主要部分)填充于第3通孔25,第3导体连接部43的剩余部分(厚度方向上的一端部)自第3通孔25朝向厚度方向上的一侧突出。第3导体连接部43的厚度方向上的另一端部与第4接地部39接触(连续)。第3导体连接部43的厚度方向上的一端部与第2接地线37接触。由此,第2接地线37和第3导体层33经由第3导体连接部43电连接。

[0107]

以上,第1接地线35、第2接地线37、第3导体层33、第2导体连接部42和第3导体连接部43形成在剖视时呈大致字母u形状的接地路径。接地路径在剖视时朝向厚度方向上的一侧开放。

[0108]

4.4导体连接部4的材料

[0109]

导体连接部4的材料与上述导体层3的材料相同。

[0110]

5.覆盖绝缘层5

[0111]

覆盖绝缘层5配置于导体层3的厚度方向上的一侧和另一侧。覆盖绝缘层5具有第1覆盖绝缘层51和第2覆盖绝缘层52。

[0112]

5.1第1覆盖绝缘层51

[0113]

第1覆盖绝缘层51在厚度方向上配置于第1导体层31的一侧。第1覆盖绝缘层51形成布线电路基板1的厚度方向上的一侧的面。第1覆盖绝缘层51使上述信号端子341和接地端子351暴露。第1覆盖绝缘层51覆盖第1导体层31的除了信号端子341和接地端子351以外的部分。

[0114]

5.2第2覆盖绝缘层52

[0115]

第2覆盖绝缘层52在厚度方向上配置于第3导体层33的另一侧。第2覆盖绝缘层52形成布线电路基板1的厚度方向上的另一侧的面。第2覆盖绝缘层52覆盖第3导体层33。

[0116]

5.3覆盖绝缘层5的材料

[0117]

作为覆盖绝缘层5的材料,例如,可举出上述树脂。

[0118]

6.粘接层6

[0119]

粘接层6配置于上述各层之间。粘接层6的材料(或原料)并未限定。粘接层6朝向厚度方向上的另一侧依次具备第1粘接层61、第2粘接层62和第3粘接层63。

[0120]

6.1第1粘接层61

[0121]

第1粘接层61配置于第1导体层31的厚度方向上的一侧的面和第1多孔质绝缘层21的厚度方向上的一侧的面以及第1覆盖绝缘层51的厚度方向上的另一侧的面。第1粘接层61将第1导体层31以及第1多孔质绝缘层21与第1覆盖绝缘层51粘接起来。第1粘接层61与第1导体层31的厚度方向上的一侧的面和侧面以及第1多孔质绝缘层21的位于第1导体层31的周围的部分的厚度方向上的一侧的面接触。第1粘接层61与第1覆盖绝缘层51的厚度方向上的另一侧的面接触。

[0122]

6.2第2粘接层62

[0123]

第2粘接层62配置于第1多孔质绝缘层21的厚度方向上的另一侧的面和第2多孔质绝缘层22的厚度方向上的一侧的面。也就是说,第2粘接层62配置在第1多孔质绝缘层21与第2多孔质绝缘层22之间。第2粘接层62在厚度方向上埋设第2导体层32。具体而言,第2粘接层62与第2导体层32的厚度方向上的两侧的面和侧面接触。另外,第2粘接层62与上述导体连接部4的剩余部分的侧面接触。具体而言,第2粘接层62与第1导体连接部41的厚度方向上的另一端部的周侧面、第2导体连接部42的厚度方向上的另一端部的周侧面和第3导体连接部43的厚度方向上的一端部的周侧面接触。

[0124]

6.3第3粘接层63

[0125]

第3粘接层63配置于第3导体层33的厚度方向上的另一侧的面和第2多孔质绝缘层22的厚度方向上的另一侧的面以及第2覆盖绝缘层52的厚度方向上的一侧的面。此外,在图1中,第3粘接层63配置于第2多孔质绝缘层22的厚度方向上的另一侧的面的形态未图示。第3粘接层63将第3导体层33以及第2多孔质绝缘层22与第2覆盖绝缘层52粘接起来。第3粘接层63与第3导体层33的厚度方向上的另一侧的面和侧面以及第2多孔质绝缘层22的位于第3

导体层33的周围的部分的厚度方向上的另一侧的面接触。

[0126]

7.第4粘接层64和加强层7

[0127]

另外,也可以是,布线电路基板1还具备假想线所示的第4粘接层64和加强层7。

[0128]

第4粘接层64配置于第2覆盖绝缘层52的厚度方向上的另一侧的面。第4粘接层64将第2覆盖绝缘层52和如下说明的加强层7粘接起来。

[0129]

加强层7加强第1信号线34和第3接地部38。加强层7配置于第2覆盖绝缘层52的厚度方向上的另一侧。具体而言,加强层7借助第4粘接层64粘接于第2覆盖绝缘层52的厚度方向上的另一侧的面。加强层7在沿厚度方向投影时与第1信号线34和第3接地部38重叠。加强层7具有平板形状。加强层7的材料并未限定。作为加强层7的材料,例如,可举出金属和硬质树脂。作为加强层7的材料,优选为金属,具体而言可举出不锈钢、铜、铁和铝。加强层7的厚度并未限定。

[0130]

8.布线电路基板1的制造方法

[0131]

接下来,参照图1~图4b来说明布线电路基板1的制造方法。

[0132]

8.1第1多孔质层叠体81的准备

[0133]

如图2a所示,在该方法中,首先,准备第1多孔质层叠体81。

[0134]

第1多孔质层叠体81朝向厚度方向上的一侧依次具备第2导体层32、一侧第2粘接层62a、第1多孔质绝缘层21和第1基底层311。

[0135]

第1多孔质层叠体81的第2导体层32配置于第1多孔质绝缘层21的厚度方向上的另一侧。第1多孔质层叠体81的第2导体层32处于尚未图案化之前而不是图1所示的布线电路基板1的第2导体层32。

[0136]

一侧第2粘接层62a配置于第2导体层32的厚度方向上的一侧的面和第1多孔质绝缘层21的厚度方向上的另一侧的面。

[0137]

第1基底层311配置于第1多孔质绝缘层21的厚度方向上的一侧的面。第1基底层311包含在图1中的布线电路基板1的第1导体层31中。

[0138]

第1多孔质层叠体81的准备方法例如记载于日本特开2019-123851号公报。

[0139]

8.2第1导通部91的形成

[0140]

如图2b所示,接着,使第1导通部91形成于第1基底层311、第1多孔质绝缘层21和一侧第2粘接层62a。此外,第1多孔质绝缘层21的第1导通部91是上述第1通孔23。

[0141]

作为第1导通部91的形成方法,例如,可举出穿孔加工。作为穿孔加工,例如,可举出激光加工、钻头加工和喷砂法。优选举出激光加工。

[0142]

8.3第1镀层312的形成

[0143]

如图2c所示,接着,使第1镀层312形成于第1导通部91的内周面和第1基底层311的厚度方向上的一侧的面。第1镀层312的形成于第1导通部91的内周面的部分是上述第1导体连接部41。

[0144]

8.4第2导体层32的图案化

[0145]

如图2d所示,对第2导体层32进行图案化而形成第2信号线36和两个第2接地线37。作为第2导体层32的图案化,例如,可举出湿蚀刻和干蚀刻,优选举出湿蚀刻。

[0146]

8.5第2多孔质层叠体82相对于第2导体层32贴合

[0147]

如图2d的下侧图和图3a所示,将第2多孔质层叠体82贴合于第2导体层32。

[0148]

如图2d的下侧图所示,首先,准备第2多孔质层叠体82。第2多孔质层叠体82朝向厚度方向的另一侧依次具备另一侧第2粘接层62b、第2多孔质绝缘层22和第2基底层331。

[0149]

另一侧第2粘接层62b配置于第2多孔质绝缘层22的厚度方向上的一侧的面。

[0150]

第2基底层331配置于第2多孔质绝缘层22的厚度方向上的另一侧的面。第2基底层331包含在上述第3导体层33中。

[0151]

第2多孔质层叠体82的准备方法例如记载于日本特开2019-123851号公报。

[0152]

接着,如图2d的箭头和图3a所示,将第2多孔质层叠体82的另一侧第2粘接层62b贴合于第2导体层32。此时,使用能够沿厚度方向按压的按压机(未图示)。按压的压力并未限定。按压的压力例如为0.5mpa以上,优选为3mpa以上,另外例如为10mpa以下。按压的时间例如为1分钟以上,优选为10分钟以上,另外例如为120分钟以下。按压也可以是热压。按压温度例如为80℃以上,优选为120℃以上,另外例如为300℃以下。

[0153]

在上述另一侧第2粘接层62b的贴合过程中,一侧第2粘接层62a和另一侧第2粘接层62b变形而进入相邻的第2信号线36与第2接地线37之间。由此,一侧第2粘接层62a和另一侧第2粘接层62b形成第2粘接层62。在图3a~图4b中,用假想线示出一侧第2粘接层62a与另一侧第2粘接层62b之间的界面,但该界面也可以不被观察到。一侧第2粘接层62a和另一侧第2粘接层62b构成一体。

[0154]

8.6第2导通部92和第3导通部93的形成

[0155]

如图3b所示,使第2导通部92形成于第1镀层312、第1基底层311和一侧第2粘接层62a。此外,第1多孔质绝缘层21的第2导通部92是第2通孔24。

[0156]

并且,使第3导通部93形成于第2基底层331、第2多孔质绝缘层22和另一侧第2粘接层62b。此外,第2多孔质绝缘层22的第3导通部93是第3通孔25。

[0157]

作为第2导通部92和第3导通部93的形成方法,可举出第1导通部91所例示的形成方法。

[0158]

8.7第2镀层313和第3镀层332的形成

[0159]

接着,如图3c所示,使第2镀层313形成于第1镀层312的厚度方向上的一侧的面和第2导通部92的内周面。并且,使第3镀层332形成于第2基底层331的厚度方向上的另一侧的面和第3导通部93的内周面。

[0160]

具体而言,在形成第2镀层313和第3镀层332之前,如图3b所示,将第1抗蚀剂95配置于第1镀层312的厚度方向上的一侧的面,将第2抗蚀剂96配置于第2基底层331的厚度方向上的另一侧的面。第1抗蚀剂95和第2抗蚀剂96均是抗镀层。第1抗蚀剂95具有第2镀层313的互补图案。第2抗蚀剂96具有第3镀层332的互补图案。

[0161]

之后,将配置有第1抗蚀剂95的第1镀层312和配置有第2抗蚀剂96的第2基底层331的抗蚀剂层叠体83浸渍于镀浴中,实施镀敷处理。

[0162]

在第1镀层312的从第1抗蚀剂95暴露的部分的厚度方向上的一侧的面和第2导通部92的内周面上析出第2镀层313。另一方面,在第1镀层312的配置有第1抗蚀剂95的部分的厚度方向上的一侧的面上不析出第2镀层313。

[0163]

在第2基底层331的从第2抗蚀剂96暴露的部分的厚度方向上的另一侧的面和第3导通部93的内周面上析出第3镀层332。另一方面,在第2基底层331的配置有第2抗蚀剂96的部分的厚度方向上的另一侧的面上不析出第3镀层332。

[0164]

由此,形成具备第3接地部38和第4接地部39的第3导体层33。

[0165]

第3接地部38由第2基底层331形成。因此,第3接地部38的厚度t3与第2基底层331的厚度相同。

[0166]

第4接地部39由第2基底层331和第3镀层332形成。因此,第4接地部39的厚度t4与第2基底层331和第3镀层332的合计厚度相同。

[0167]

之后,去除上述第1抗蚀剂95和第2抗蚀剂96。

[0168]

8.8第1镀层312和第1基底层311的图案化

[0169]

如图4a所示,对第1镀层312和第1基底层311进行图案化。作为第1镀层312和第1基底层311的图案化,例如,可举出湿蚀刻和干蚀刻,优选举出湿蚀刻。由此,形成具备第1信号线34和第1接地线35的第1导体层31(实施第1工序)。

[0170]

第1信号线34由图案化后的第1基底层311和图案化后的第1镀层312形成。因此,第1信号线34的厚度t1是第1基底层311和第1镀层312的合计厚度。

[0171]

第1接地线35由图案化后的第1基底层311、图案化后的第1镀层312和第2镀层313形成。因此,第1接地线35的厚度t2是第1基底层311、第1镀层312和第2镀层313的合计厚度。

[0172]

8.9第1覆盖层叠体85和第2覆盖层叠体86的贴合

[0173]

如图4b所示,将第1覆盖层叠体85贴合于第1导体层31(实施第2工序)。如假想线所示,第1覆盖层叠体85朝向厚度方向上的另一侧依次具备第1覆盖绝缘层51和第1粘接层61。

[0174]

并且,将第2覆盖层叠体86贴合于第3导体层33。如假想线所示,第2覆盖层叠体86朝向厚度方向上的一侧依次具备第2覆盖绝缘层52和第3粘接层63。

[0175]

在上述贴合过程中,使用上述按压机。按压的条件与上述相同。

[0176]

在上述第1覆盖层叠体85的贴合过程中,第1粘接层61进入到相邻的第1信号线34与第1接地线35之间。第1粘接层61与第1多孔质绝缘层21的自第1信号线34和第1接地线35暴露的部分的厚度方向上的一侧的面接触。

[0177]

在上述第2覆盖层叠体86的贴合过程中,第3粘接层63与第2多孔质绝缘层22的位于第3导体层33的周围的部分的厚度方向上的另一侧的面接触。

[0178]

由此,制造出具备多孔质绝缘层2、导体层3、导体连接部4、覆盖绝缘层5和粘接层6的布线电路基板1。

[0179]

并且,如图1所示,在布线电路基板1设置加强层7的情况下,将加强层7借助第4粘接层64贴合于第2覆盖绝缘层52。在加强层7的贴合过程中,使用上述按压机。按压的条件与上述相同。

[0180]

9.一个实施方式的作用效果

[0181]

在该布线电路基板1中,第1接地线35比第1信号线34厚。换言之,第1信号线34比第1接地线35薄。

[0182]

因此,例如,在将第2多孔质层叠体82(参照图2d)贴合于第2导体层32时,并且在将加强层7设于布线电路基板1时,若在厚度方向上对第1多孔质绝缘层21进行按压,则同第1多孔质绝缘层21的在厚度方向上与第1接地线35重叠的部分相比,第1多孔质绝缘层21的在厚度方向上与第1信号线34重叠的部分承受较小的按压压力。因此,同第1多孔质绝缘层21的在厚度方向上与第1接地线(第2布线部)35重叠的部分的厚度的变动相比,能够抑制第1多孔质绝缘层21的在厚度方向上与第1信号线34重叠的部分的厚度的变动。具体而言,能够

抑制第1信号线34的特性阻抗的失配。

[0183]

其结果,与第1接地线35的电特性的变动相比,能够抑制第1信号线34的电特性的变动。

[0184]

另一方面,虽然第1多孔质绝缘层21的与第1接地线35重叠的部分较大地变动,但由于流入第1接地线35的弱电流接地,因此容许第1接地线35的电特性的较大的变动。

[0185]

在该布线电路基板1中,作为接地层的第3导体层33具备与第1信号线34重叠的第3接地部38和与第1接地线35重叠且比第3接地部38厚的第4接地部39。因此,在厚度方向上对布线电路基板1进行按压时,同多孔质绝缘层2(第1多孔质绝缘层21和第2多孔质绝缘层22)的在厚度方向上与第1接地线35重叠的部分相比,多孔质绝缘层2的在厚度方向上与第1信号线34重叠的部分会承受更小的按压压力。因此,同多孔质绝缘层2的在厚度方向上与第1接地线35重叠的部分的厚度的变动相比,能够进一步抑制多孔质绝缘层2的在厚度方向上与第1信号线34重叠的部分的厚度的变动。具体而言,能够进一步抑制第1信号线34的特性阻抗的失配。

[0186]

另外,在上述制造方法中,如图4b所示,在将第1覆盖层叠体85贴合于第1导体层31的工序中,即使对多孔质绝缘层2(第1多孔质绝缘层21和第2多孔质绝缘层22)作用有较大的按压压力,如所述那样,同多孔质绝缘层2的在厚度方向上与第1接地线35重叠的部分的厚度的变动相比,也能够抑制多孔质绝缘层2的在厚度方向上与第1信号线34重叠的部分的厚度的变动。其结果,与第1接地线35的电特性的变动相比,能够抑制第1信号线34的电特性的变动。

[0187]

10.变形例

[0188]

在变形例中,对于与一个实施方式相同的构件和工序,标注相同的附图标记并省略其详细的说明。另外,在变形例中,除了特别记载以外,能够起到与一个实施方式相同的作用效果。并且,能够适当组合一个实施方式和其变形例。

[0189]

也可以是,第1接地线35是第1电源线,第2接地线37是第2电源线,第3导体层33是电源层。第1电源线、第2电源线和电源层连同第2导体连接部42和第3导体连接部43一起形成电源路径。在电源路径,例如,流动有1a以上、乃至10a以上的大电流。

[0190]

如图1所示,第1信号线34配置在两个第1接地线35之间。在变形例中,第1信号线34也可以在第1方向上配置于相对于一个第1接地线35而言的另一个第1接地线35的相反侧,不过对此未图示。另外,第1信号线34也可以在第1方向上配置于相对于另一个第1接地线35而言的一个第1接地线35的相反侧。

[0191]

优选的是,第1信号线34配置在两个第1接地线35之间。若如此设置,则在使用具有平板形状的按压板进行按压时,多孔质绝缘层2的在厚度方向上与两个第1接地线35重叠的部分能够均衡地承受较大的按压压力,因此,多孔质绝缘层2的与配置在两个第1接地线35之间的第1信号线34重叠的部分承受更小的按压压力。因此,同多孔质绝缘层2的在厚度方向上与第1接地线35重叠的部分的厚度的变动相比,能够进一步抑制多孔质绝缘层2的在厚度方向上与第1信号线34重叠的部分的厚度的变动。

[0192]

第1接地线(第2布线部)35也可以是1个,不过对此未图示。

[0193]

在图5所示的布线电路基板1中,导体层3具有作为接地层的一个例子的第1导体层30。第1导体层30配置于第1多孔质绝缘层21的厚度方向上的一侧的面。第1导体层30具备第

1接地部301和第2接地部302。

[0194]

第1接地部301配置于第1多孔质绝缘层21的位于两个第2通孔24之间的部分的厚度方向上的一侧的面。第1接地部301沿第1方向延伸。第1接地部301在沿厚度方向投影时与第3接地部38重叠。第1接地部301具有平板形状。

[0195]

一个第2接地部302的厚度方向上的另一侧部分与第1接地部301的第1方向上的一端部连结。另一个第2接地部302的厚度方向上的另一侧部分与第1接地部301的第1方向上的另一端部连结。由此,两个第2接地部302经由第1接地部301相互电连接。

[0196]

因而,第1导体层30、第2接地线37、第3导体层33和导体连接部4形成在剖视时呈大致矩形的框形形状的接地路径。矩形框在剖视时包围第2信号线36。

[0197]

如图6所示,布线电路基板1具备1个多孔质绝缘层2、1个导体层3、两个粘接层6和1个覆盖绝缘层5。

[0198]

多孔质绝缘层2是第1多孔质绝缘层21。第1多孔质绝缘层21不具备第2通孔24。

[0199]

导体层3是第1导体层31。

[0200]

粘接层6具备第1粘接层61和第2粘接层62。

[0201]

覆盖绝缘层5是第1覆盖绝缘层51。

[0202]

在图6所示的布线电路基板1中,朝向厚度方向上的一侧依次配置第1多孔质绝缘层21、第2粘接层62、第1导体层31、第1粘接层61、第1覆盖绝缘层51。

[0203]

在图7所示的布线电路基板1中,导体层3具备上述第1导体层31和第3导体层40。

[0204]

第3导体层40具备第2信号线36和两个第4接地部39。

[0205]

多孔质绝缘层2包含位于厚度方向上的一端部和/或另一端部的外层,不过对此未图示。外层沿面方向延伸。外层很平滑。例如,第1多孔质绝缘层21包含配置于厚度方向上的一端部和/或另一端部的外层。第2多孔质绝缘层22在厚度方向上的一端部和/或另一端部包含外层。

[0206]

位于第1多孔质绝缘层21的厚度方向上的一端部处的外层形成第1多孔质绝缘层21的厚度方向上的一侧的面。位于第1多孔质绝缘层21的厚度方向上的另一端部处的外层形成第1多孔质绝缘层21的厚度方向上的另一侧的面。外层的厚度相对于第1多孔质绝缘层21的厚度的比例如小于0.1。外层的厚度能够适当调整,以便能够确保外层相对于第1基底层311的剥离强度。具体而言,外层的厚度例如为1μm以上,另外例如为50μm以下,优选为30μm以下。

[0207]

位于第2多孔质绝缘层22的厚度方向上的一端部处的外层形成第2多孔质绝缘层22的厚度方向上的一侧的面。位于第2多孔质绝缘层22的厚度方向上的另一端部处的外层形成第2多孔质绝缘层22的厚度方向上的另一侧的面。外层的厚度相对于第2多孔质绝缘层22的厚度的比例如小于0.1。外层的厚度能够适当调整,以便能够确保外层相对于另一侧第2粘接层62b的剥离强度。具体而言,外层的厚度例如为1μm以上,另外例如为50μm以下,优选为30μm以下。

[0208]

粘接层6具备未图示的第4粘接层和第5粘接层,不过对此未图示。

[0209]

第4粘接层配置于第1多孔质绝缘层21的厚度方向上的一侧的面。第4粘接层介于第1多孔质绝缘层21与第1导体层31之间。第4粘接层将第1多孔质绝缘层21和第1导体层31粘接起来。在该变形例中,在第1多孔质绝缘层21的厚度方向上的一侧的面配置有第4粘接

层,在第1多孔质绝缘层21的厚度方向上的另一侧的面配置有第2粘接层62(参照一侧第2粘接层62a、图3c)。

[0210]

第5粘接层配置于第2多孔质绝缘层22的厚度方向上的另一侧的面。第5粘接层介于第2多孔质绝缘层22与第3导体层33之间。第5粘接层将第2多孔质绝缘层22和第3导体层33粘接起来。在该变形例中,在第2多孔质绝缘层22的厚度方向上的一侧的面配置有第2粘接层62(参照另一侧第2粘接层62b、图3c),在第2多孔质绝缘层22的厚度方向上的另一侧的面配置有第5粘接层。

[0211]

为了制造该变形例的布线电路基板1,如参照图2a那样,准备朝向厚度方向上的一侧依次具备第2导体层32、一侧第2粘接层62a、第1多孔质绝缘层21和未图示的第4粘接层和第1基底层311的第1多孔质层叠体81。

[0212]

如参照图2d的下侧图那样,使用朝向厚度方向的另一侧依次具备另一侧第2粘接层62b、第2多孔质绝缘层22、未图示的第5粘接层和第2基底层331的第2多孔质层叠体82。

[0213]

另外,作为本发明的例示的实施方式提供了上述方案,但是上述方案只不过是例示,不能进行限定性的解释。对于本领域的技术人员来说显而易见的本发明的变形例包含在权利要求书中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1