一种上下沿对称的或非门电路的制作方法

本发明涉及集成电路设计领域里的标准单元电路,特别涉及一种上下沿对称的或非门电路。

背景技术:

1、一般来说,晶圆厂会提供一套基于其工艺开发的标准单元库,该单元库包含一些最基本最常用的电路单元,如与非门、或非门、加法器、反相器、寄存器等。但不同的芯片设计厂商往往需要在此基础上做一些定制修改,以适应其设计的特殊需求。

2、传统的或非门如图1所示,它的上拉电路为两个pmos(全称:positive channelmetal oxide semiconductor)串联,而下拉电路为两个nmos(全称:n-metal-oxide-semiconductor)并联,这就导致一个现象:该电路的上升沿比较慢,而下降沿比较快。这种不对称性导致了上升沿时间和下降沿时间的严重不一致,导致在一些对上升沿和下降沿一致性要求较高的电路中不能使用。如果不考虑nmos和pmos之间的性能差异,那么该电路的下降沿时间约为上升沿时间的一半。

3、即在现有技术中,标准的或非门电路由于其上拉电路的结构和下拉电路的结构不对称,很容易造成其输出的上升沿时间和下降沿时间有较大的差距。这种差距在有一些使用场景下是无法接受的,例如时钟生成电路,不对称的上升沿和下降沿会造成时钟的占空比偏离。

4、另外,标准的或非门电路由于其上拉电路较弱,因此在超低电压下工作的时候会有ocv过高的问题。

5、此外,现有技术包括以下术语:

6、ocv(open circuit voltage):由于制造工艺和环境等原因导致芯片上各部分的mos管特征不能完全一样,从而造成的偏差。这种偏差主要体现在mos管的速度上,而且随着工作电压的降低,这种偏差会更大。因此,如果要让电路能在超低电压下工作,就必须从电路设计上减小ocv。

7、蒙特卡洛仿真:是指以mos管的参数作为随机变量,通过多次的随机输入而产生不同的输出结果。通过观察结果的一致性可以知道电路的ocv大小。

8、超低电压:芯片的功耗与工作电压的平方成正比,因此降低芯片功耗最有效的方法就是降低工作电压。但是在超低电压下mos管的ocv会变的很大,因此如果想让芯片在超低电压下工作,就必须克服超低电压下的ocv问题。

9、上升沿与下降沿对称:标准逻辑的单元的上升沿速度和下降沿速度如果不对称,会造成电路的翻转率过高,从而导致功耗增加。除此以外,在时钟生成电路里,因为对占空比要求更高,所以也要求上升沿速度和下降沿速度尽量对称。

技术实现思路

1、为了解决上述问题,本申请所要解决的技术问题的目的在于:采用一种特殊的结构,使得或非门输出的上升沿时间和下降沿时间十分对称,达到了在一些特殊场景下使用的要求。同时本申请减小的上拉电路的ocv,使得在超低电压下工作的时候有更好的鲁棒性。

2、具体地,本发明提供一种上下沿对称的或非门电路,包括:

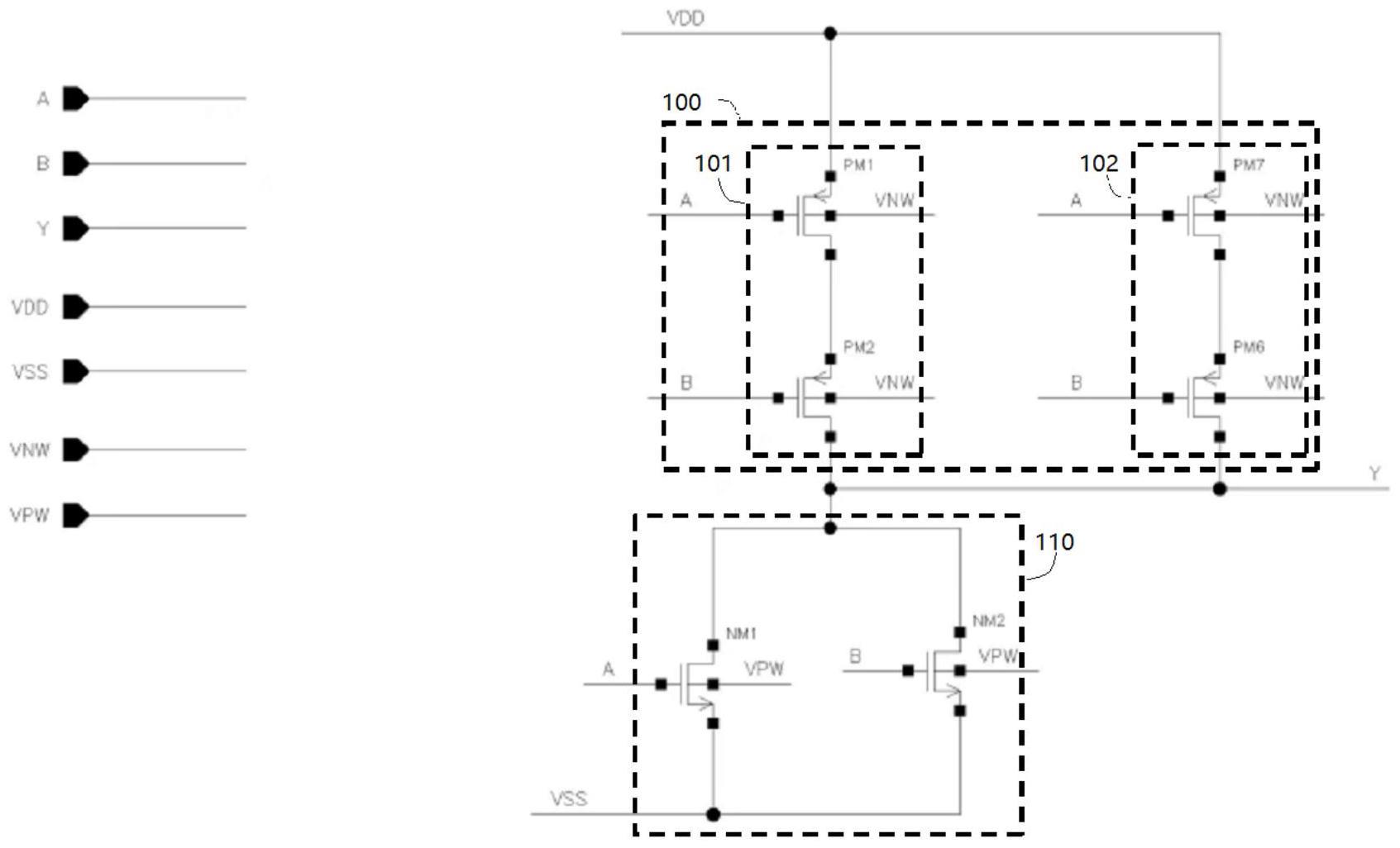

3、一上拉电路(100),为一个两两串联的pmos管再并联的电路,包括第一串联电路(101)的两个pmos管,分别记为pm1和pm2;以及第二串联电路(102)的两个pmos管,分别记为pm6和pm7,所述第一串联电路(101)和第二串联电路(102)做并联连接在一起;和

4、一下拉电路(110),为一个并联两个nmos管的电路,分别记为nm1和nm2;

5、所述上拉电路(100)与下拉电路(110)直接通过导线相连接;

6、所述第一串联电路(101)和第二串联电路(102)的并联是通过两者的一端以导线连接vdd,另一端通过导线连接y,输出信号y既连接上拉电路又连接下拉电路;当pmos开nmos关的时候,上拉电路开启,下拉电路关闭,y=vdd;反之,当pmos关nmos开的时候,上拉电路关闭,下拉电路开启,y=vss;

7、所述下拉电路(110)一端通过导线连接所述上拉电路(100),另一端通过导线连接vss。

8、所述第一串联电路(101)中,所述pm1一端通过导线连接vdd,所述pm1的a是逻辑输入信号,与所述pm2的逻辑输入信号b共同决定输出信号y的值;所述pm1的vnw是输入电压信号,用来给pmos管的n阱供电,另一端通过导线与所述pm2连接;

9、所述pm2的b是逻辑输入信号,与所述pm1的逻辑输入信号a共同决定输出信号y的值;vnw是输入电压信号,用来给pmos管的n阱供电,另一端通过导线连接y,并与所述第二串联电路(102)、所述下拉电路(110)连接,即y是逻辑输出信号,其值等于a或非b即!(a|b));

10、所述第二串联电路(102)中,所述pm7一端通过导线连接vdd,所述pm7的a作为输入端,另一端通过导线与所述pm6连接;所述pm6的b作为输入端,另一端通过导线连接y,并与所述第一串联电路(101)、所述下拉电路(110)连接,其中,a是逻辑输入信号,与另一逻辑输入信号b共同决定输出信号y的值;vnw是输入电压信号,用来给pmos管的n阱供电。

11、所述下拉电路的两两并联为两个nmos管的并联,分别记为nm1和nm2。

12、所述nm1的一端与所述上拉电路(100)通过导线连接,a、vpw作为输入端,另一端vss源端接地;

13、所述nm2的一端与所述上拉电路(100)通过导线连接,b、vpw作为输入端,另一端vss源端接地;

14、所述nm1与所述nm2通过导线实现并联连接构成下拉电路(110)。

15、所述或非门电路当不考虑nmos和pmos的性能差异时,其上升沿时间和下降沿时间差异能够忽略即视为相等。

16、所述电路应用于在超低电压下工作的集成电路芯片。

17、由此,本申请的优势在于:提供了一种结构简单,可以在超低电压下工作且鲁棒性良好的或非门电路,能够实现上下沿对称。

技术特征:

1.一种上下沿对称的或非门电路,其特征在于,包括:

2.根据权利要求1所述的一种上下沿对称的或非门电路,其特征在于,所述第一串联电路(101)中,所述pm1一端通过导线连接vdd,所述pm1的a是逻辑输入信号,与所述pm2的逻辑输入信号b共同决定输出信号y的值;所述pm1的vnw是输入电压信号,用来给pmos管的n阱供电,另一端通过导线与所述pm2连接;

3.根据权利要求1所述的一种上下沿对称的或非门电路,其特征在于,所述下拉电路的两两并联为两个nmos管的并联,分别记为nm1和nm2。

4.根据权利要求3所述的一种上下沿对称的或非门电路,其特征在于所述nm1的一端与所述上拉电路(100)通过导线连接,a、vpw作为输入端,另一端vss源端接地;

5.根据权利要求1所述的一种上下沿对称的或非门电路,其特征在于,所述或非门电路当不考虑nmos和pmos的性能差异时,其上升沿时间和下降沿时间差异能够忽略即视为相等。

6.根据权利要求1所述的一种上下沿对称的或非门电路,其特征在于,所述电路应用于在超低电压下工作的集成电路芯片。

技术总结

本发明提供一种上下沿对称的或非门电路,包括:一上拉电路,为一个两两串联的PMOS管再并联的电路,包括第一串联电路的两个PMOS管,分别记为PM1和PM2;以及第二串联电路的两个PMOS管,分别记为PM6和PM7,所述第一串联电路和第二串联电路做并联连接在一起;和一下拉电路,为一个并联两个NMOS管的电路,分别记为NM1和NM2;所述上拉电路与下拉电路相连接;所述第一串联电路和第二串联电路的并联是通过两者的一端以导线连接VDD,另一端通过导线连接Y实现的;所述下拉电路一端通过导线连接所述上拉电路,另一端通过导线连接VSS。

技术研发人员:孙文中,刘睿

受保护的技术使用者:合肥小鲲科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!