半导体存储器装置和制造半导体存储器装置的方法与流程

本公开的各种实施方式涉及电子装置,并且更具体地,涉及包括沟道结构的半导体存储器装置和制造半导体存储器装置的方法。

背景技术:

1、近来,计算机环境的范式已经转变为无处不在的计算,使得可以随时随地使用计算机系统。由此,诸如移动电话、数码相机、笔记本计算机之类的便携式电子装置的使用迅速增加。通常,这样的便携式电子装置使用采用了半导体存储器装置的存储器系统,换句话说,使用数据储存装置。数据储存装置用作便携式电子装置的主存储器装置或辅助存储器装置。

2、使用半导体存储器装置的数据储存装置的优点在于:由于没有机械驱动部件,稳定性和耐久性优异,信息访问速度高,并且功耗低。作为具有这些优点的存储器系统的示例,数据储存装置包括通用串行总线(usb)存储器装置、具有各种接口的存储卡、固态驱动器(ssd)等。

3、半导体存储器装置被分类为易失性存储器装置和非易失性存储器装置。

4、这样的非易失性存储器装置具有比较低的写入和读取速度,但即使在供电中断时仍保留存储在其中的数据。因此,非易失性存储器装置用于存储不论是否供电都保留的数据。非易失性存储器装置的代表性示例包括只读存储器(rom)、掩模rom(mrom)、可编程rom(prom)、可擦除可编程rom(eprom)、电可擦除可编程rom(eeprom)、闪存、相变随机存取存储器(pram)、磁ram(mram)、电阻式ram(rram)、铁电式ram(fram)等。闪存被分类为nor型和nand型。

技术实现思路

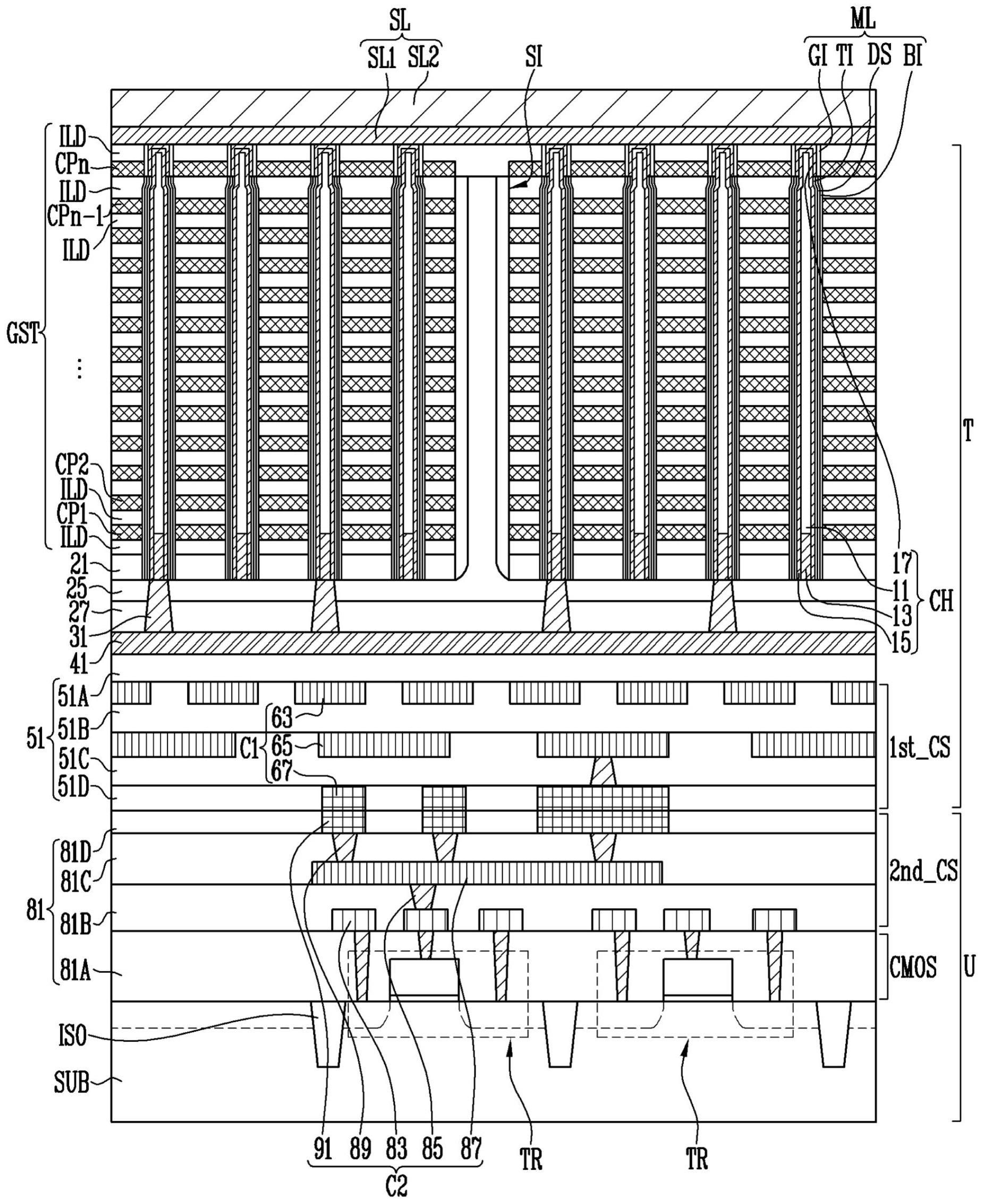

1、本公开的实施方式可以提供一种半导体存储器装置。该半导体存储器装置可以包括:栅极层叠体,其包括在基板上沿垂直方向交替层叠的层间绝缘层和导电图案;沟道结构,其贯穿栅极层叠体的至少一部分,并且沟道结构的上表面保留为被栅极层叠体暴露;存储器层,其被配置为包围沟道结构的侧壁;以及源极线结构,其形成在栅极层叠体上以接触沟道结构的上表面,其中,沟道结构可以包括第一沟道层和第二沟道层,第一沟道层沿垂直方向延伸,并且第二沟道层被配置为包围第一沟道层的与多个导电图案当中的最上的导电图案相邻的侧壁。

2、本公开的实施方式可以提供一种半导体存储器装置。该半导体存储器装置可以包括:栅极层叠体,其包括在基板上沿垂直方向交替层叠的层间绝缘层和导电图案;沟道结构,其贯穿栅极层叠体的至少一部分,并且沟道结构的上表面保留为被栅极层叠体暴露;存储器层,其被配置为包围沟道结构的侧壁;以及源极线结构,其形成在栅极层叠体上以接触沟道结构的上表面,其中,沟道结构可以包括沿垂直方向延伸的芯绝缘层,第一沟道层,其被配置为包围芯绝缘层的外壁,以及第二沟道层,其被配置为包围第一沟道层的与多个导电图案当中的最上的导电图案相邻的侧壁,并且其中,存储器层可以包括设置在第二沟道层和最上的导电图案之间的栅极绝缘层。

3、本公开的实施方式可以提供一种制造半导体存储器装置的方法。该方法可以包括:形成包括在基板上沿垂直方向交替层叠的层间绝缘层和导电图案的栅极层叠体;形成多个沟道结构,每个沟道结构包括芯绝缘层、第一沟道层和存储器层,芯绝缘层贯穿栅极层叠体的至少一部分并且具有延伸到基板中的端部,第一沟道层被配置为包围芯绝缘层的侧壁和端部,并且存储器层从第一沟道层和栅极层叠体之间的区域延伸到第一沟道层的端部和基板之间的区域;通过去除基板使多个沟道结构的端部从栅极层叠体突出;在所述沟道结构的突出的端部当中通过去除存储器层来使第一沟道层暴露;沿着暴露的第一沟道层的表面依次形成第二沟道层和栅极绝缘层;以及在突出的沟道结构之间的栅极层叠体上形成导电图案。

技术特征:

1.一种半导体存储器装置,所述半导体存储器装置包括:

2.根据权利要求1所述的半导体存储器装置,其中,所述沟道结构的所述上表面是所述第二沟道层的表面。

3.根据权利要求1所述的半导体存储器装置,所述半导体存储器装置还包括:

4.根据权利要求3所述的半导体存储器装置,其中,所述存储器层被设置在所述多个导电图案当中的其它导电图案与所述第一沟道层之间。

5.根据权利要求4所述的半导体存储器装置,其中,所述存储器层包括:

6.根据权利要求1所述的半导体存储器装置,其中,所述第一沟道层是未掺杂的多晶硅层。

7.根据权利要求1所述的半导体存储器装置,其中,所述第二沟道层是掺杂的多晶硅层。

8.根据权利要求1所述的半导体存储器装置,其中,所述源极线结构包括:

9.一种半导体存储器装置,所述半导体存储器装置包括:

10.根据权利要求9所述的半导体存储器装置,其中,所述沟道结构的所述上表面是所述第二沟道层的表面。

11.根据权利要求9所述的半导体存储器装置,其中,所述存储器层还包括:

12.根据权利要求9所述的半导体存储器装置,其中,所述第一沟道层是未掺杂的多晶硅层并且所述第二沟道层是掺杂的多晶硅层。

13.一种制造半导体存储器装置的方法,所述方法包括以下步骤:

14.根据权利要求13所述的方法,其中,所述第一沟道层被实现为未掺杂的多晶硅层并且所述第二沟道层被实现为掺杂的多晶硅层。

15.根据权利要求13所述的方法,其中,形成所述第二沟道层和所述栅极绝缘层的步骤包括以下步骤:

16.根据权利要求13所述的方法,所述方法还包括以下步骤:

17.根据权利要求16所述的方法,其中,形成所述源极线结构的步骤包括以下步骤:

18.根据权利要求17所述的方法,其中,所述第一源极层被实现为掺杂的多晶硅层并且所述第二源极层被实现为钨层。

技术总结

本文提供了半导体存储器装置和制造半导体存储器装置的方法。半导体存储器装置包括栅极层叠体,其包括在基板上沿垂直方向交替层叠的层间绝缘层和导电图案;沟道结构,其贯穿栅极层叠体的至少一部分,并且沟道结构的上表面保留为被栅极层叠体暴露。

技术研发人员:金定炯

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!