半导体结构及其制造方法与流程

本公开实施例涉及半导体,特别涉及一种半导体结构及其制造方法。

背景技术:

1、随着半导体结构的不断发展,其关键尺寸不断减小,但由于光刻机的限制,其关键尺寸的缩小存在极限,因此如何在一片晶圆上做出更高存储密度的芯片,是众多科研工作者和半导体从业人员的研究方向。二维或平面半导体器件中,存储单元均是水平方向上排列,因此,二维或平面半导体器件的集成密度可以由单位存储单元所占据的面积决定,则二维或平面半导体器件的集成密度极大地受到形成精细图案的技术影响,使得二维或平面半导体器件的集成密度的持续增大存在极限。因而,半导体器件的发展走向三维半导体器件。

2、然而,目前三维半导体器件中各功能器件的排布方式需要全新的设计,例如在保证各功能器件之间不受影响的同时,充分利用已有的布局空间,以提高三维半导体器件的集成密度。

技术实现思路

1、本公开实施例提供一种半导体结构及其制造方法,至少有利于半导体结构中晶体管结构和电容结构的集成密度。

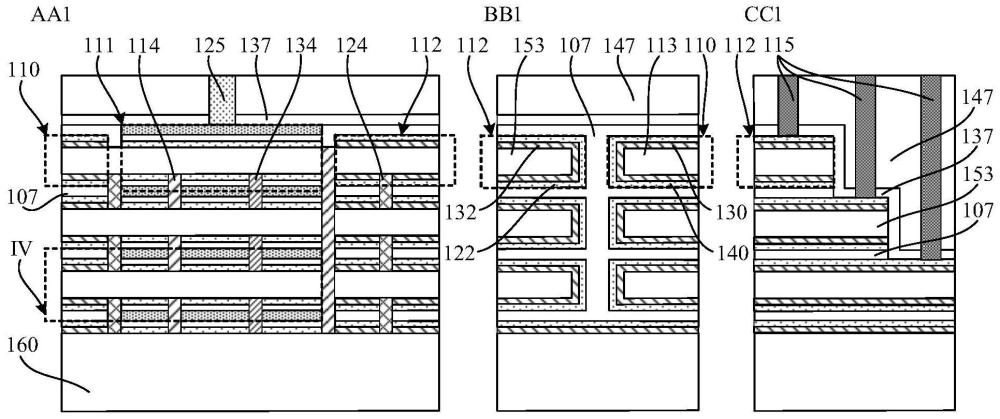

2、根据本公开一些实施例,本公开实施例一方面提供一种半导体结构,包括:沿第一方向排布的晶体管结构和电容结构,所述电容结构沿所述第一方向延伸;字线阶梯结构,与所述晶体管结构沿第二方向间隔排布,且所述字线阶梯结构沿所述第一方向延伸,所述第一方向与所述第二方向相交,所述字线阶梯结构和所述晶体管结构电连接;其中,以垂直于所述第二方向的平面为参考面,所述晶体管结构在所述参考面上的正投影为第一投影,所述电容结构在所述参考面上的正投影为第二投影,所述字线阶梯结构在所述参考面上的正投影为第三投影,所述第三投影覆盖所述第一投影,且所述第三投影与所述第二投影部分重叠。

3、在一些实施例中,所述晶体管结构、所述电容结构以及所述字线阶梯结构组成存储结构,沿所述第一方向上相邻的两个所述存储结构呈中心对称,且两个所述存储结构中一者的所述字线阶梯结构与另一者的所述电容结构沿所述第一方向间隔排布。

4、在一些实施例中,所述晶体管结构包括多个沿第三方向间隔排布的子晶体管结构,且所述第三方向、所述第二方向与所述第一方向两两相交;所述电容结构包括多个沿第三方向排布的子电容结构,所述子电容结构包括依次堆叠的下电极层、电容介电层以及上电极层;所述字线阶梯结构包括沿所述第三方向上间隔排布的多个台阶结构,所述台阶结构沿所述第一方向延伸,且多个所述台阶结构在所述第一方向上的长度不同;其中,所述子晶体管结构与所述子电容结构一一对应连接,所述子晶体管结构与所述台阶结构一一对应连接。

5、在一些实施例中,所述半导体结构还包括:支架结构,所述支架结构位于所述电容结构中相邻的所述子电容结构之间,且所述支架结构环绕所述子电容结构沿所述第一方向延伸的的部分侧壁,以支撑所述电容结构。

6、在一些实施例中,所述晶体管结构、所述电容结构以及所述字线阶梯结构组成存储结构,所述存储结构沿所述第一方向和所述第二方向均间隔排布;所述半导体结构还包括:多个所述存储结构共用的支架结构,所述支架结构沿所述第二方向延伸且环绕位于第二方向排布的多个存储结构中的所述电容结构。

7、在一些实施例中,沿所述第一方向上相邻的两个所述存储结构中一者的所述台阶结构与另一者的所述电容结构之间具有第一间隔;所述支架结构包括:第一支架层,所述第一支架层沿所述第二方向延伸且环绕所述下电极层沿所述第一方向延伸的部分侧壁,所述第一支架层位于所述第一间隔中。

8、在一些实施例中,所述子晶体管结构包括:沿所述第一方向延伸的部分半导体通道,以及环绕所述半导体通道沿所述第一方向延伸的侧壁的栅极结构;所述下电极层包括沿所述第一方向延伸的部分所述半导体通道;所述支架结构还包括:第二支架层,所述第二支架层沿所述第二方向延伸且环绕所述半导体通道的部分侧壁,所述第二支架层位于所述栅极结构和所述电容结构之间以及位于相邻所述台阶结构之间;第三支架层,所述第三支架层沿所述第二方向延伸且环绕所述下电极层中的所述半导体通道的部分侧壁,所述第三支架层位于所述第一支架层远离所述第二支架层的一侧。

9、在一些实施例中,沿所述第一方向上,所述半导体通道包括第一区、第二区以及第三区,所述栅极结构环绕所述第一区的侧壁,所述第二支架层环绕所述第二区的侧壁,所述下电极层包括所述第三区以及环绕所述第三区部分侧壁的子下电极层,所述第一支架层和所述第三支架层环绕所述第三区剩余的侧壁。

10、在一些实施例中,所述半导体结构还包括:多个沿所述第三方向延伸的第一导电柱,所述第一导电柱与所述台阶结构一一对应,且所述第一导电柱与所述台阶结构接触连接;多个沿所述第三方向延伸的第二导电柱,所述第二导电柱与所述上电极层接触连接。

11、根据本公开一些实施例,本公开实施例另一方面还提供一种半导体结构的制造方法,包括:形成沿第一方向排布的晶体管结构和电容结构,所述电容结构沿所述第一方向延伸;形成字线阶梯结构,所述字线阶梯结构与所述晶体管结构沿第二方向间隔排布,且所述字线阶梯结构沿所述第一方向延伸,所述第一方向与所述第二方向相交,所述字线阶梯结构和所述晶体管结构电连接;其中,以垂直于所述第二方向的平面为参考面,所述晶体管结构在所述参考面上的正投影为第一投影,所述电容结构在所述参考面上的正投影为第二投影,所述字线阶梯结构在所述参考面上的正投影为第三投影,所述第三投影覆盖所述第一投影,且所述第三投影与所述第二投影部分重叠。

12、在一些实施例中,采用同一制备步骤形成所述字线阶梯结构和所述晶体管结构。

13、在一些实施例中,所述电容结构包括多个沿第三方向排布的子电容结构,所述制造方法还包括:形成支架结构,所述支架结构位于所述电容结构中相邻的所述子电容结构之间,且所述支架结构环绕所述子电容结构的部分侧壁,以支撑所述电容结构。

14、在一些实施例中,所述支架结构包括第一支架层,形成所述第一支架层的步骤包括:形成沿所述第一方向间隔且交错排布的第一堆叠结构和第二堆叠结构,且所述第一堆叠结构和所述第二堆叠结构沿所述第二方向上间隔且交错排布;形成第一牺牲层,所述第一牺牲层填充满所述第一堆叠结构和所述第二堆叠结构之间的第一间隔;其中,沿第三方向上,所述第一堆叠结构和所述第二堆叠结构均包括交替堆叠的第一半导体层和第二半导体层,且所述第三方向、所述第二方向与所述第一方向两两相交;形成具有第一开口的第一掩膜层,所述第一开口沿所述第二方向延伸,且所述第一开口露出部分所述第一牺牲层;以所述第一掩膜层为掩膜,刻蚀所述第一开口露出的所述第一牺牲层以及与所述第一开口正对的所述第一半导体层,以形成第一空穴;形成第一支架层,所述第一支架层填充满所述第一空穴。

15、在一些实施例中,形成所述第一堆叠结构和所述第二堆叠结构的步骤包括:形成沿所述第三方向上依次堆叠的初始第一半导体层和初始第二半导体层;图形化所述初始第一半导体层和所述初始第二半导体层,以形成所述第一堆叠结构和所述第二堆叠结构。

16、在一些实施例中,所述第一堆叠结构中的所述第二半导体层为半导体通道,沿所述第一方向上,所述半导体通道包括第一区、第二区以及第三区;所述支架结构还包括第二支架层和第三支架层;形成所述第一掩膜层的步骤还包括:形成具有第二开口和第三开口的所述第一掩膜层,其中,所述第二开口沿所述第二方向延伸,且所述第二开口露出所述第二区以及与所述第二区相接触的所述第一牺牲层,所述第三开口沿所述第二方向延伸,且所述第三开口露出相邻所述第一堆叠结构之间的部分所述第一牺牲层;形成所述第二支架层的步骤包括:以所述第一掩膜层为掩膜,刻蚀所述第二开口露出的所述第一牺牲层以及与所述第二开口正对的所述第一半导体层,以形成第二空穴;形成填充满所述第二空穴的所述第二支架层;形成所述第三支架层的步骤包括:以所述第一掩膜层为掩膜,刻蚀所述第三开口露出的所述第一牺牲层以及与所述第三开口正对的所述第一半导体层,以形成第三空穴;形成填充满所述第三空穴的所述第三支架层。

17、在一些实施例中,形成所述晶体管结构的步骤包括:以所述第二半导体层和所述支架结构为掩膜,去除剩余的所述第一半导体层和所述第一牺牲层,以形成第四空穴;形成填充满所述第四空穴的第二牺牲层;形成第二掩膜层,所述第二掩膜层位于所述半导体通道的所述第三区上;以所述第二掩膜层为掩膜,去除与所述半导体通道的所述第一区相接触的所述第二牺牲层,以及去除与所述第二堆叠结构相接触的所述第二牺牲层;形成栅极结构以及导电层,所述栅极结构环绕所述半导体通道的所述第一区的侧壁,所述导电层环绕所述第二堆叠结构中所述第二半导体层的侧壁,所述晶体管结构包括所述栅极结构和所述第一区,所述导电层和所述第二堆叠结构中的所述第二半导体层构成初始字线阶梯结构。

18、在一些实施例中,沿所述第三方向上,环绕不同所述第一区侧壁的所述栅极结构之间具有第二间隔,环绕不同所述第二堆叠结构中所述第一半导体层侧壁的导电层之间具有第三间隔;所述制造方法还包括:形成第一介质层,所述第一介质层填充满所述第二间隔和所述第三间隔。

19、在一些实施例中,形成所述电容结构的步骤包括:形成具有第四开口的第三掩膜层,所述第四开口位于所述半导体通道的所述第三区上;以所述第三掩膜层为掩膜,去除与所述第三区相接触的所述第二牺牲层以形成第五空穴;形成子下电极层,所述子下电极层环绕所述第五空穴露出的所述半导体通道侧壁;形成电容介电层,所述电容介电层环绕所述子电极层远离所述半导体通道的侧壁;形成上电极层,所述上电极层填充满剩余所述第五空穴;其中,所述第三区的所述半导体通道和所述子下电极层构成下电极层,所述下电极层、所述电容介电层以及所述上电极层构成所述电容结构。

20、在一些实施例中,形成所述字线阶梯结构的步骤包括:多次对所述初始字线阶梯结构以及所述第二堆叠结构中的所述第一半导体层进行局部刻蚀,以形成所述字线阶梯结构,所述字线阶梯结构包括沿所述第三方向上间隔排布的多个台阶结构,且多个所述台阶结构沿所述第一方向上的长度不同。

21、在一些实施例中,所述制造方法还包括:形成多个沿所述第三方向延伸的第一导电柱,所述第一导电柱与所述台阶结构一一对应,且所述第一导电柱与所述台阶结构接触连接;形成多个沿所述第三方向延伸的第二导电柱,所述第二导电柱与所述电容结构接触连接。

22、本公开实施例提供的技术方案至少具有以下优点:

23、晶体管结构沿第一方向上具有相对的第一侧和第二侧,沿第二方向上具有相对的第三侧和第四侧,电容结构位于第一侧或第二侧,字线阶梯结构位于第三侧或第四侧,如此,在使得晶体管结构与字线阶梯结构相邻以便于晶体管结构与字线阶梯结构之间电连接的同时,有利于降低晶体管结构、电容结构以及字线阶梯结构三者整体在第一方向上的布局长度。此外,可以理解的是,半导体结构在第一方向上的布局长度一般由电容结构在第一方向上的布局长度决定,字线阶梯结构沿第一方向延伸的部分区域与电容结构正对,可以在降低字线阶梯结构在第二方向上的布局长度的同时,使字线阶梯结构沿第一方向上尽量多布局,以增加字线阶梯结构与电容结构的正对区域的长度,以实现对布局空间的合理利用和降低半导体结构总的布局面积。

- 还没有人留言评论。精彩留言会获得点赞!