一种逐次逼近型模数转换器及终端设备的制作方法

本技术涉及集成电路设计领域,特别是涉及一种逐次逼近型模数转换器及终端设备。

背景技术:

1、模数转换器(analog to digital converter,adc)是通信系统中连结模拟信号与数字信号的桥梁,其主要由采样保持(sample-and-hold,t/h)电路、量化器和编码器组成,参阅图1a所示,图1a展示了模数转换器的基本工作过程:采样保持电路用于对输入的模拟量进行采样后将其转换成离散的模拟量,之后量化器再对其进行量化,生成数字码,最后通过数字电路整合后转换成二进制编码。adc按照采样频率与输入频率的关系可分为奈奎斯特采样模数转换器(nyquist rate adc)和过采样模数转换器(over-sampling adc)两大类。常见的奈奎斯特模数转换器有闪烁型、流水线型、逐次逼近型等。

2、较为常见逐次逼近型(successive approximation,sar)模数转换器的基本结构参阅图1b所示,其主要由时钟电路、采样保持电路、参考电压产生电路、比较器、逐次逼近逻辑电路以及电容型数转换器(capacitor digital to analog converter,cdac)组成。比较器将采样到的输入电压和参考电压进行比较,产生的比较结果(0或1)传递给逐次逼近逻辑电路,逐次逼近逻辑电路从cdac的最高位开始控制另一侧极板的翻转,进而产生新的模拟电压,再与参考电压进行比较得到数字码。如此从高位到低位,依次完成比较和输出数字码。

3、对于逐次逼近型模数转换器而言,如果要进行正确的比较,每一位转换之后cdac的建立误差必须要小于最低有效位(least significant bit,lsb)的一半。然而在建立cdac中位于高位的电容时需要较长的时间,若要等高位的电容完全建立后再进行下一次比较,adc的转换速度就被限制;而建立时间不足导致的不完全建立会引起比较器的比较错误,从而影响adc的精度。为了解决这个问题,针对cdac的冗余技术被提出,常见的用于saradc中的冗余技术有三种:非二进制权重电容阵列、二进制补偿型电容阵列和二进制组合型电容阵列。此外,在sar adc的设计中,速度和精度往往需要兼顾考虑,adc精度越高,意味着转换和电容重建的次数越多,因此需要的时间窗口也越长,adc的速度因此受限。同时,对于驱动高速高精度的模拟前端电路来说,当adc的精度每上升1bit的精度,需要的功耗会随之翻倍。因此,精度和速度可配置的sar adc可以较好地满足当今不同的精度模式、宽采样速率、低功耗的应用场合。但目前兼顾冗余技术以及精度速度可配置优势的sar adc中cdac的电容均为单调翻转,因此,在单调翻转时,对sar adc中的比较器输入共模波动较大,此外,现有的sar adc若想进行冗余切换,则用于读取sar adc的数字误差校准电路(digitalerror circuit,dec)会跳过低位码字,导致损失至少一个量化阶梯。

技术实现思路

1、本技术提供一种逐次逼近型模数转换器及终端设备,通过设计模数转换器中的各进制位的电容大小以及电容配置情况,保证了进行模数转换时模数转换器中的比较器的输入共模不发生大的波动,且用于读取sar adc的数字误差校准电路也可以完全复用,从而不损失量化阶梯。

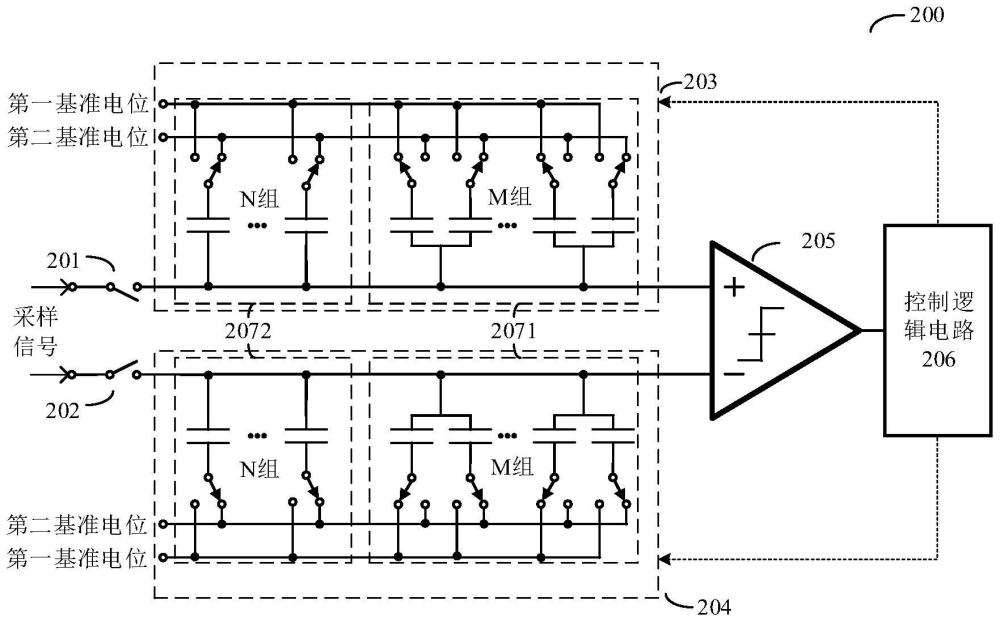

2、第一方面,本技术提供一种逐次逼近型模数转换器,逐次逼近型模数转换器包括:第一采样开关、第二采样开关、第一电容阵列、第二电容阵列、比较器及控制逻辑电路;第一电容阵列中包括:m组第一类型电容器组以及n组第二类型电容器组;第二电容阵列中包括:m组第一类型电容器组以及n组第二类型电容器组,m与n为正整数;其中,每个第一类型电容器组中包括两个电容,两个电容中的每个电容均被配置为选择性的连接到第一基准电位以及第二基准电位中的其中一个基准电位,第一类型电容器组中的两个电容的电容大小相同;每个第二类型电容器组中包括一个电容,其被配置为选择性的连接到第一基准电位以及第二基准电位中的其中一个基准电位,第一基准电位高于第二基准电位;第一采样开关用于接收采样信号的正端输入;第二采样开关用于接收采样信号的负端输入,第一采样开关的第二端与第一电容阵列的输入端连接,第二采样开关的第二端与第二电容阵列的输入端连接比较器的第一输入端连接于第一电容阵列的输出端,比较器的第二输入端连接于第二电容阵列的输出端,比较器,用于对第一输入端以及第二输入端的电平进行比较,输出比较结果,控制逻辑电路连接于比较器的输出端,控制逻辑电路基于比较器的比较结果输出数字信号,并切换第一电容阵列和/或第二电容阵列中的电容连接的基准电位。

3、逐次逼近型模数转换器中可以但不限于上述限定的结构,逐次逼近型模数转换器中还可以包括:采样保持电路。其中,采样保持电路用于连接在采样信号与第一采样开关以及第二采样开关之间。采样保持电路能够跟踪或者保持输入的模拟信号的电平值。在处于采样状态时,采样保持电路的输出信号跟随输入信号变化而变化;在处于保持状态时,采样保持电路的输出信号保持为接到保持命令的瞬间的模拟信号电平值。

4、本技术通过重新设计模数转换器中的各进制位的电容大小以及电容配置情况,将电容阵列通过第一类型电容器组及第二类型电容器组的划分方式,增加了多位冗余的前提下,在高位比较时令比较器两端分别连接的第一类型电容器组,来同时切换连接的基准电位,使比较器的输入共模不发生大的波动,并且,本技术提供模数转换器能适应多种精度模式、宽采样速率、低功耗的应用场合,同时也缩短了设计周期和节省设计成本。

5、为了使比较器的输入共模不发生大的波动,作为一种可能的实施方式,每个第一类型电容器组中的其中一个电容连接第一基准电位,另一个电容连接第二基准电位,控制逻辑电路用于将第一电容阵列的第一类型电容器组中连接第一基准电位的电容切换连接到第二基准电位,并将第二电容阵列的第一类型电容器组中连接第二基准电位的电容切换连接到第一基准电位;或者将第一电容阵列的第一类型电容器组中连接第二基准电位的电容切换连接到第一基准电位,并将第二电容阵列的第一类型电容器组中连接第一基准电位的电容切换连接到第二基准电位。在控制逻辑电路切换第一电容阵列和/或第二电容阵列中的电容连接的基准电位时,控制信号相反从而使得比较器两端整体的输入共模不发生大的波动。

6、作为一种可能的实施方式,控制逻辑电路,包括比较控制电路以及结果输出电路比较控制电路,用于控制比较器比较第一输入端的电平与第二输入端的电平q次,q为m与n之和;结果输出电路用于基于比较器的q次比较结果,输出q位二进制数,第一电容阵列中的m组第一类型电容器组和n组第二类型电容器组与q位二进制数中的每位一一对应,第二电容阵列中的m组第一类型电容器组和n组第二类型电容器组与q位二进制数中的每位一一对应。第一电容阵列中m组第一类型电容器组和n组第二类型电容器组分别与q位二进制数中的各位对应,第二电容阵列中同样包括的m组第一类型电容器组和n组第二类型电容器组,m组第一类型电容器组和n组第二类型电容器组分别与q位二进制数中的各位对应,可选的,第一电容阵列中的m组第一类型电容器组与q位二进制数中的前m位对应,第一电容阵列中的n组第二类型电容器组与q位二进制数中的后n位对应,第二电容阵列中的m组第一类型电容器组与q位二进制数中的前m位对应,第一电容阵列中的n组第二类型电容器组与q位二进制数中的后n位对应。

7、作为一种可能的实施方式,控制逻辑电路还包括电容阵列切换电路,在比较器比较的第k次,电容阵列切换电路用于在k小于或等于m时,若比较器输出的结果为1,则将第一电容阵列中表示第k位的第一类型电容器组中连接第一基准电位的电容切换连接到第二基准电位,并将第二电容阵列中表示第k位的第一类型电容器组中连接第二基准电位的电容切换连接到第一基准电位,若比较器输出的数字信号为0,则将第一电容阵列中表示第k位的第一类型电容器组中连接第二基准电位的电容切换连接到第一基准电位,并将第二电容阵列中表示第k位的第一类型电容器组中连接第一基准电位的电容切换连接到第二基准电位;在k大于m时,若比较器输出的结果为1,将第二电容阵列中表示第k位的第二类型电容器组中的电容切换连接到第一基准电位,若比较器输出的数字信号为0,将第一电容阵列中表示第k位的第二类型电容器组中的电容切换连接到第二基准电位。

8、为了兼容满足高速采样以及高精度的场景,作为一种可能的实施方式,还包括比较控制电路用于:接收降低采样精度指令,将比较器比较第一输入端以及第二输入端的电平的次数降至p次,并将第一电容阵列以及第二电容阵列中表示设定比特位的第二类型电容器组中的电容所连接的电位固定连接在第一基准电位。

9、p小于等于q,p越小,采样速度则越快,降低的比特位精度和设定比特位相关,q与p之间的差值为第二类型电容器组中的电容电位固定连接在第一基准电位的电容的数量。在高速应用下,比较控制电路会接收降低采样精度指令,从而降低比较第一输入端的电平与第一输入端的电平的次数,并控制第一电容阵列以及第二电容阵列中表示设定比特位的第二类型电容器组中的电容固定连接在第一基准电位。

10、作为一种可能的实施方式,第一电容阵列或第二电容阵列中,用于表示第k位的第一类型电容器组或第二类型电容器组的电容值小于或等于用于表示第1位到k-1位的第一类型电容器组或第二类型电容器组的电容值之和。

11、作为一种可能的实施方式,每个第一类型电容器的电容值为4倍单位电容的电容值的倍数,单位电容为第二类型电容器中电容值最小的电容。

12、作为一种可能的实施方式,还包括:数字误差校准电路;数字误差校准电路与控制逻辑电路连接,数字误差校准电路,用于:根据控制逻辑电路输出的数字信号,将控制逻辑电路输出的数字信号转换为设定比特位数的二进制数。控制逻辑电路输出的数字信号经过多个全加器电路进行相加求和后,由数字信号转换为设定比特位数的二进制数。

13、作为一种可能的实施方式,第一电容阵列中的每个第一类型电容器组中具体包括:第一电容、第二电容、第一开关以及第二开关;第一电容的一端与第一电容阵列的输出端连接,第一电容的另一端与第一开关的一端连接;第一开关用于选择连接到第一基准电位或第二基准电位上;第二电容的一端与第一电容阵列的输出端连接,第二电容的另一端与第二开关的一端连接;第二开关用于选择连接到第一基准电位或第二基准电位上;第一电容阵列中的每个第二类型电容器组中具体包括:第三电容以及第三开关;第三电容的一端与第一电容阵列的输出端连接,第三电容的另一端与第三开关的一端连接;第三开关用于选择连接到第一基准电位或第二基准电位上。

14、第一开关、第二开关以及第三开关为单刀双掷开关。本技术实施例对开关的具体形态不做具体限定。在进行模数转换前,因第一类型电容器组中的其中一个电容连接第一基准电位,另一个电容连接第二基准电位,因此,若第一基准电位为高电平电位,第二基准电位为低电平电位或地电位,可选的,第一开关可以连接到第一基准电位上以使第一电容充电,第二开关可以连接到第二基准电位上以使第二电容放电,或者,第一开关可以连接到第二基准电位上以使第一电容放电,第二开关可以连接到第一基准电位上以使第二电容充电,第一开关以及第二开关,不同时连接在第一基准电位或第二基准电位上,则第三开关则选择连接在第二基准电位。

15、作为一种可能的实施方式,第二电容阵列中的每个第一类型电容器组中具体包括:第四电容、第五电容、第四开关以及第五开关;第四电容的一端与第二电容阵列的输出端连接,第四电容的另一端与第四开关的一端连接;第四开关用于选择连接到第一基准电位或第二基准电位上;第五电容的一端与第二电容阵列的输出端连接,第五电容的另一端与第五开关的一端连接;第五开关用于选择连接到第一基准电位或第二基准电位上;第二电容阵列中的每个第二类型电容器组中具体包括:第六电容以及第六开关;第六电容的一端与第二电容阵列的输出端连接,第六电容的另一端与第六开关的一端连接;第六开关用于选择连接到第一基准电位或第二基准电位上。

16、第四开关、第五开关以及第六开关为单刀双掷开关,第一类型电容器组中的其中一个电容连接第一基准电位,另一个电容连接第二基准电位,若第一基准电位为高电平电位,第二基准电位为地电位,第四开关可以连接到第一基准电位上以使第四电容充电,第五开关可以连接到第二基准电位上以使第五电容放电,或者,第四开关可以连接到第二基准电位上以使第四电容放电,第五开关可以连接到第一基准电位上以使第五电容充电,第四开关以及第五开关,不同时连接在第一基准电位或第二基准电位上,而第六开关则选择连接在第二基准电位。

17、第二方面,本技术提供一种终端设备,包括壳体、处理器、存储器,以及第一方面的逐次逼近型模数转换器,处理器与存储器设置于壳体内,存储器与处理器连接,逐次逼近型模数转换器与处理器连接,逐次逼近型模数转换器用于将模拟信号转换为数字信号。

- 还没有人留言评论。精彩留言会获得点赞!