一种汽车防盗指示灯控制电路及其控制方法与流程

1.本发明属于汽车电子控制器技术领域,具体涉及一种汽车防盗指示灯控制电路及其控制方法。

背景技术:

2.bcm:车身控制器。

3.mcu:微处理器,一般不支持运行多任务的复杂系统(比如(嵌入式)linux)。

4.soc:片上系统,能支持运行多任务的复杂系统(比如(嵌入式)linux)。

5.lsd:低边驱动电路。

6.常电:控制器中不可关断的电源,该电源在控制器接入后一直开启。

7.可控电:控制器中可关断的电源,该电源可根据需要开启和关断。

8.目前绝大多数的乘用车都有防盗指示功能,防盗指示灯安装在车辆风挡玻璃或者车窗附近,其控制电路一般是集成在车身控制器或仪表内部,在车主按下智能钥匙的上锁按钮后,汽车的防盗系统就会激活,然后防盗指示灯有规律的间歇性闪烁,车内车外都能很容易地看见。如果防盗指示灯以0.5~1hz的频率闪烁,表明汽车防盗系统已正常工作,车主可以安全离开,否则车主需要检查一下门窗盖是否关闭、电池是否亏电和防盗系统是否损坏等异常,防盗指示灯闪烁也能对盗车贼起警示作用。

9.汽车防盗指示功能比较简单,但是它需要在锁车后一直工作,因此它的耗电对于汽车的闲置时间性能有很大的影响,降低汽车防盗指示电路的功耗是各大汽车控制器厂商的一致目标,现有的汽车防盗指示灯控制电路方案主要有以下两种:

10.1.在车主按下智能钥匙的上锁按钮后,控制器进入休眠状态,控制器中的mcu或soc被周期性地唤醒,唤醒后驱动防盗指示灯,然后再休眠,如此重复。缺陷是mcu或soc被周期性的唤醒,mcu或soc的工作电流比较大,增大了休眠电流,缩短了汽车的闲置时间,如果停放时间较长,就会导致汽车亏电,降低了用户体验感。

11.2.在车主按下智能钥匙的上锁按钮后,控制器进入休眠状态,控制器中的mcu或soc一直休眠,使用专用集成电路驱动防盗指示灯。缺陷是专用集成电路价格较贵,增加了控制器的成本。

12.这两种方案的性价比不高,在充分竞争的汽车电子控制器市场,性价比是决定控制器能否有市场的关键因素。

技术实现要素:

13.本发明要解决的技术问题是:提供一种汽车防盗指示灯控制电路及其控制方法,用于降低汽车防盗指示电路的功耗。

14.本发明为解决上述技术问题所采取的技术方案为:一种汽车防盗指示灯控制电路,包括非稳态电路模块、gnd开关电路模块、反相缓冲电路模块、控制电路模块、缓冲隔离电路模块和lsd电路模块;非稳态电路模块的pwm1引脚连接反相缓冲电路模块的pwm1引脚;

反相缓冲电路模块的pwm2引脚连接lsd电路模块的pwm2引脚;lsd电路模块的pwm3引脚连接缓冲隔离电路模块的pwm3引脚;缓冲隔离电路模块的pwm0引脚连接控制电路模块的pwm0引脚;控制电路模块的do0引脚连接gnd开关电路模块的do0引脚;gnd开关电路模块的gnd-s引脚连接非稳态电路模块的gnd-s引脚;非稳态电路模块的gnd引脚、gnd开关电路模块的gnd引脚、控制电路模块的gnd引脚、缓冲隔离电路模块的gnd引脚连接电源地gnd;非稳态电路模块的vdd1引脚、gnd开关电路模块的vdd1引脚、反相缓冲电路模块的vdd1引脚连接电源vdd1;控制电路模块的vdd2引脚、缓冲隔离电路模块的vdd2引脚连接电源vdd2;lsd电路模块的opl引脚输出低边驱动opl_security_indicator_led,用于外接高边指示灯负载。

15.按上述方案,非稳态电路模块包括定时器u1、第二电阻r2、第四电阻r4、第一电容c1、第二电容c2、第三电容c3、第四电容c4、第五电容c5;定时器u1的vdd引脚用于输入范围为3.3v~5v的电压vdd1,gnd引脚为电源地gnd开关,out引脚用于输出方波pwm1;定时器u1采用计时器集成电路tlc555;第一电容c1是滤波电容,并联在定时器u1的vdd引脚与电源地gnd之间;第三电容c3是滤波电容,并联在定时器u1的vdd引脚与gnd引脚之间;第二电容c2是定时器u1内部阈值滤波电容,并联在定时器u1的cont引脚与gnd引脚之间;第四电容c4和第五电容c5分别并联在定时器u1的trig引脚与gnd引脚之间;第二电阻r2是第四电容c4和第五电容c5主充电电阻,并联在定时器u1的reset引脚与disch引脚之间;reset引脚与vdd引脚短接;第四电阻r4是第四电容c4和第五电容c5的次充电电阻和放电电阻,并联在定时器u1的disch引脚与trig引脚之间;trig引脚与thres引脚短接;第二电阻r2、第四电阻r4、第四电容c4和第五电容c5用于共同决定方波pwm1的频率和占空比特性;当gnd-s连通电源地gnd时,方波pwm1的频率为:

16.f1=1.44/[(r2+2r4_*(c4+c5)],

[0017]

周期为2s;方波pwm1的高电平占空比为:

[0018]

d1=(r2+r4)/(r2+2r4),

[0019]

高电平时间为1.98s;在拉电流不大于1ma时,方波pwm1的高电平幅度不低于(vdd1-0.3)v;在灌电流不大于2ma时,方波pwm1的低电平幅度不高于0.3v;方波pwm1的上升沿时间不大于10us,下降沿时间为不大于5us;非稳态电路模块的工作电流不大于0.2ma;当gnd-s与电源地gnd断开时,定时器u1的out引脚输出悬空,非稳态电路模块的工作电流不大于0.01ma。

[0020]

按上述方案,gnd开关电路模块包括第四数字晶体管q4、第五三极管q5、第七电阻r7、第八电阻r8、第十一电阻r11和第七电容c7;第四数字晶体管q4采用输入反向缓冲npn型数字晶体管;第四数字晶体管q4的基极引脚用于输入do0控制输入信号,射极引脚连接电源地gnd;第七电阻r7为第四数字晶体管q4的集电极上拉限流电阻,第四数字晶体管q4的集电极通过串联第七电阻r7用于输入范围为3.3v~5v的电压vdd1;第八电阻r8为第五三极管q5的基极限流电阻,第四数字晶体管q4的集电极通过串联第八电阻r8连接第五三极管q5的基极;第五三极管q5采用集电极开路的输入反向缓冲npn三极管;第五三极管q5的集电极用于输出gnd-s,射极连接电源地gnd;第十一电阻r11为第五三极管q5的基极分流电阻,第七电容c7为第五三极管q5的基极输入滤波电容,均并联在第五三极管q5的基极与射极之间;当do0输入ttl或cmos高电平时,第四数字晶体管q4饱和导通,第四数字晶体管q4的集电极输出0.1v,第五三极管q5截止,第五三极管q5的集电极输出开路,gnd-s与电源地gnd断开,

vdd1不大于12v时,gnd-s的灌电流不大于5ua时,gnd开关电路模块的工作电流不大于0.6ma;当do0输入ttl或cmos低电平时,第四数字晶体管q4截止,第四数字晶体管q4的集电极输出开路,第五三极管q5饱和导通,第五三极管q5的集电极输出0.1v,gnd-s与电源地gnd连通,gnd-s的灌电流不大于10ma时,gnd-s的电压不大于0.1v,gnd开关电路模块的工作电流不大于0.2ma;当do0输入悬空时,gnd-s连通到gnd,灌电流不大于10ma时,gnd-s的电压不大于0.1v,gnd开关电路模块的工作电流不大于0.2ma;gnd开关电路模块抗10mhz以上的高频干扰。

[0021]

按上述方案,反相缓冲电路模块包括第一三极管q1、第一电阻r1和第三电阻r3;第一三极管q1为输入反向缓冲三极管;第一电阻r1为第一三极管q1的基极分流电阻,并联在第一三极管q1的基极与射极之间;第三电阻r3为第一三极管q1的基极限流电阻;第一三极管q1的基极通过串联第三电阻r3用于接收方波pwm1,集电极用于输出与方波pwm1反相位的方波pwm2,射极用于输入范围为3.3v~5v的电压vdd1;方波pwm2的频率与方波pwm1相同;方波pwm2的高电平占空比为d1=1-0.99=0.1,高电平时间为0.02s;在拉电流不大于10ma时,方波pwm2的高电平幅度不低于vdd1-0.1v,消耗电流不大于0.6ma;若接10kω的下拉电阻负载,输出方波pwm2的低电平幅度不高于0.1v;若不接下拉电阻负载,输出漏电流不大于5ua的开路,消耗电流不大于0.01ma;方波pwm2的上升沿时间不大于10us,下降沿时间不大于5us;方波pwm2相对于方波pwm1的时延不大于1ns,反相缓冲电路模块的工作电流为3ua;第一三极管q1的基极输入开路时,第一三极管q1的集电极输出开路,反相缓冲电路模块的消耗电流不大于3ua。

[0022]

按上述方案,控制电路模块的vdd2引脚用于输入范围为3.3v~5v的mcu或soc的供电电源,gnd引脚连接电源地gnd;pwm0引脚用于输出频率为0.1hz~10hz可调、占空比为0%~100%可调、上升沿时间不大于10us、下降沿时间不大于5us的方波pwm0;do0引脚用于输出数字信号do0;do0引脚和pwm0引脚的输出电压满足ttl或cmos规范,最大拉电流不小于1ma,最大灌电流不小于2ma;若vdd2为常电,控制电路模块具备低功耗模式,低功耗电流不大于0.2ma;若vdd2为可控电,控制电路模块与其它电路共用电源;在正常工作模式,pwm0引脚输出频率为0.2hz、占空比为0.4%、上升沿时间为5us、下降沿时间为3us、高电平拉电流为0.3ma、低电平灌电流为70ua的方波pwm0;do0引脚输出3.3v、拉电流为0.3ma的数字信号do0;在低功耗模式下,vdd2为0v时灌电流为2ua,pwm0引脚开路时灌电流为3ua,do0引脚开路时灌电流为3ua。

[0023]

按上述方案,缓冲隔离电路模块包括第二数字晶体管q2、第三三极管q3、第五电阻r5和第六电阻r6;第二数字晶体管q2采用输入反向缓冲的npn型数字晶体管;第二数字晶体管q2的基极引脚用于输入方波pwm0,射极引脚连接电源地gnd;第五电阻r5为第三三极管q3的基极限流电阻,串联在第三三极管q3的基极与第二数字晶体管q2的集电极引脚之间;第六电阻r6为第三三极管q3的基极分流电阻,并联在第三三极管q3的基极与射极之间;第三三极管q3采用集电极开路的输入反向缓冲pnp三极管;第三三极管q3的射极用于输入范围为3.3v~5v的电压vdd2,集电极用于输出与方波pwm0同相位的方波pwm3;拉电流不大于10ma时,方波pwm3的高电平幅度不低于(vdd1-0.1)v时,消耗电流不大于0.7ma;若接下拉10kω负载的条件下,方波pwm3的低电平幅度不高于0.1v;方波pwm3的低电平幅度为0v时,消耗电流为1ua;若不接下拉负载,输出漏电流不大于5ua的开路,消耗电流不大于0.01ma;

方波pwm3相对于方波pwm0的时延不大于1us;方波pwm3的上升沿时间不大于10us,下降沿时间不大于5us;当第二数字晶体管q2的基极引脚悬空时,第三三极管q3的集电极输出悬空,消耗电流不大于3ua。

[0024]

按上述方案,lsd电路模块包括双向tvs管d1、第六三极管q6、第九电阻r9、第十电阻r10、第十二电阻r12、第十三电阻r13、第六电容c6、第八电容c8;第六三极管q6采用输入反向驱动的npn三极管;第十电阻r10和第十二电阻r12为第六三极管q6的基极限流电阻,第六三极管q6的基极通过串联第十电阻r10输入方波pwm2,第六三极管q6的基极通过串联第十二电阻r12输入方波pwm3;第十三电阻r13为第六三极管q6的基极分流电阻,并联在第六三极管q6的基极与射极之间;第六电容c6是高频反馈电容,并联在第六三极管q6的基极与集电极之间,用于抑制来自opl_security_indicator_led的高频瞬态干扰和进行瞬态过压保护;第九电阻r9是限流电阻,用于限流、限功率和防接电源正损坏;第六三极管q6的集电极通过串联第九电阻r9后输出opl_security_indicator_led,用于外接高边指示灯负载;第八电容c8是防静电电容,并联在第九电阻r9输出opl_security_indicator_led的一端与电源地gnd之间;双向tvs管d1用于防脉冲和防过压,并联在第六三极管q6的集电极和射极之间;当输入lsd电路模块的pwm2为方波且pwm3为低电平或悬空时,lsd电路模块输出与方波pwm2反相位的方波opl_security_indicator_led,设vbat为外接高边指示灯负载的供电电压,rl为外接指示灯负载的等效电阻,rs为本模块的输出限流电阻,则opl_security_indicator_led的输出电压如下式所示:

[0025][0026]

opl_security_indicator_led的输出电流如下式所示:

[0027][0028]

当输入lsd电路模块的pwm3为方波且pwm2为低电平或悬空时,lsd电路模块输出与方波pwm3反相位的方波opl_security_indicator_led,opl_security_indicator_led的输出电压如下式所示:

[0029][0030]

opl_security_indicator_led的输出电流如下式所示:

[0031][0032]

当输入lsd电路模块的pwm3和pwm2都为方波时,opl_security_indicator_led的输出电压如下式所示:

[0033][0034]

opl_security_indicator_led输出电流如下式所示:

[0035][0036]

opl_security_indicator_led用于驱动外接高边指示灯负载进行静电防护、脉冲防护、接电源正防护、瞬态过压保护、过压保护、限流保护和限功率保护功能。

[0037]

一种汽车防盗指示灯控制方法,包括以下步骤:

[0038]

s1:控制电路模块休眠或电源vdd2关断后,电源vdd1处于常电状态,汽车防盗指示灯控制电路工作在自主模式,自主模式下的工作电流为0.3ma;控制电路模块的do0引脚处于悬空状态,gnd开关电路模块的do0引脚不对控制电路模块的do0引脚反灌电流;控制电路模块的pwm0引脚处于悬空状态,缓冲隔离电路模块的pwm0引脚不对控制电路模块的pwm0引脚反灌电流;缓冲隔离电路模块的pwm3引脚开路,lsd电路模块的pwm3输入为低电平;

[0039]

gnd开关电路模块的gnd-s引脚连通gnd引脚,非稳态电路模块的pwm1引脚输出高电平占空比为1.98s、周期为2s的方波,反相缓冲电路模块的pwm2引脚输出高电平占空比为0.02s、周期为2s的方波,lsd电路模块的opl引脚输出低边驱动opl_security_indicator_led驱动高边指示灯持续周期性的闪烁,闪烁特性为亮0.02s和灭1.98s,按此规律一直反复持续,直至控制电路模块被唤醒或电源vdd2开启;

[0040]

s2:电源vdd2开启或控制电路模块被唤醒正常工作后,电源vdd1处于常电状态,汽车防盗指示灯控制电路工作在被控模式,被控模式下的工作电流不大于13ma;控制电路模块的do0引脚输出高电平,gnd开关电路模块的gnd-s引脚与gnd引脚断开,非稳态电路模块的gnd-s引脚不对gnd开关电路模块的gnd-s引脚反灌电流;非稳态电路模块的pwm1引脚开路,反相缓冲电路模块的pwm1引脚不对非稳态电路模块的pwm1引脚反灌电流;反相缓冲电路模块的pwm2引脚开路,lsd电路模块的pwm2引脚不对反相缓冲电路模块的pwm2引脚反灌电流,lsd电路模块的pwm2引脚输入低电平;

[0041]

控制电路模块的pwm0引脚输出由软件控制占空比和周期的方波,缓冲隔离电路模块的pwm3引脚输出与pwm0引脚输入的相同占空比和相同周期的方波,lsd电路模块的opl引脚输出低边驱动opl_security_indicator_led驱动高边指示灯负载工作,工作特性与pwm3引脚输入的方波的特性相同,点亮时间同pwm3的高电平时间,其熄灭时间同pwm3的低电平时间。

[0042]

一种计算机存储介质,其内存储有可被计算机处理器执行的计算机程序,该计算机程序执行一种汽车防盗指示灯控制方法。

[0043]

本发明的有益效果为:

[0044]

1.本发明的一种汽车防盗指示灯控制电路及其控制方法,集成在车身控制器、仪表控制器或其它控制器中控制汽车防盗指示灯,在车主按下智能钥匙的上锁按钮后,控制器进入休眠状态,本发明电路自动开启控制防盗指示灯工作,使mcu或soc一直处于休眠状

态,实现了降低汽车防盗指示电路的功耗的功能。

[0045]

2.本发明在mcu或soc休眠或下电后自主工作,或在mcu或soc被唤醒后仍然自主工作,降低了mcu或soc的负载率;在mcu或soc被唤醒后受mcu或soc的控制,工作方式灵活;且按低功耗要求设计,本发明的自主工作电流为0.3ma,静态功耗低。

[0046]

3.本发明通过改变电路中r2和r4的值来改变输出信号的占空比,灵活设置输出占空比参数;r2、r4和c4均采用高精度器件,输出占空比精度高;主要采用分立器件和通用逻辑电路,成本低;还设置有包括emc、静电、过压、限流和隔离缓冲的保护措施,可靠性高。本发明可以集成在任何有防盗指示功能的控制器中,节约了安装空间。

[0047]

4.本发明不仅用于控制防盗指示灯,稍作修改还用于控制其它的高低边负载设备,通用性强;本发明电路可以裁剪使用,如只保留自主工作模式等,可裁剪性好;本发明可扩展驱动多个负载,如增加模块6(低边驱动),可扩展性好;本发明电路可以与其它功能电路重组应用,如模块3(反相缓冲)的输出可以和其它电路“与”运算后输出给模块6,可重组性强。

[0048]

5.本发明通用性强、功耗低、成本低、可靠性高,mcu或soc的负荷率低。

附图说明

[0049]

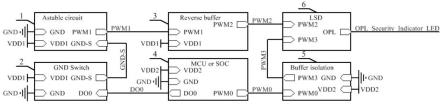

图1是本发明实施例的总电路图。

[0050]

图2是本发明实施例的模块1的电路图。

[0051]

图3是本发明实施例的模块2的电路图。

[0052]

图4是本发明实施例的模块3的电路图。

[0053]

图5是本发明实施例的模块4的电路图。

[0054]

图6是本发明实施例的模块5的电路图。

[0055]

图7是本发明实施例的模块6的电路图。

[0056]

图中:1.非稳态电路模块;2.gnd开关电路模块;3.反相缓冲电路模块;4.控制电路模块;5.缓冲隔离电路模块;6.lsd电路模块。

具体实施方式

[0057]

下面结合附图和具体实施方式对本发明作进一步详细的说明。

[0058]

参见图1,本发明的实施例包括模块1非稳态电路模块、模块2gnd开关电路模块、模块3反相缓冲电路模块、模块4(mcu或soc)控制电路模块、模块5缓冲隔离电路模块和模块6lsd电路模块。vdd1是控制器的常电电源,可以为5v或3.3v,vdd2是mcu或soc的供电电源,可以为3.3v或5v的常电电源也可以为3.3v或5v的可控电电源,“gnd”是控制器的公共地,即电源负,“opl_security_indicator_led”是低边驱动输出,外接高边指示灯负载。在mcu或sco休眠后或者mcu或soc的供电关断后,模块2的“gnd-s”连通到“gnd”,模块1的“pwm1”输出占空比为1.98s和周期为2s的方波,模块3的“pwm2”输出占空比为0.02s和周期为2s的方波,模块6的“opl_security_indicator_led”驱动高边指示灯持续周期性的闪烁,其闪烁特性为亮0.02s和灭1.98s。在mcu或sco被唤醒正常工作后,模块4的“pwm0”输出占空比和周期可软件控制的方波,模块5的“pwm3”输出与pwmo同占空比和同周期的方波,模块6的“opl_security_indicator_led”驱动高边指示灯负载工作,其工作特性同“pwm0”。

[0059]

参见图2,模块1为非稳态电路模块,vdd1为本模块的常电电源输入,可以为3.3v或5v,gnd为电源负,gnd-s为gnd开关,pwm1为方波输出;当gnd-s连通到gnd时,pwm1输出周期为2s和高电平时间为1.98s的方波,在拉电流不大于1ma时,其输出方波高电平幅度不低于(vdd1-0.3)v,在灌电流不大于2ma时,低电平幅度为不高于0.3v,输出方波的上升沿时间不大于10us,输出方波的下降沿时间不大于5us,本模块的工作电流不大于0.2ma;当gnd-s与gnd断开时,pwm1输出悬空,本模块的工作电流不大于0.01ma;vdd1对gnd去耦滤波,vdd1对gnd-s去耦滤波,控制比较器阈值对gnd-s耦滤波;方波发生器的充放电电容为不大于15uf的无极性电容。

[0060]

c1是vdd1对gnd的滤波电容,c3是vdd1对gnd-s的滤波电容,c2是u1内部阈值滤波电容,u1是通用计时器集成电路tlc555,r2、r4、c4和c5共同决定pwm1的频率和占空比特性,r2是c4和c5主充电电阻,r4是c4和c5的次充电电阻和放电电阻。当gnd-s连通到gnd时,pwm1的频率f1=1.44/[(r2+2r4)*(c4+c5)]≈0.5hz,周期为2s,pwm1的高电平占空比为d1=(r2+r4)/(r2+2r4)≈0.99,高电平时间为1.98s,pwm1的低电平幅度为0.1v,pwm1的高电平幅度为3.3v,pwm1的上升沿时间为5us,下降沿时间为3us,本模块的工作电流为0.2ma;当gnd-s与gnd断开时,pwm1输出悬空,本模块的工作电流为0.01ma。

[0061]

参见图3,模块2为gnd开关电路模块,vdd1为本模块的常电电源输入,可以为3.3v或5v,gnd为电源负,gnd-s为gnd开关,do0为控制输入;当do0输入ttl或cmos高电平时,gnd-s与gnd断开,在vdd1不大于12v时,gnd-s的灌电流不大于5ua时,本模块的工作电流不大于0.6ma;当do0输入ttl或cmos低电平时,gnd-s连通到gnd,在灌电流不大于10ma时,gnd-s的电压不大于0.1v,本模块的工作电流不大于0.2ma;当do0输入悬空时,gnd-s连通到gnd,在灌电流不大于10ma时,gnd-s的电压不大于0.1v,本模块的工作电流不大于0.2ma;抗10mhz以上的高频干扰。

[0062]

q4为输入反向缓冲npn型数字晶体管,q5为集电极开路的输入反向缓冲npn三极管,r7为q4的集电极上拉限流电阻,r8为q5的基极限流电阻,r11为q5的基极分流电阻,c7为q5的基极输入滤波电容。当do0输入(2∽3.3)v高电平时,q4饱和导通,q4-3pin输出0.1v,q5截止,q5-3pin输出开路,gnd-s与gnd断开,gnd-s的灌电流为1ua时,本模块的工作电流为0.06ma;当do0输入(0∽0.6v)低电平时,q4截止,q4-3pin输出开路,q5饱和导通,q5-3pin输出0.1v,gnd-s与gnd连通,gnd-s的灌电流为0.17ma时,本模块的工作电流为0.18ma。

[0063]

参见图4,模块3为反相缓冲电路模块,vdd1为本模块的常电电源输入,可以为3.3v或5v,pwm1为来自模块1的方波输入,pwm2为本模块的方波输出;当pwm1输入方波时,pwm2输出与pwm1反相位的方波,在拉电流不大于10ma时,其输出方波高电平幅度不低于(vdd1-0.1)v,其消耗电流不大于0.6ma;在下拉10kω负载的条件下,其输出方波低电平幅度为不高于0.1v时,如果不接下拉负载,其输出漏电流不大于5ua的开路,其消耗电流不大于0.01ma;pwm2相对于pwm1的时延不大于1us,pwm2的上升沿时间不大于10us,pwm2的下降沿时间不大于5us;当pwm1输入开路时,pwm2输出开路,其消耗电流不大于3ua。

[0064]

q1为输入反向缓冲三极管,r1为q1的基极分流电阻,r3为q1的基极限流电阻;当pwm1输入方波时,pwm2输出与pwm1反相位的方波,pwm2的频率同pwm1为0.5hz,周期为2s,pwm2的高电平占空比为d1=1-0.99=0.1,高电平时间为0.02s,pwm2的低电平幅度为0.1v,pwm2的高电平幅度为3.3v,pwm2的上升沿时间为5us,下降沿时间为3us,pwm2相对于pwm1的

时延为1ns,本模块的工作电流为3ua;当pwm1输入开路时,pwm2输出开路,本模块的工作电流为1ua。

[0065]

参见图5,模块4为控制电路模块,vdd2是mcu或soc的供电电源,可以为3.3v或5v的常电电源,可以和vdd1为同一个电源,也可以为3.3v或5v的可控电源,“gnd”是电源负;pwm0为pwm输出,其输出频率为0.1hz~10hz可调,输出占空比为0%~100%可调,其输出上升沿时间不大于10us,其输出下降沿时间不大于5us,do0为数字输出,do0和pwm0的输出电压满足ttl或cmos规范,do0和pwm0的最大拉电流不小于1ma,最大灌电流不小于2ma;如果vdd2为常电,mcu或soc需具备低功耗模式,其低功耗电流不大于0.2ma,如果vdd2为可控电,mcu或soc可以不用具备低功耗模式,mcu或soc可以与其它电路共用。

[0066]

本实例采用国产soc(g9s),在正常工作模式,pwm0的输出频率为0.2hz,输出占空比为0.4%,其输出上升沿时间为5us,输出下降沿时间为3us,其高电平拉电流为0.3ma,低电平灌电流为70ua,do0输出3.3v,其拉电流为0.3ma;在低功耗模式,vdd2输出0v,其灌电流为2ua,pwm0输出开路,其灌电流为3ua,do0输出开路,其灌电流为3ua。

[0067]

参见图6,模块5为缓冲隔离电路模块,vdd2是mcu或soc的供电电源,可以为3.3v或5v的常电电源也可以为3.3v或5v的可控电电源,gnd为电源负,pwm0为来自模块4的方波输入,pwm3为本模块的方波输出;当pwm0输入方波时,pwm3输出与pwm0同相位的方波,在拉电流不大于10ma时,其输出方波高电平幅度不低于(vdd1-0.1)v,其消耗电流不大于0.7ma;在下拉10kω负载的条件下,其输出方波低电平幅度为不高于0.1v时,如果不接下拉负载,其输出漏电流不大于5ua的开路,其消耗电流不大于0.01ma;pwm3相对于pwm0的时延不大于1us,pwm3的上升沿时间不大于10us,pwm3的下降沿时间不大于5us;当pwm0输入开路时,pwm3输出开路,其消耗电流不大于3ua。

[0068]

q2为输入反向缓冲的npn型数字晶体管,q3为集电极开路的输入反向缓冲pnp三极管,r5为q3的基极限流电阻,r6为q3的基极分流电阻;当pwm0输入方波时,pwm3输出与pwm0同相位的方波,其输出方波高电平幅度为3.3v,其消耗电流不大于0.67ma,其输出方波低电平幅度为0v时,其消耗电流为1ua,pwm3相对于pwm0的时延为1us,pwm3的上升沿时间为5us,pwm3的下降沿时间为5us,当pwm0输入悬空时,pwm3输出悬空,其消耗电流为1ua。

[0069]

参见图7,模块6为lsd电路模块,pwm2为来自模块3的方波输入,pwm3为来自模块5的方波输入,opl_security_indicator_led是本模块的输出,外接高边指示灯负载。q2为输入反向驱动的npn型三极管,r10和r12为q2的基极限流电阻,r13为q2的基极分流电阻,c6是高频反馈电容,可以抑制来自opl_security_indicator_led的高频瞬态干扰,也能起瞬态过压保护的作用,c1是防静电电容,d1是防脉冲和防过压的tvs,r9是限流电阻,可以起限流、限功率和防接电源正损坏的作用。

[0070]

当pwm2输入方波和pwm3输入低电平(悬空)时,opl_security_indicator_led输出与pwm2反相位的方波,opl_security_indicator_led输出电压如下式所示:

[0071][0072]

opl_security_indicator_led输出电流如下式所示:

[0073][0074]

vbat为外接高边指示灯负载的供电电压,rl为外接指示灯负载的等效电阻,rs为本模块的输出限流电阻。

[0075]

仅当pwm3输入方波和pwm2输入低电平(悬空)时,opl_security_indicator_led输出与pwm3反相位的方波,opl_security_indicator_led输出电压如下式所示:

[0076][0077]

opl_security_indicator_led输出电流如下式所示:

[0078][0079]

当pwm3和pwm2都输入方波时,opl_security_indicator_led输出电压如下式所示:

[0080][0081]

opl_security_indicator_led输出电流如下式所示:

[0082][0083]

opl_security_indicator_led输出具有静电防护、脉冲防护、接电源正防护、瞬态过压保护、过压保护、限流保护和限功率保护功能等功能。

[0084]

本实施例中,opl_security_indicator_led输出电压如下式所示:

[0085][0086]

opl_security_indicator_led输出电流如下式所示:

[0087][0088]

opl_security_indicator_led输出电压如下式所示:

[0089][0090]

opl_security_indicator_led输出电流如下式所示:

[0091][0092]

本发明的替代方案1为采用mosfet替代三极管;替代方案2为采用不同参数的元器件;替代方案3为采用不同的控制参数。

[0093]

本发明的控制方法,包括以下步骤:

[0094]

mcu或soc休眠后或者vdd2关断后,vdd1处于常电状态,汽车防盗指示灯控制电路工作在自主模式,模块4(mcu或soc)的do0输出悬空状态,模块2的doo不对模块4的do0反灌电流(本实施例中反灌电流小于1ua),模块4(mcu或soc)的pwm0输出悬空状态,模块5的pwm0不对模块4的pwm0反灌电流(本实施例中反灌电流小于1ua)。模块5的pwm3输出开路,模块6的pwm3输入为低电平。模块2的gnd-s与gnd连通,pwm1输出高电平占空比为1.98s和周期为2s的方波,模块3的pwm2输出高电平占空比为0.02s和周期为2s的方波,模块3采用pnp型三极管做反相和缓冲隔离,用于避免模块3在pwm1输出的1.98s的高电平区间消耗电流,模块6的opl_security_indicator_led输出驱动外部的防盗指示灯亮0.02s和灭1.98s,按此规律一直反复持续,直至mcu或soc被唤醒或者vdd2开启,模块6采用npn型三极管做反相和功率放大,用于避免模块6在pwm2输出的1.98s的低电平区间消耗电流,自主模式下的汽车防盗指示灯控制电路的工作电流为0.3ma。

[0095]

mcu或soc被唤醒后或者vdd2开启后,vdd1处于常电状态,汽车防盗指示灯控制电路工作在被控模式,模块4(mcu或soc)的do0输出高电平,模块2的gnd-s与gnd断开,模块1的gnd-s不对模块2的gnd-s反灌电流(本实施例中反灌电流小于1ua),模块1的pwm1输出开路,模块3的pwm1不对模块1的pwm1反灌电流(本实施例中反灌电流小于1ua),模块3的pwm2输出开路,模块6的pwm2不对模块3的pwm2反灌电流(本实施例中反灌电流小于1ua),模块6的pwm2输入为低电平。模块4(mcu或soc)的pwm0输出pwm信号,pwm0的占空比和周期由软件控制(本实施例中pwm0的高电平占空比为0.4%和周期为5s),模块5的pwm3输出与pwm0同相位和同周期的pwm信号,模块6的opl_security_indicator_led输出驱动外部的防盗指示灯亮灭,其点亮时间同pwm3的高电平时间(本实施例中为20ms),其熄灭时间同pwm3的低电平时间(本实施例中为4.98s),被控模式下的汽车防盗指示灯控制电路的工作电流不大于13ma(本实施例中为0.12ma)。

[0096]

以上实施例仅用于说明本发明的设计思想和特点,其目的在于使本领域内的技术人员能够了解本发明的内容并据以实施,本发明的保护范围不限于上述实施例。所以,凡依据本发明所揭示的原理、设计思路所作的等同变化或修饰,均在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1