半导体器件及其制造方法与流程

本发明涉及一种半导体器件,并且更具体地,涉及一种包括三维存储单元的半导体器件及其制造方法。

背景技术:

1、二维半导体存储器件的集成度主要由存储单元所占据的面积来确定。因此,集成度极大地受到精细图案制造技术水平的影响。二维半导体存储器件的集成度仍在提高,但由于制造更精细的图案需要非常昂贵的工具,因此所述提高是有限的。因此,已经提出了具有三维布置的存储单元的三维(3d)半导体存储器件。

技术实现思路

1、本发明公开的实施例提供了一种3d高度集成的存储单元以及包括该高度集成的存储单元的3d半导体存储器件。

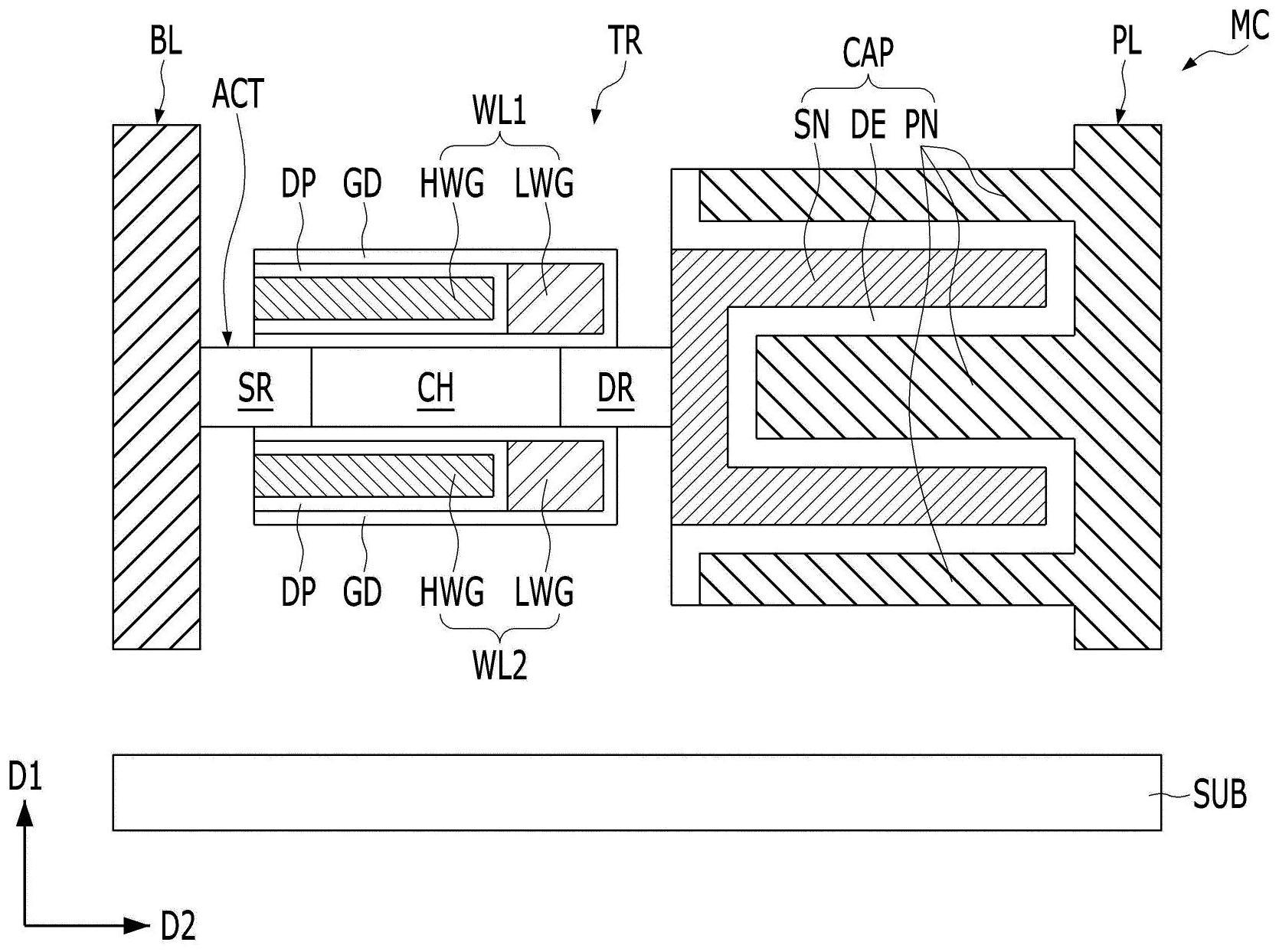

2、根据本发明的实施例,一种半导体器件包括:有源层,该有源层包括沟道,该有源层与衬底间隔开并且在与衬底的表面平行的方向上延伸;栅极电介质层,该栅极电介质层形成在有源层之上;字线,该字线在与有源层交叉的方向上被横向定向、位于栅极电介质层之上,并且该字线包括低功函数电极和高功函数电极,该高功函数电极具有比低功函数电极高的功函数;以及偶极子诱导层(dipole inducing layer),该偶极子诱导层设置在高功函数电极与栅极电介质层之间。

3、根据本发明的实施例,一种制造半导体器件的方法,该方法包括:在衬底上形成有源层,该有源层与衬底竖向间隔开;在有源层之上形成栅极电介质层;在栅极电介质层之上形成低功函数电极;在低功函数电极的一侧上且在栅极电介质层之上形成偶极子诱导层;以及在偶极子诱导层之上形成高功函数电极,该高功函数电极具有比低功函数电极高的功函数。

4、根据本发明的实施例,一种制造半导体器件的方法,该方法包括:形成叠置件本体,在所述叠置件本体中第一层间电介质层、第一牺牲层、有源层、第二牺牲层以及第二层间电介质层被顺序地叠置;形成贯穿所述叠置件本体的开口;通过穿过所述开口去除所述第一牺牲层和所述第二牺牲层来形成凹陷;在由所述凹陷暴露的所述有源层之上形成栅极电介质层;在所述栅极电介质层之上形成部分地填充所述凹陷的低功函数电极;在所述低功函数电极的一侧上且在所述栅极电介质层之上形成偶极子诱导层;以及形成高功函数电极,所述高功函数电极填充所述凹陷的剩余部分、位于所述偶极子诱导层之上,并且具有比所述低功函数电极高的功函数。

5、根据本发明的一个实施例,一种半导体器件可以包括:有源层,该有源层与衬底间隔开,其中有源层在平行于衬底的方向上延伸并且包括沟道;位线,该位线在垂直于衬底的方向上延伸并且耦接到有源层的第一端部;电容器,该电容器耦接到有源层的第二端部;以及字线结构,该字线结构在与有源层交叉的方向上延伸,其中,字线结构可以包括与位线相邻的高功函数电极;低功函数电极,该低功函数电极与电容器相邻并且具有比高功函数电极低的功函数;以及偶极子诱导层,该偶极子诱导层设置在高功函数电极与低功函数电极之间。

6、本发明可以通过在高功函数电极与栅极电介质层之间形成偶极子诱导层来使用平带移位而增大单元阈值电压。

7、由于字线具有低功函数电极和高功函数电极的双功函数电极,因此本发明可以在确保存储单元的刷新特性的同时实现低功耗。

技术特征:

1.一种半导体器件,包括:

2.如权利要求1所述的半导体器件,

3.如权利要求1所述的半导体器件,其中,所述偶极子诱导层包括具有比所述栅极电介质层高的氧原子面密度的材料。

4.如权利要求1所述的半导体器件,其中,所述偶极子诱导层包括氧化铝或氧化铪。

5.如权利要求1所述的半导体器件,其中,所述低功函数电极和所述高功函数电极在与所述有源层交叉的方向上彼此平行地延伸。

6.如权利要求1所述的半导体器件,其中,所述低功函数电极包括掺杂有n型杂质的多晶硅。

7.如权利要求1所述的半导体器件,其中,所述高功函数电极包括金属基材料。

8.如权利要求1所述的半导体器件,其中,所述高功函数电极包括氮化钛、钨、或者氮化钛和钨的叠置件。

9.如权利要求1所述的半导体器件,其中,所述有源层包括半导体材料或氧化物半导体材料。

10.如权利要求1所述的半导体器件,其中,所述有源层包括多晶硅、单晶硅、锗、硅锗、或铟镓锌氧化物。

11.如权利要求1所述的半导体器件,其中,所述栅极电介质层包括氧化硅、氮化硅、金属氧化物、金属氧氮化物、金属硅酸盐、高k材料、铁电材料、反铁电材料、或它们的组合。

12.如权利要求1所述的半导体器件,

13.如权利要求12所述的半导体器件,还包括:

14.如权利要求1所述的半导体器件,其中,所述字线包括双字线、单字线、或环栅字线。

15.如权利要求1所述的半导体器件,其中,所述栅极电介质层具有覆盖所述偶极子诱导层和所述低功函数电极的形状。

16.一种制造半导体器件的方法,所述方法包括:

17.如权利要求16所述的方法,其中,所述偶极子诱导层包括具有比所述栅极电介质层高的氧原子面密度的材料。

18.如权利要求16所述的方法,其中,所述偶极子诱导层包括氧化铝或氧化铪。

19.如权利要求16所述的方法,其中,所述低功函数电极包括掺杂有n型杂质的多晶硅。

20.如权利要求16所述的方法,其中,所述高功函数电极包括氮化钛、钨、或者氮化钛和钨的叠置件。

21.如权利要求16所述的方法,还包括:

22.一种制造半导体器件的方法,所述方法包括:

23.如权利要求22所述的方法,还包括:

技术总结

提供一种半导体器件及其制造方法。本发明涉及高度集成的存储单元以及包括该存储单元的半导体器件。根据本发明的实施例,半导体器件包括:有源层,该有源层包括沟道,该有源层与衬底间隔开并且在与衬底的表面平行的方向上延伸;栅极电介质层,该栅极电介质层形成在有源层之上;字线,该字线在与有源层交叉的方向上被横向定向、位于栅极电介质层之上,并且该字线包括低功函数电极和高功函数电极,该高功函数电极具有比低功函数电极高的功函数;以及偶极子诱导层,该偶极子诱导层设置在高功函数电极与栅极电介质层之间。

技术研发人员:金俊植

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!