电平转换电路和电子装置

本公开的实施例涉及一种电平转换电路和电子装置。

背景技术:

1、随着芯片技术的迅速发展以及人们对低功耗芯片需求的增加,越来越多的电子系统趋向于引入低电压信号。出于提高系统速度和降低功耗等多方面的考虑,很多电子系统中存在两个或更多的电压域,例如模拟电压域和数字电压域等。为解决信号在不同电压域之间交互时的逻辑不协调问题,需要使用电平转换电路对不同电压域之间的信号进行电平转换。

2、信号从高电压域到低电压域的转换通常是比较容易实现的,但是从低电压域到高电压域的转换则较为复杂,电平转换电路的设计难度也较大。传统的电平转换电路在将低电压电平的输入信号转换成高电压电平的输出信号时存在上拉延迟高、转换速度慢等问题,成为了制约电路速度的主要因素之一。

技术实现思路

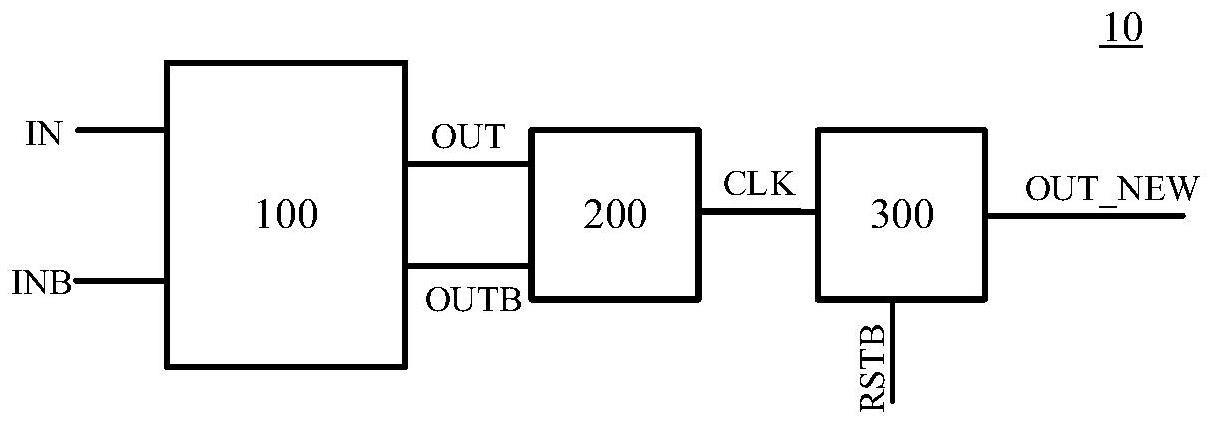

1、本公开至少一实施例提供一种电平转换电路,该电平转换电路包括:电平转换单元,包括接收第一输入信号和与所述第一输入信号反相的第二输入信号的输入单元,以及输出第一输出信号和与所述第一输出信号反相的第二输出信号的输出单元;或非逻辑单元,对从所述电平转换单元接收的所述第一输出信号和所述第二输出信号执行或非逻辑运算,并输出第一中间信号;电平翻转单元,根据所述或非逻辑单元输出的所述第一中间信号输出相对于所述第一中间信号翻转的第三输出信号。

2、例如,在本公开至少一实施例提供的电平转换电路中,所述输入单元包括接收所述第一输入信号的第一晶体管、接收所述第二输入信号的第二晶体管以及与所述第一晶体管和所述第二晶体管电连接并提供第一电压的第一电源端,所述输出单元包括输出所述第一输出信号的第三晶体管、输出所述第二输出信号的第四晶体管以及与所述第三晶体管和所述第四晶体管电连接并提供第二电压的第二电源端。

3、例如,在本公开至少一实施例提供的电平转换电路中,所述第一电压小于所述第二电压。

4、例如,在本公开至少一实施例提供的电平转换电路中,所述或非逻辑单元包括或非门电路。

5、例如,在本公开至少一实施例提供的电平转换电路中,所述电平翻转单元的时钟控制端接收所述第一中间信号。

6、例如,在本公开至少一实施例提供的电平转换电路中,所述电平翻转单元包括时钟触发器。

7、例如,在本公开至少一实施例提供的电平转换电路中,所述时钟触发器

8、ˉ

9、包括t=1的t触发器、d与q电连接的d触发器、j=k=1的jk触发器或

10、ˉ

11、r与q电连接且s与q电连接的rs触发器。

12、例如,在本公开至少一实施例提供的电平转换电路中,所述电平翻转单元包括清零端,所述清零端接收清零信号以执行清零操作。

13、例如,在本公开至少一实施例提供的电平转换电路中,所述清零操作包括设置清零信号为0,以使得所述第三输出信号的初始电平为0。

14、本公开至少一实施例还提供一种电子装置,该电子装置包括本公开任一实施例所述的电平转换电路。

技术特征:

1.一种电平转换电路,包括:

2.根据权利要求1所述的电平转换电路,其中,所述输入单元包括接收所述第一输入信号的第一晶体管、接收所述第二输入信号的第二晶体管以及与所述第一晶体管和所述第二晶体管电连接并提供第一电压的第一电源端,所述输出单元包括输出所述第一输出信号的第三晶体管、输出所述第二输出信号的第四晶体管以及与所述第三晶体管和所述第四晶体管电连接并提供第二电压的第二电源端。

3.根据权利要求2所述的电平转换电路,其中,所述第一电压小于所述第二电压。

4.根据权利要求1所述的电平转换电路,其中,所述或非逻辑单元包括或非门电路。

5.根据权利要求1所述的电平转换电路,其中,所述电平翻转单元的时钟控制端接收所述第一中间信号。

6.根据权利要求1或5所述的电平转换电路,其中,所述电平翻转单元包括时钟触发器。

7.根据权利要求6所述的电平转换电路,其中,所述时钟触发器包括t=1的t触发器、d与电连接的d触发器、j=k=1的jk触发器或r与q电连接且s与电连接的rs触发器。

8.根据权利要求6所述的电平转换电路,其中,所述电平翻转单元包括清零端,所述清零端接收清零信号以执行清零操作。

9.根据权利要求8所述的电平转换电路,其中,所述清零操作包括设置清零信号为0,以使得所述第三输出信号的初始电平为0。

10.一种电子装置,包括根据权利要求1-9所述的电平转换电路。

技术总结

一种电平转换电路和电子装置。该电平转换电路包括电平转换单元、或非逻辑单元和电平翻转单元。电平转换单元包括输入单元和输出单元,输入单元接收第一输入信号和与第一输入信号反相的第二输入信号,输出单元输出第一输出信号和与第一输出信号反相的第二输出信号;或非逻辑单元对从电平转换单元接收的第一输出信号和第二输出信号执行或非逻辑运算,并输出第一中间信号;电平翻转单元根据或非逻辑单元输出的第一中间信号输出相对于第一中间信号翻转的第三输出信号。该电平转换电路能够减小输出信号的上拉延迟,提高电平转换速度。

技术研发人员:吴华强,何源,唐建石,高滨,钱鹤

受保护的技术使用者:清华大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!