高性能锁相环的制作方法

shokrollahi,名称为“带内嵌时钟的正交差分向量信令码”的美国专利申请,下称《holden 2》;

16.申请号为14/926,958,申请日为2015年10月29日,发明人为richard simpson,andrew stewart及ali hormati,名称为“用于向量信令码通信链路的时钟数据对齐系统”的美国专利申请,下称《stewart 1》;

17.申请号为14/925,686,申请日为2015年10月28日,发明人为armin tajalli,名称为“改进式相位插值器”的美国专利申请,下称《tajalli 2》;

18.申请号为62/286,717,申请日为2016年1月25日,发明人为armin tajalli,名称为“高频增益改善型电压采样驱动器”的美国临时专利申请,下称《tajalli 3》。

19.此外,本技术中还引用以下现有技术参考文献:

20.专利号为6,509,773,申请日为2001年4月30日,发明人为buchwald等人,名称为“相位插值器装置和方法”的美国专利,下称《buchwald》;

[0021]“采用两相锁存器的线性相位检测”,a.tajalli等人,iee电子学快报(iee electronics letters),2003年,下称《tajalli 4》;

[0022]“带65纳米cmos技术自对准dll的低抖动低相位噪声10ghz亚谐波注入锁定锁相环”,hong-yeh chang、yen-liang yeh、yu-cheng liu、meng-han li及kevin chen,ieee微波理论与技术汇刊,第62卷,第3期,2014年3月,第543~555页,下称《chang等人》;

[0023]“用于fmcw雷达的带基于延迟锁定环的参考倍频器的低相位噪声77ghz小数n分频锁相环”,herman jalli ng、rainer stuhlberger、linus maurer、thomas sailer及andreas stelzer,第6届欧洲微波集成电路会议论文集,2011年10月10日~11日,第196~199页,下称《ng等人》;

[0024]“采用带宽自适应性混合pll/dll的高噪声稳健性时钟数据恢复设计”,han-yuan tan,2006年11月哈佛大学博士论文,下称《tan》。

技术领域

[0025]

本发明实施方式总体涉及通信系统电路,尤其涉及通过用于芯片间通信的高速多线接口获得相位正确的稳定接收器时钟信号。

背景技术:

[0026]

在现代数字系统中,必须以高效可靠的方式进行数字信息处理。在此背景下,须将数字信息理解为含于离散值(即非连续值)内的信息。数字信息不但可由比特和比特集合表示,而且还可由有限集合内的数字表示。

[0027]

为了提高总带宽,大多数芯片间或装置间通信系统采用多条线路进行通信。这些线路当中的每一条或每一对均称为信道或链路,而且多个信道组成电子部件之间的通信总线。在物理电路层级上,芯片间通信系统内的总线通常由芯片与主板之间的封装电导体、印刷电路板(pcb)上的封装电导体、或pcb间线缆和连接器内的封装电导体构成。此外,高频应用中,还可采用微带或带状pcb线路。

[0028]

常用总线线路信号传输方法包括单端信令法和差分信令法。在要求高速通信的应用中,这些方法还可以在功耗和引脚利用率方面(尤其高速通信中的这些方面)进行进一步

优化。最近提出的向量信令法可在芯片间通信系统的功耗、引脚利用率及噪声稳健性方面实现更加优化的权衡取舍。此类向量信令系统将发射器端的数字信息转换为向量码字形式的不同的表示空间,并且根据传输信道的特性和通信系统的设计约束选择不同的向量码字,以在功耗、引脚利用率及速度之间做出更优的权衡取舍。这一过程在本技术中称为“编码”。编码后的码字以一组信号的形式从发射器发送至一个或多个接收器。在接收器端,将所接收的与码字对应的信号转换回最初的数字信息表示空间。这一过程在本技术中称为“解码”。

[0029]

无论何种编码方法,均须对接收装置所接收的信号进行间隔采样(或者以其他方式记录其信号值),而且无论传输信道的延迟、干扰及噪声条件如何,该采样间隔均须使得采样值能够以最佳方式表示最初的发送值。这一时钟数据恢复(cdr)过程不仅须确定出合适的采样时序,而且可能需要一直不停地进行该确定步骤,以实现不同信号传播条件的动态补偿。

[0030]

许多已知的cdr系统采用锁相环(pll)或延迟锁定环(dll)合成具有适于实现精确接收数据采样的频率和相位的本地接收时钟。

技术实现要素:

[0031]

为了对经通信系统发送的数据值进行可靠地检测,接收器必须能够在精心选择的时间点上精确测量接收信号值的幅度。目前,已有各种可促进此类接收测量的已知方法,包括接收与发送数据流相关的一个或多个专用时钟信号的方法,从发送数据流中提取内嵌时钟信号的方法,以及根据发送数据流的已知属性合成本地接收时钟的方法。

[0032]

一般而言,此类定时方法的接收器端实施方式称为时钟数据恢复(cdr),并且通常利用锁相环(pll)或延迟锁定环(dll)合成具有所需频率和相位特征的本地接收时钟。

[0033]

在各pll和dll实施方式中,通过相位比较器对接收参考信号和本地时钟信号的相对相位(在某些变形实施方式中,比较其相对频率)进行比较以生成误差信号,然后利用该误差信号对本地时钟源的相位和/或频率进行校正,从而最大程度地减小误差。由于该反馈环路行为将导致给定的pll实施方式在所述参考信号与本地时钟之间产生固定的相位关系(例如,0度或90度的相位偏移),因此还通常通过引入额外的固定或可变相位调整量而将该相位偏移设定至与上述值不同的目标值(如45度的相位偏移),以促进接收器的数据检测。

[0034]

在下述方法和系统中:接收n个本地时钟信号相位和m个参考信号相位,其中,m为大于或等于1的整数,n为大于或等于2的整数;生成多个部分相位误差信号,每一个部分相位误差信号均至少部分通过将(i)所述m个参考信号相位当中的相应相位与(ii)所述n个本地时钟信号相位当中的相应相位相比较而形成;通过将所述多个部分相位误差信号相加以生成复合相位误差信号;并且利用所述复合相位误差信号以响应方式调整本地振荡器的固定相位。

[0035]

在一些实施方式中,m=1,而且通过将n个部分相位误差信号相加以生成所述复合相位误差信号。或者,所述多个部分相位误差信号包括m=n个部分相位误差信号,并且利用所述n个本地时钟信号相位当中的给定相位以及所述m个参考信号相位当中的给定相位生成单个部分相位误差信号。在其他替代实施方式中,所述多个部分相位误差信号包括m

×

n个部分相位误差信号,并且将所述n个本地时钟信号相位当中的每一个相位均与所述m个参

考信号相位当中的每一个相位进行比较。

[0036]

在一些实施方式中,所述多个部分相位误差信号当中的每一个部分相位误差信号上均施加有相应的权重值。在一些实施方式中,根据m

×

n矩阵,选择所述加权值。

[0037]

在一些实施方式中,所述m个参考信号相位接收自对输入参考信号进行处理的延迟锁定环。

[0038]

在一些实施方式中,所述n个本地时钟信号相位当中的至少一个由对本地振荡器信号和相位偏移信号进行处理的相位插值器生成。在一些实施方式中,所述n个本地时钟信号相位当中的至少一个的生成包括:通过使用所述相位插值器内的4个差分对插入4个相位,其中,该4个相位当中的每一个均根据与可独立调节的电流源相连的相应差分对插入。

[0039]

在一些实施方式中,至少一个部分相位误差信号由一对触发器形成,其中,所述m个参考信号相位当中的给定相位对所述一对触发器中的第一触发器进行钟控,所述n个本地时钟信号相位当中的给定相位对第二触发器进行钟控。

[0040]

在一些实施方式中,每一部分相位误差信号均为由相应电荷泵生成的模拟信号,该相应电荷泵接收相应电荷泵控制信号,所述相应电荷泵控制信号为根据所述m个参考信号相位当中的相应相位与所述n个本地时钟信号相位当中的相应相位之间的相应比较而生成的。

[0041]

在本技术中描述的实施方式中,通过将上述相位检测元件与上述相位调整元件相结合,降低了电路节点电容及电路延迟,从而提高了环路稳定性及pll锁定特性,其中包括通过提高环路锁定带宽而降低时钟抖动和提高电源噪声抑制。

[0042]

在本技术中描述的其他实施方式中,通过dll将所述接收参考时钟信号转换为多个参考时钟相位,从而将pll的相位比较运算转换为参考时钟相位与本地时钟相位之间的多项比较,并在随后将该多项比较结果的和或加权和用作pll的误差反馈信号。在本技术中描述的另一实施方式中,在单个接收参考时钟相位与多个本地时钟相位之间进行多项比较,并将该多项比较结果的加权和用作pll的误差反馈项。在至少一种此类其他实施方式中,所述加权和包括二维时域滤波器。

附图说明

[0043]

图1为一种能够在八线通信信道上编码和发送五个数据比特及一个时钟的实施方式框图。

[0044]

图2为一种与图1发射器兼容的接收器实施方式框图。

[0045]

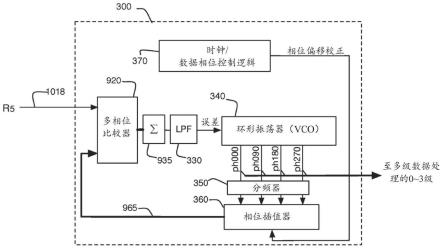

图3为一种图2接收器所使用的时钟恢复电路的实施方式框图。

[0046]

图4a、图4b和图4c所示为适用于时钟恢复电路的锁相环元件的三种相位比较器实施方式。

[0047]

图5为一种集成了xor相位比较器和时钟相位插值器的实施方式示意图。

[0048]

图6a为钟控数据锁存器示意图;图6b为集成了时钟相位插值器的另一钟控数据锁存器的实施方式示意图。

[0049]

图7a和图7b为集成了状态机相位比较器和时钟相位插值器的实施方式示意图。

[0050]

图8为一种适于进一步与相位比较器实施方式集成的电荷泵实施方式示意图。

[0051]

图9为将多个参考时钟相位与多个本地时钟相位相比较的另一实施方式框图。

[0052]

图10为在单个参考时钟与多个本地时钟相位之间进行多项比较的另一实施方式的框图。

[0053]

图11a为根据一些实施方式的加权xor相位比较器。

[0054]

图11b为一种m个参考相位与n个本地时钟相位的矩阵相位比较的实施方式框图。

[0055]

图12a和图12b为图5所示集成了相位比较器和相位插值器的一种替代实施方式框图。

[0056]

图13a为根据一些实施方式的折叠式相位比较器的时序图。

[0057]

图13b为根据一些实施方式的反向削波效应时序图。

[0058]

图14a和图14b分别为根据一些实施方式的阵列xor相位比较器和单xor相位比较器的时序图。

[0059]

图15为根据一些实施方式的方法流程图。

具体实施方式

[0060]

如《cronie 1》、《cronie 2》、《cronie 3》及《cronie 4》中所描述的,可通过向量信令码例如在系统内的两个集成电路装置之间形成极高带宽的数据通信链路。如图1实施方式所示,经多个数据通信信道发送向量信令码符号,共同作用以发送该向量信令码的码字。根据所使用的具体向量信令码的不同,组成通信链路的信道数目少至两条,多至八条或八条以上,并且可在不同的通信信道上发送一个或多个时钟信号,或者将该时钟信号作为向量信令码的子信道分量进行发送。在图1实施例中,图示通信链路120由八条线路125构成,这些线路共同在发射器110和接收器130之间传输五个数据值100和一个时钟信号105。

[0061]

各个符号(例如在任何单条通信信道中传输的各符号)可使用多个信号电平(通常为3个或3个以上电平)。当以10gbps以上的信道速率运行时,需要深度的流水线式或并行式信号处理,从而使得接收行进一步复杂化,并使得先前接收值即为当前接收值的已知接收方法变得无法使用。

[0062]

本技术中描述的实施方式还可应用于《cronie 2》、《cronie 3》、《cronie 4》和/或《tajalli 1》所述向量处理方法未涵盖的现有排列组合排序法。更一般而言,这些实施方式可应用于任何需要通过多个信道或信道元件的相互协调而生成连贯一致的总结果的通信或存储方法中。

[0063]

接收器数据检测

[0064]

以下,以《stewart 1》中的典型高速接收器实施方式为背景描述各实施例,该实施方式仅用于说明目的,不构成限制。

[0065]

如图2所示,该例示数据接收器包括八个相同的连续时间线性均衡(ctle)处理级210,用于对之前在图1中示为120的八条线路所接收的信号进行处理。

[0066]

如在《tajalli 1》、《holden 1》和《ulrich 1》中所描述的,可通过以多输入比较器(mic)或混频器对各组输入信号进行线性组合的方式,实现向量信令码的高效检测。对于上述例示接收器所使用的5b6w码而言,通过以五个此类混频器对六个接收输入数据信号的加权子集进行处理,可实现五个数据比特的检测,无需进一步的解码。此外,类似地,通过以额外的一个混频器对两个接收时钟信号的组合进行处理,可实现时钟信号检测。在图2中,通过上述一组六个mic混频器220对接收后的均衡化的信号进行处理,可生成六个所检测出的

信号mic0~mic5。

[0067]

由于涉及高数据速率,因此可在所述例示接收器中使用多个并行接收处理级。在一种实施方式中,以四个并行接收数据处理级对所检测出的五个数据信号mic0~mic4进行处理,每一级230均包括五个数据采样器及下游的缓冲器。随后,将该四个级的输出重新组合为接收数据流,在图2所示情形中,由多路复用器240实施这一重新组合过程。

[0068]

时钟恢复电路(在本领域中也称为时钟数据恢复或cdr)通过从数据线本身,或者从专用时钟信号输入中提取时序信息的方式支持上述采样测量,并且利用所提取的信息生成时钟信号,以对数据线采样装置所使用的时间间隔进行控制。实际的时钟提取操作可由锁相环(pll)或延迟锁定环(dll)等众所周知的电路完成,这些电路在操作过程中还可生成更高频率的内部时钟、多个时钟相位等,以支持接收器的操作。在图2实施方式中,所检测出的时钟信号由mic5获得,然后经处理300而为所述四个数据处理级提取出时序正确的采样时钟。

[0069]

锁相环概述

[0070]

现有文献已对锁相环(pll)进行了详尽的描述。典型的pll由将外部参考信号与内部时钟信号相比较的相位比较器,通过将所得误差值平滑化而生成钟控信号的低通滤波器,以及由平滑后的误差值控制并生成供所述相位比较器处理的上述内部时钟信号的可变频率时钟源(一般为压控振荡器(vco))组成。在该pll设计的一种众所周知的变形形式中,还可以在vco和相位比较器之间设置时钟分频器,用于将更高频率的时钟输出锁相至低频参考信号。

[0071]

在一种替代实施方式中,所述可变频率时钟源由可变延迟元件代替,从而使得其输出(可选为多个抽头输出)表示原始输入信号的一个或多个相继的时间延迟形式,而非待与参考输入信号进行相位比较的相继振荡器周期。出于本技术的目的,在此类应用,尤其在相位比较器、相位插值器及电荷泵的这些构成元件相关时,将延迟锁定环(dll)视为与pll具有同等功能。

[0072]

本领域已有为人所知的多种形式的相位比较器。作为非限制性的一例,图4a所示的简易xor(异或)门可用于对两个方波信号进行比较。熟悉本领域的技术人员可以看出的是,此类数字xor输出为一种可变占空比的波形,当两个输入信号具有90度相位偏移关系时,该波形在低通滤波为模拟误差信号后,可生成以其模拟信号范围的中心为中心的比例误差信号。

[0073]

图4b所示为结构更为复杂的状态机相位比较器,该比较器由两个边沿触发锁存器构成,这两个锁存器分别由所述参考时钟信号和内部时钟信号进行钟控,其中,第一接收时钟边沿使得“前”“后”两个输出端当中的一者开始产生输出信号,一旦这两个输出端当中的任何一者开始输出信号,各锁存器便随即复位,以等待下一比较时间间隔。在其他的实施方式中,可在所述重置路径中设置时序延迟,以实现额外的复位脉冲时序控制。一般而言,所述“前”“后”两个相位比较输出分别作为电荷泵的“上升”和“下降”两个输入,该电荷泵的输出为上述模拟误差值。也就是说,上升信号可导通对电容器进行充电的第一晶体管电路,从而提高所述模拟电压;而下降信号可导通使电容器放电的第二晶体管电路,从而降低所述电压。因此,当所述两个输入时钟信号之间的相位偏移为0度时,所述模拟误差值将保持不变,并使得锁相环处于稳定的锁定状态。本领域中已有多种为人所知的同等状态机相位比

较器实现形式,这些实现形式可同等地应用于在本技术中,但这并不意味着对本发明限制。一些状态机实施方式可能对所述输入信号之间的相位差异和频率差异均较为敏感,从而有助于在启动时更加快速地实现pll的锁定状态。

[0074]

如图4c所示,也可将单个边沿钟控d触发器用作相位比较器。在本地时钟的每一上升沿(ckpll),d输入端均对参考输入(ckref)的状态(在本例中为方波)进行采样。如果其状态为“高”(例如其已经历跃迁),则q输出端也为“高”,表明该参考信号为“前”;如果其状态为“低”(例如其未经历跃迁),则q输出端也为“低”,表明该参考信号为“后”。与上例相比,这种所谓的二进制(bang-bang)相位比较器所提供的误差结果中的细微差别更小,从而可进行更高水平的滤波,以实现环路稳定性。

[0075]

熟悉本领域的技术人员可意识到的是,无论pll设计中采用的相位比较器为何种类型,均可实现类似的功能性操作,因此就总体估计而言,相位比较器的选择并不构成限制。此外,设计过程中,还必须将包括锁定时间、稳定性、功耗等在内的次要设计因素考虑在内。

[0076]

接收器的时钟恢复

[0077]

图3所示的例示接收器采用一种pll实施方式。该pll将所接收的时钟信号r5作为其时钟的锁相参考信号。在一些实施方式中,适宜时可将逻辑电平移位器310作为用于检测的mic所提供的信号电平与优选相位比较器输入电平之间的接口。相位比较器320在将所述参考时钟与vco提供的本地时钟比较后,生成输出值。该输出值经低通滤波后提供误差值,以供后续对vco 340的工作频率进行校正。在一些实施方式中,相位比较器320输出数字波形,该数字波形需通过隐式或显式数模转换,或通过电荷泵等接口元件而转换为模拟误差信号。在一些实施方式中,通过数字滤波动作可将所述转换与整个所述低通滤波操作或与其一部分相结合,该结合仅作为一种非限制性的示例,该数字滤波动作图示为由数字控制信号控制的用于生成模拟信号输出的电荷泵切换动作。

[0078]

在至少一种实施方式中,将由形成闭环的一系列完全相同的门器件构成的环形振荡器340用做为所述pll的内部压控振荡器(vco)时序源。其中,可通过对该环形振荡器的门传播延迟、门间升降时间及门切换阈值当中的至少一者进行模拟而调整而改变所述vco的频率。这一点可通过切换式电容器组实现,其中,作为一种非限制性的实施例,通过施加数字控制信号,将电容性元件选择性地以并联和/或串联方式组合,从而改变rc时间常数。此外,还可通过增大或减小用于驱动所述环形振荡器门的电流源的方式,改变其输出切换升降时间,从而实现有效延迟的调整。通过沿组成所述环形振荡器的一系列门以等间隔进行输出采样(即隔相同个数的环形振荡器门进行采样),可获得四个数据相位采样时钟,在本技术中分别记为0度时钟、90度时钟、180度时钟和270度时钟。

[0079]

在一种实施方式中,所述环形振荡器由完全相同的八组逻辑门(即一组反相器电路)构成,从而使得每两组之间的相位差为45度。在该实施方式中,举例而言,所述0度、90度、180度和270度输出可分别获得自第二、第四、第六和第八输出。由于此类设计的多种变形形式在本领域中已为人所知,因此所述环形振荡器内的元件数目以及提供具体输出的具体抽头均不应理解为构成任何限制。举例而言,所述0度抽头可处于任意位置,这是因为熟悉本领域的技术人员可意识到的是,无论起始相位如何,pll在正常运行中均可实现所述环形振荡器相位与外部参考相位的对准。类似地,在其他同等设计中,所述输出时钟相位可不

具有方波占空比,此间一例为采用从不同抽头位置获得输入的and门(与门)或or门(或门)。在所述例示接收器中,vco优选在接收参考时钟频率的倍数下工作,因此在所述相位比较器上游还设有分频器350,用于以相应系数对vco输出进行分频。在一种实施方式中,通过采用二进制(系数为2)分频器350以获得正确的采样时钟速率。在另一实施方式中,不使用分频器,而是将vco输出直接提供给相位插值器。

[0080]

所述四个采样时钟相位当中的每一者均通过适当地定时而为所述四个并行处理级当中的一个处理级进行接收数据采样。具体而言,内部时钟ph000对准至可以以最佳方式触发处理级0中的数据采样器,内部时钟ph090对准至可以以最佳方式触发处理级1中的数据采样器,内部时钟ph180对准至可以以最佳方式触发处理级2中的数据采样器,内部时钟ph270对准至可以以最佳方式触发处理级3中的数据采样器。

[0081]

为了使被锁定的pll信号的总体相位与参考时钟输入相位相偏移,从相位插值器360获得提供给相位比较器的本地时钟输出,该相位插值器的输出相位以可控制方式介于其输入时钟相位之间。如此,不但所述pll可锁定至其固定相位关系,而且环形振荡器340所提供的内部时钟信号与该固定相位偏移相位插值器350在信号相位偏移校正功能的控制下所引入的相位延迟量。本领域已有为人所知的相位插值器,例如《buchwald 1》及《tajalli 2》中描述的插值器。

[0082]

在一种实施方式中,相位插值器360从环形振荡器340接收具有90度相位差的多个本地时钟相位。所述相位插值器可控制为选择两个相邻时钟输入相位,然后在其之间进行插值,从而在该两个被选值之间生成具有选定相位偏移的输出。出于描述的目的,可以假设所使用的相位比较器使得所述pll锁定为使得所述两个相位比较器输入之间的相位差为零。如此,在该例中,当在所述相位插值器中施加0度和90度的时钟相位作为输入时,可使得所述pll的相位调整为比参考时钟输入超前0度~90度。

[0083]

容易理解的是,使用其他度数的两个时钟以及/或者其他相位比较器设计,仍可获得具有类似相位偏移的同等结果,但是如上所述,此种情形下的锁定相位差与上例有所不同。由此可见,本技术中所述的具体选定相位时钟及具体的相位比较器设计均不构成限制。

[0084]

带插值器的相位比较器

[0085]

随着通信信道数据速率越来越高,固有和寄生电路节点电容所导致的电路延迟和有效环路响应带宽限制使得越来越难以维持可接受的pll锁定范围和精度。图5所示为一种提供适于此类高速运行的改进式响应特性的实施方式。本领域技术人员可看出的是,该实施方式为一种cmos设计,该设计针对正负输出偏移提供对称操作,而且同时集成了相位插值器和相位比较器两种设计当中的元件。这种紧密的集成方式降低了节点电容并促进了所需的高速运行,而且其平衡的差分结构简化了对充放电流的控制。

[0086]

与传统设计一致,所述pll的vco(或由该vco驱动的时钟分频器)向用于共同设置有效本地时钟相位的相位插值器元件510和515提供本地振荡器输入。如图所示,其中共有相互偏移90度的四个本地振荡器相位,即相当于两个相位处于正交关系及其互补信号,因此分别标为+i、+q及-i、-q,从而可实现整个360度的相位调整,或称“四象限”相位调整。在其他实施方式中,可将本地振荡器的相位数目减少至两个,或者可使用异于90度相位差的振荡器相位,或者可从一组四个以上的输入中选择时钟相位;作为非限制性的一例,可从一组八个输入时钟相位当中选择至少两个待插入的时钟相位。

[0087]

在第一实施方式中,相位插值器元件510包括四个混频元件,每一混频元件包括一对差分晶体管及受控电流源,并具有由所述四个并联混频元件驱动的公共差分输出端。因此,电流源ia(i)的配置方式控制着提供给所述公共输出端ckp的本地振荡器相位+i的量。类似地,电流源ia(-i)控制着所述输出中互补输出相位-1的量,ia(q)控制着相位+q的量,且ia(-q)控制着相位-q的量。对于熟悉本领域的技术人员而言显而易见的是,所述四个电流源可配置为在ckp端产生一个相对于pll本地时钟输入具有任何所需相位关系的输出时钟。

[0088]

类似地,相位插值器元件515的电流源ib(i)、ib(-i)、ib(q)和ib(-q)可配置为在ckn端获得一个相对于pll本地时钟输入具有任何所需相位关系的输出时钟。在一些实施方式中,ckpllp和ckplln可配置为具有互补关系,从而为相位比较器520提供平衡互补的正向和负向电流幅度。然而,也可配置非互补的ia和ib值,以获得特定的结果。作为一种非限制性的示例,在一种实施方式中,ia和ib值可分别调整,从而与保持完全互补的ia和ib值的实施方式相比,获得更高分辨率的相位调整。

[0089]

相位比较器520的第二输入为外部参考时钟ckref+/ckref-,用于生成相位误差输出电流vcoctl+ncoctl-。在一种改进的实施方式中,所述两个外部参考时钟具有相反极性,但并不一定具有互补相位,从而使得正极性比较和负极性比较分别表示不同的相位比较。这一改进实施方式可与非互补的ia和ib偏置配置方式相结合,从而在上述不同的相位比较过程中,实现独立的本地时钟相位调整。也就是说,在一种实施方式中,相位比较器520顶端的ckref输入为选自该电路中可供使用的参考时钟相位的第一相位,而电流ia调整至提供相对于所选第一相位的相应插入相位偏移。与此同时,相位比较器520底端的ckref输入为选自该电路中可供使用的参考时钟相位的第二相位,而电流ib调整至提供相对于所选第二相位的相应插入相位偏移。其中,此两相对相位偏移为等量偏移。

[0090]

相位插值器电流源的值可由外部控制逻辑配置,包括但不限于,硬件配置寄存器、控制处理器输出寄存器以及硬件cdr调整逻辑。

[0091]

其他相位比较器实施方式

[0092]

图5所示实施方式中的相位比较器520为与图4a相同的xor器件,用于通过将本地时钟ckpll与外部参考时钟ckref混频而生成相位误差输出vcoctl。在图12a所示的其他实施方式中,采用折叠式相位比较器1220,该比较器由电流吸收端ifix2与相位插值器510组合以及电流源ifixl与相位插值器515组合所产生的电流驱动。以下,将对图12a所示的该折叠式相位比较器实施方式进行进一步详细的描述。与上述实施方式一致,电流源ia(i)、ia(-i)、ia(q)和ia(-q)被配置为将pll时钟i、-i、q和-q以所期望的方式插入插值器输出ckpllp和中,而电流源ib(i)、ib(-i)、ib(q)和ib(-q)被配置为将pll时钟i、-i、q和-q以所期望的方式插入插值器输出ckplln和中。相位比较器1220还由所接收的参考时钟ckref+和ckref-驱动,以产生相位比较结果:相位误差(+)和相位误差(-)。在一些实施方式中,可通过对标记为“电路平衡反馈”的电路节点进行监测而确定所插入时钟信号的相对直流分量,然后可通过对510和515中的已配置的电流源的值进行调整而实现该相对直流分量的调整。在一些实施方式中,每一电流源ia和ib均接收七个控制比特。需要注意的是,本发明实施方式并不限制于接收七个控制比特,而且可例如根据相位插值器分辨率的设计约束,采用任何数目的控制比特。在一些实施方式中,电流源ia和ib相等(例如,对于

+/-i和+/-q,ia=ib)。在此类实施方式中,相位插值器510和515的分辨率为7个比特。在其他实施方式中,可通过使ib相对于ia移位,或通过使ia相对于ib移位,实现额外的分辨率。在一种例示实施方式中,ia=ib+8,其中,8为通过与每个电流源ia的控制比特相加而获得每个电流源ib的控制比特的十进制移位量。在此类实施方式中,p侧相位插值器510和n侧相位插值器515接收两个不同的vco相位,并且所述相位比较器从vco的不同相位采集信息。由于相位插值器510和515融合了来自vco的不同相位的信息,因此所述pll具有更加详细的pll相位信息,而且该pll的带宽比传统pll的带宽更高。

[0093]“ia=ib+移位量”的实施方式为具有两个部分相位比较器的矩阵相位比较器的一种特殊情形。其中,第一部分相位比较器(n侧xor比较器)将参考相位与一组vco反馈相位相比较,而第二部分相位比较器(p侧xor比较器)将参考时钟相位与另一组vco反馈相位相比较。以下,将对矩阵相位比较器实施方式进行更加详细的描述。

[0094]

在一些实施方式中,可使用图12a所示的折叠式结构。图12a与图5所示实施方式类似,但不同之处在于以折叠式相位比较器1220代替相位比较器520。如图所示,折叠式相位比较器1220包括电流源ifix1和ifix2,此两电流源可配置为向pmos相位插值器电流源ia和nmos相位插值器电流源ib提供更大的电压余量。此外,相位比较器1220包括与ckpllp和ckplln连接的一对晶体管支路。就说明目的而言,假设相位插值器510和515仅具有ia(i)和ib(i),此两电流源分别导通,以代表vco相位ph0000。当ckref相对于ph0000偏移90度时,折叠式相位比较器1220将处于锁定状态。如图13a所示,在一个周期的前180度(1)期间,对于前一个90度(2),pmos相位插值器510通过晶体管1206对相位误差信号的(-)端进行电流ip充电。与此同时,nmos相位插值器515通过晶体管1208对相位误差信号的(-)端进行电流in放电。类似地,在后一个90度(3)期间,经晶体管1202对相位误差信号的(+)端进行电流ip充电,并通过晶体管1204对该(+)端进行电流in放电。如图所示,ifix2从pmos相位插值器510所提供的电流中吸收固定量的电流,而ifix1向nmos相位插值器515提供一定量的电流,以防止该nmos相位插值器中的电流源从所述相位误差信号中吸收过量电流。这一技术实现了一种反向削波效应(clippingeffect)。本领域技术人员可注意到的是,当等量调整各电流ifix的幅度时,可对相位误差信号的范围产生影响。在一些实施方式中,增大ifix的幅度将使得所述相位误差信号的幅度范围降低,而减小ifix的幅度将使得该相位误差信号的幅度范围增大。这一关系如图13b所示。

[0095]

图13b为上述反向削波特征的时序图。图13b所示为电流ip在前180度(1)内的a和b两个ifix2值下的幅度,其中,a》b。如图所示,在ifix2=a的情形下,ip的幅度更小。当ifix2=b时,ip的幅度ip的幅度范围相对更高。本领域技术人员可注意到的是,在折叠式相位比较器1220进行in放电的情形中,可产生类似效应。

[0096]

在一些实施方式中,如图12a所示,可利用后180度(4)实现电路平衡反馈。在该电路平衡反馈相位(4)下,可通过pmos相位插值器510进行电流充电,并通过nmos相位插值器515进行电流放电。如果充电/放电电流之间存在不平衡,则电路平衡反馈信号将为非零信号,从而对这一不平衡进行指示。该不平衡的原因例如为晶体管之间不匹配。该电路平衡反馈信号可随后用于对ifix1或ifix2进行调整,以实现充电/放电电流的平衡。达到平衡后,所述平衡反馈信号即变为零。在一些实施方式中,可对所述电荷泵电路的电压进行监测。如果相等,则表示该电路达到了正确的平衡状态,即ip=in。图12b为图12a相位比较器电路的

简化示意图。

[0097]

或者,也可采用《tajalli 4》所述的相位比较器作为520或1220,以在采用低电源电压的实施方式中,实现同等的高信号余量相位检测。此外,在该实施方式中,520还可被包括图4a、图4b和图4c所示的所有变形的其他相位比较器替代。

[0098]

作为此类替代实施方式的一例,图4b所示的状态机相位/频率检测器可与图5的相位插值器设计相结合。

[0099]

图6a为一种传统cml钟控锁存器实施方式示意图,该锁存器由输出q和两种结果的钟控反馈锁存器构成,此两结果的状态由钟控差分输入d和初始化。图6b所示为同一电路,但其中以相位插值器615对时钟源相位进行调整,该相位插值器的操作原理见上文对图5的描述。

[0100]

当将图6b的钟控锁存器电路替换成图4b的每一d触发器实例时,即形成图7a和图7b所示替代实施方式。d触发器710由接收时钟ckref进行钟控,该接收时钟通过相位插值器715。作为出于解释的目的一例,如果不设置相位偏移(或者当所需偏移为0度)时,则电流源ia将以100%比例设为“混频”输入ckref,而其他三个电流源设为零电流。d触发器720由本地时钟ckpll进行钟控,该本地时钟通过设置相位插值器725的电流源ib(i)、ib(-i)、ib(q)和ib(-q)的方式获得,而该设置进一步对相互组合的i和q时钟的相对比例和极性进行控制。在一种实施方式中,如图3所示,i获得自ph000,-i获得自ph180,q获得自ph090,-q获得自ph270。此外,触发器710和720的复位功能由简易cml或门730驱动。

[0101]

需要注意的是,在该实施方式中,相位插值器715的大部分功能被禁用,其设置目的仅在于与处于工作状态的相位插值器725保持相同的寄生负载特性,以最大程度地提高电路对称性,并通过保持平衡的负载特性以最大程度地减少检测偏差和漂移等副作用。

[0102]

相互集成的相位比较器、插值器及电荷泵

[0103]

如上所述,pll的相位比较器输出一般用于驱动电荷泵电路(cpc),该电路输出用于控制vco的模拟误差信号。上述通过将pll相位比较器与时钟调整相位插值器相集成而实现的低电容和高电路速度改进还可通过以相同方式进一步集成电荷泵元件的方式进行进一步的扩展。

[0104]

在该集成实施方式中,图7a和图7b所示实施方式所提供的电荷泵控制信号upp、upn、downp及downn对图8所示的用于生成iout输出的电荷泵实施方式进行直接控制。电流源i

cpc

和参考电压v

ref

可配置为对i

out

的范围进行缩放和调整。熟悉本领域的技术人员可注意到的是,图8电路的非常高的对称性可实现在v

replica

和i

out

信号的生成之间进行精确跟踪。

[0105]

图8为根据一些实施方式具有更佳充电/放电电流平衡功能的电荷泵电路示意图。电路800包括并联的两个电荷泵802,804:电荷泵804内的两个差分对生成输出电流,该电流表示随升降脉冲而产生的相位误差信号;如下所述,电荷泵802的两个差分对用于将放电电流设置为与充电电流相等。具体而言,电流源i

cpc

通过以电流镜像电路提供相应偏置电压v

bp

的方式,设置充电电流水平,以对所述两个电荷泵的顶端电流源806,808进行驱动,从而将i

cpc

同样提供给每一电荷泵802,804。当upn降低并使得场效应晶体管(fet)810导通时,节点812被场效应晶体管806,810提供的充电电流i

cpc

充电(电容性元件814既可以为分立帽(discrete cap),也可以为寄生帽(parasitic cap))。在平衡条件下(即不存在相位误差),

随后在downp处于高信号电平时经底端场效应晶体管816放电的电流量应该将节点812恢复至v

ref

值。如果所述放电电流太低且电压v

replica

升至v

ref

以上,则放大器820将提高放电电流场效应晶体管818上的偏置电压v

bn

,以将放电电流的量增大至与充电电流i

cpc

相等,并使得节点812上的电压v

replica

恢复至v

ref

。另一方面,如果v

bn

在场效应晶体管818上设置的放电电流过高,则电压v

replica

将变得过低,放大器820随即通过降低放电场效应晶体管818上的偏置电压v

bn

使电荷泵电流恢复平衡。

[0106]

通过相位比较器、相位插值器及电荷泵元件的其他等效组合,还可获得其他实施方式。

[0107]

输入参考信号过采样

[0108]

之所以例如如图7a和7b所示以非对称方式使用相位插值器的原因在于本地时钟与参考时钟源的性质不同。前者获得自多相时钟源(如振荡器或分频器),该多相时钟源本身能够提供多相输入,以供相位插值元件使用。后者一般为获得自同一接收时钟源的单相时钟。

[0109]

在现有技术中,《tan》描述了一种组合的dll/pll结构,其中,pll的vco采用两条完全相同的压控延迟线路作为输入延迟线路,该输入延迟线路作用于参考时钟输入上,而且由单个反馈误差信号控制。《ng》和《chang》中还描述了将前端dll用作倍频器,以便于产生极高频的时钟。

[0110]

然而,当对此类受控延迟线路进行抽头采样时,如果该受控延迟线路设置为使得各抽头之间的差分延迟与接收时钟边沿之间的时间成正比,经过该延迟线路的接收时钟将产生一组具有一定多相时钟特点的输出。作为非限制性一例,总延迟与参考时钟周期相仿的四抽头延迟线路的等间隔输出将产生与正交相控时钟信号具有类似特点的输出。在该例中,当将每一此类输出与正确选择的本地时钟相位进行相位比较时,可通过将所生成的一系列相位误差结果相互组合而为所述pll的vco生成更为准确的总时钟误差信号。其中,接收时钟的各延迟形式使得来自所述vco的时钟具有可进行额外的相位比较的机会,从而使受控环路实现更高的更新速率,并可提高pll的环路带宽。如此,可以降低抖动,并实现更佳的抗噪性。也就是说,通过该技术,可以提高环路的更新速率,进而使得电路能够在更高频率下对噪声和抖动的影响进行跟踪和校正。

[0111]

为了使上述延迟相位比较能够为pll提供有意义的信息,所述延迟线路提供的延迟间隔必须与本地时钟相位之间的各时间段相协调。这种控制方式可为延迟元件提供延迟锁定环(dll)的多方面功能。从图9框图可看出,由dll 910向上述pll实施方式300提供外部时钟参考输入。在将接收时钟信号r5提供给抽头延迟线路916后,产生一系列接收时钟相位918。dll控制环路由相位比较器912提供,其中,该相位比较器通过将接收时钟与延迟时钟相比较而生成误差值,该误差值经低通滤波915后产生用于对所述延迟线路的时序进行控制的延迟调整信号。

[0112]

如此,在pll 300中,上述简单相位比较(图3中的320)由多相位比较器920实施。在至少一种实施方式中,由xor门将n条线路(n例如等于2,4,8等,而且还可以包括奇数,以产生60、120、180、240、300等其他相位)918上的每一接收参考时钟信号的相位与相位插值器360的线路965上的n个本地时钟信号相位当中的不同时钟相位相比较。每一xor门输出均表示可转换为模拟信号值的部分相位误差信号,而且如上所述,通过求和电路935将所有此类

模拟部分相位误差信号加和,以生成用于控制环形振荡器340的复合相位误差信号。在另一实施方式中,由与上述mic混频器相仿的加权求和节点实施所述求和935,该求和中选择的不同权重值可实现对pll的静态和动态工作特性进行进一步的控制。或者,也可通过以每一xor输出驱动相应晶体管电路向电容性元件注入电荷或从该电容性元件移除电荷的方式实现上述求和操作。此外,图9中的pll 340可设置为提供所需的相位偏移,其中,每一插入相位均相对于待与其进行xor比较的抽头延迟线路信号具有相同的偏移量。

[0113]

在一些系统环境中,例如当通信协议采用多个时钟信号时,可直接从接收器获得所述多相位参考时钟。

[0114]

上述多项比较操作所提供的额外反馈信息也可在不设上述延迟锁定环前端的情况下获得。在图10所示实施方式中,单个接收参考信号1018输入多相位比较器920内,其中,该单个接收参考信号与本地时钟信号965的两个或两个以上的相位当中的每个相位相比较。在一种实施方式中,由xor部分相位比较器通过将所述单个接收参考时钟相位918的相位与来自相位插值器360的本地时钟信号965的不同相位相比较的方式形成部分相位误差信号。每一部分相位误差信号均可转换为模拟信号值,而且如上所述,通过对所有此类模拟部分相位误差信号进行加和,可生成用于控制环形振荡器340的复合相位误差信号。在另一实施方式中,由与上述mic混频器相仿的加权求和节点实施所述求和935,该求和中选择的不同权重值可实现对pll的静态和动态工作特性进行进一步的控制。具体而言,通过对权重值进行调整,可在pll的时域传递函数中产生额外的闭环极点和/或零点,从而实现进一步的环路稳定性控制。

[0115]

图14a为参考信号ckref与四个vco相位(来自pll的反馈)的比较时序图:

[0116]

xor(ckref,vco’000)

[0117]

xor(ckref,vco’090)

[0118]

xor(ckref,vco’180)

[0119]

xor(ckref,vco’270)

[0120]

如图14a所示,假设所有权重值均相等。然而,这一假设纯属说明目的,不应视为以任何方式构成限制。图14a还包括对所述四个xor输出进行求和。可以看出,在锁定状态下,底部波形的积分为零,因此pll实现正确锁定。为方便起见,图14b还示出了基于xor运算的传统相位比较器,在该比较器中,参考相位仅与一个vco相位相比较。在锁定状态下,参考相位与vco相位相移90度,而且该xor运算的输出为平均值为零的矩形波形。如此,即可看出此两波形(图14b的简易xor运算和图14a的阵列xor运算)的不同之处,其中,在这两种情形中,给定时段的平均值均为零,并且pll处于锁定状态。采用部分相位比较器阵列的实施方式比采用单个xor相位比较器发生更多的跃迁。由于每次跃迁均携带与边沿相关的信息,因此更多跃迁意味着所述相位比较器能够从vco和ckref中采集到更多的信息。

[0121]

需要注意的是,在阵列xor实施方式中,某些比较可能需要使用xnor(异或非门)完成。如此,可通过为不同相位比较谨慎地选择xor或xnor的方式,保证系统稳定性。

[0122]

在至少一种实施方式中,所述求和中使用的权重值设置为随比较时钟相位与pll“正常锁定”相位之间的时序差成正比地减小。作为非限制性的一例,当pll的正常锁定相位为ph090时,ph090与接收参考信号之间的比较加权值为1;ph000和ph180(如相对于正常锁定相位偏移一个抽头)的比较加权值为1/2;接收参考信号与ph270(相对于正常锁定相位偏

移两个抽头)的比较加权值为1/4;等等。这些不同加权比较结果相加后形成复合信号,该复合信号经低通滤波330后,即成为用于控制pll的vco 340的所述误差值。

[0123]

在至少一种采用多个相位比较器的实施方式中,当采用相等的相位比较器加权值时,经观察,所述多项相位比较在12.5ghz的速率下产生确定性抖动。虽然该该抖动的幅度极小且抖动发生速率远高于环路滤波器截止频率,然而通过进行上述权重值调整,仍能显著地降低该确定性抖动。其中,权重值大小随其与主要参考信号样本之间的距离成正比减小。在一些实施方式中,通过在比较器电路中采用不同的权重值而构成离散时域滤波器。这一特性可用于简化模拟滤波器330的设计。举例而言,当所采用的加权值正确时,可在时域传递函数中构建离散的零值,从而为实现环路稳健性创造条件。

[0124]

与上述示例一致,通过相位比较器、相位插值器及电荷泵元件的其他等效组合,还可获得其他实施方式。

[0125]

矩阵相位比较

[0126]

上述接收参考信号的多个相位与本地pll时钟的多个相位之间的多相位比较还可以扩展至矩阵相位比较器,此间的一种实施方式如图11b所示,其中,该矩阵中的每一相位比较器1110(在图11b中可称为部分相位比较器)的一种实施方式在图11a中示为单相位比较器1110。为了说明起见,图中的各部分相位比较器排列为4

×

4的矩阵,然而该排列方式仅用于说明,并不构成限制。在各实施方式中,还采用具有任何m和n维度的矩形、正方形或稀疏矩阵,而且该矩阵的元素可由本技术中所述的任何部分相位比较器构成,并可选采用本技术中所述的任何加权因子计算方法。在本技术中,稀疏矩阵是指至少一个所述元素的权重值为零的任何实施方式。

[0127]

在完全矩阵比较中,来自接收参考信号的m个相位当中的每个相位均分别与来自本地时钟的n个相位当中的每个相位进行相位比较,该本地时钟可接收自pll,或者直接接收自vco或各种其他时钟源。出于说明的目的,此处的n个本地时钟相位接收自上述pll。每一所得相位误差信号均由预设或预定值加权,而且所有的(m

×

n)个加权结果经求和而产生总误差结果。其中的一个相位比较器例如为图11a所示的1110,该比较器由xor相位比较器1112构成,该xor相位比较器的输出馈送至加权因子1118。

[0128]

图11b中的完全矩阵相位比较器1120的一种实施方式由m

×

n个部分相位比较器1110的实例构成,每一部分相位比较器接收所述m个参考信号相位(本技术中记为ckref0、ckrefl、ckref2、ckref3)当中的一个相位以及所述n个本地时钟相位输入相位(本技术中记为ckpll0、ckplll、ckpll2、ckpll3)当中的一个相位,并产生加权结果(如多个部分相位误差信号1131、1132、1133、1134)。该加权结果输入求和功能935中,以生成复合相位误差信号1145。

[0129]

熟悉本领域的技术人员可看出的是,上述图9中的多相位比较器920相当于本矩阵比较器的一个部分使用的实例,即仅矩阵对角线上的比较器得到实例化。就功能而言,当将完全矩阵对角线上比较器的权重值设为非零值,并将所有其他比较器的权重值设为零值时,可得到完全相同的结果。因此,通过矩阵加权因子的选择性配置,可以以类似方式实现包括相位偏移的模拟、环路时域零值的引入等上述其他功能。

[0130]

图15所示为根据一些实施方式的方法1500的流程图。如图所示,方法1500包括:在方框1502中,接收n个本地时钟信号相位和m个参考信号相位,其中,m为大于或等于1的整

数,n为大于或等于2的整数。该方法还包括:在方框1504中,生成多个部分相位误差信号,每一部分相位误差信号至少部分通过将(i)所述m个参考信号相位当中的相应相位与(ii)所述n个本地时钟信号相位当中的相应相位相比较的方式形成。在方框1506中,通过将所述多个部分相位误差信号相加而生成复合相位误差信号,并随即以该复合相位误差信号调整本地振荡器的固定相位1508。

[0131]

在一些实施方式中,m=1,并且通过将n个部分相位误差信号相加而生成所述复合相位误差信号。或者,所述多个部分相位误差信号包括m=n个部分相位误差信号,而且利用所述n个本地时钟信号相位当中的给定相位以及所述m个参考信号相位当中的给定相位生成单个部分相位误差信号。在其他替代实施方式中,所述多个部分相位误差信号包括m

×

n个部分相位误差信号,而且所述n个本地时钟信号相位当中的每一相位均与所述m个参考信号相位当中的每一相位相比较。

[0132]

在一些实施方式中,所述多个部分相位误差信号当中的每一部分相位误差信号上均施加有相应的权重值。

[0133]

在一些实施方式中,所述m个参考信号相位接收自对输入参考信号进行处理的延迟锁定环。

[0134]

在一些实施方式中,所述n个本地时钟信号相位当中的至少一个本地时钟信号相位由对本地振荡器信号和相位偏移信号进行处理的相位插值器生成。在一些实施方式中,所述n个本地时钟信号相位当中的至少一个本地时钟信号相位的生成包括:通过所述相位插值器内的4个差分对插入4个相位,该4个相位当中的每一相位均根据与可独立调节的电流源相连的相应差分对被插入。

[0135]

在一些实施方式中,至少一个部分相位误差信号由一对触发器形成,其中,所述m个参考信号相位当中的给定相位对所述一对触发器中的第一触发器进行钟控,所述n个本地时钟信号相位当中的给定相位对第二触发器进行钟控。

[0136]

在一些实施方式中,每一部分相位误差信号均为由相应电荷泵生成的模拟信号,该相应电荷泵接收根据所述m个参考信号相位当中的相应相位与所述n个本地时钟信号相位当中的相应相位之间的相应比较生成的相应电荷泵控制信号。

[0137]

其他实施方式

[0138]

经两条专用时钟线路传输并从图2中mic5处接收的时钟信号接收方式的容易程度与作为携带相同数据的一条向量信令码子信道传输并例如从mic4接收的时钟信号接收方式的容易程度相同。这种将时钟内嵌于向量信令码子信道的方法如《shokrollahi 2》和《holden 3》中所述。其中描述的所有时钟内嵌实施方式均可与本技术中描述的pll和时序控制机制相结合,以产生有益效果,但这并不构成任何限制。

[0139]

类似地,其他利用数据线边沿跃迁进行时钟信号传输的已知方法也可与本技术中描述的pll和时序控制机制相结合。其中,尤其适合于结合的向量信令码为能够长时间保证跃迁密度的向量信令码,如《shokrollahi 1》中描述的向量信令码。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1