一种基于负电压自举电容的互补型自举开关及工作方法

1.本发明涉及模拟集成电路技术领域,具体涉及一种基于负电压自举电容的互补型自举开关及工作方法。

背景技术:

2.模数转换器是将模拟信号转换为数字信号的桥梁,而采样保持电路又是模数转换器的重要组成部分。自举开关的作用是周期性的采样模拟信号并保存,自举开关的速度和精度是后续其他模拟电路实现功能的基础。

3.自举电路存在着许多非理想因素,比如:沟道电荷注入、时钟馈通、采样电路存在寄生电容、导通电阻不固定等。而传统的自举开关仅由nmos晶体管或者pmos晶体管构成采样开关,当采样开关的源极和输入信号连接时,这种结构使得采样开关的栅源电压在采样阶段保持不变,但其他非理想因素如沟道电荷注入和寄生电容仍会影响自举开关的性能。此外,传统结构自举开关的采样开关在漏极和输入信号v

in

连接时无法实现栅源电压的固定,从而使导通电阻发生较大的变化,因此亟需一种基于负电压自举电容的互补型自举开关,通过采用互补的nmos和pmos共同构成采样开关,当采样开关的漏极和v

in

连接时,使导通电阻的变化幅度降低。

技术实现要素:

4.针对现有技术的不足,本发明提供一种基于负电压自举电容的互补型自举开关。采样开关由nmos晶体管和pmos晶体管构成,减小了沟道电荷注入效应;在关键节点引入自举电容,减小mos晶体管的宽长比,进而减小寄生电容,在高速采样频率下提升了自举开关的性能。

5.本发明的技术方案为:

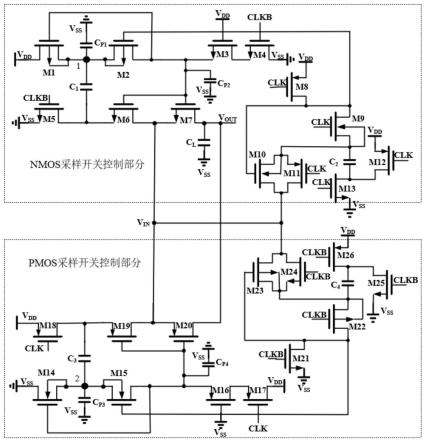

6.一种基于负电压自举电容的互补型自举开关,包括nmos采样开关控制部分和pmos采样开关控制部分,其中:

7.nmos采样开关控制部分包括第一nmos晶体管和第一pmos晶体管,所述第一nmos晶体管包括m3、m4、m5、m6、m7、m9、m10和m13,所述第一pmos晶体管包括m1、m2、m8、m11和m12;

8.其中,m1、m8、m12的源极和m3的栅极分别接电源电压v

dd

,m4的漏极和m5、m13的源极分别接地v

ss

;m8、m9、m11、m12、m13的栅极分别接采样时钟clk;m4、m5的栅极分别接采样时钟clkb,m1的漏极接m2的源极,m2的漏极、m3的源极分别和m1、m6、m7的栅极连接,m3的漏极和m4的源极连接,m5的漏极和m6的源极连接,m6的漏极、m7的源极分别和输入信号v

in

连接,m7的漏极和输出信号v

out

连接;

9.pmos采样开关控制部分包括第二pmos晶体管和第二nmos晶体管,所述第二pmos晶体管包括m16、m17、m18、m19、m20、m22、m23和m26,所述第二nmos晶体管包括m14、m15、m21、m24和m25;

10.其中,m14、m21、m25的源极和m16的栅极分别接地vss,m21、m22、m24、m25、m26的栅

极分别接采样时钟clkb,m14的漏极接m15的源极,m15的漏极、m16的源极分别和m14、m19、m20的栅极连接,m16的漏极和m17的源极连接,m5的漏极和m19的源极连接,m19的漏极、m20的源极分别和输入信号v

in

连接,m20的漏极和输出信号v

out

连接。

11.进一步地,所述nmos采样开关控制部分,还包括所述m8的漏极、m9的源极分别和m2、m10的栅极连接,m9的漏极分别和m10、m11的源极连接,m10和m11的漏极分别和输入信号v

in

连接,m12和m13的漏极连接。

12.进一步地,所述nmos采样开关控制部分还包括第一电容,所述第一电容包括c1和c2,其中,c1的上极板连接m1的漏极,c1下极板接m5的漏极,c2的上极板连接m11的源极,c2的下极板接m13的漏极,m1的衬底与m2的衬底分别连接到m1的漏极,m10的衬底与源极连接。

13.进一步地,所述pmos采样开关控制部分,还包括所述m21的漏极、m22的源极分别和m15、m23的栅极连接,m22的漏极分别和m23、m24的源极连接,m23和m24的漏极分别和输入信号v

in

连接,m25和m26的漏极连接。

14.进一步地,所述pmos采样开关控制部分还包括第二电容,所述第二电容包括c3和c4,c3上极板连接m14的漏极,c3下极板接m18的漏极,c4上极板接m23的源极,c4下极板接m26的漏极,m14的衬底与m15的衬底分别连接到m14的漏极,m23的衬底与源极连接。

15.一种基于负电压自举电容的互补型自举开关工作方法,包括:

16.通过设置采样时钟clk和clkb为相反的信号,控制互补型自举开关的通断,具体包括:

17.当自举开关工作在保持阶段时,clk为低电平,clkb为高电平;

18.对nmos采样开关控制部分:m1、m3、m4、m5开启,m2、m6、m7关闭,c1上极板电位为v

dd

,c1下极板电位为v

ss

;m8、m10、m11、m12开启,m9、m13关闭,c2上极板电位为v

in

,c2下极板电位为v

dd

;

19.对pmos采样开关控制部分:m14、m16、m17、m18开启,m15、m19、m20关闭,c3上极板电位为v

ss

,c3下极板电位为v

dd

;m21、m23、m24、m25开启,m22、m26关闭,c4上极板电位为v

in

,c4下极板电位为v

ss

。

20.进一步地,所述自举开关工作在采样阶段时,clk为高电平,clkb为低电平;

21.对nmos采样开关控制部分:m2、m6、m7开启,m1、m3、m4、m5关闭,c1的上极板电位为v

dd

+v

in

,下极板电位为v

in

;m9、m13开启,m8、m10、m11、m12关闭,c2的上极板电位为v

in-v

dd

,下极板电位为v

ss

;

22.对pmos采样开关控制部分:m15、m19、m20开启,m14、m16、m17、m18关闭,c3的上极板电位为v

in-v

dd

,下极板电位为v

in

;m22、m26开启,m21、m23、m24、m25关闭,c4上极板电位为v

in

+v

dd

,下极板电位为v

dd

。

23.进一步地,所述自举开关工作在采样阶段时,m7的栅源电压v

gs7

=v

dd

,m20的栅源电压v

sg20

=v

dd

,m2的栅源电压v

sg2

=2v

dd

,m15的栅源电压v

gs15

=2v

dd

,关键寄生节点的mos晶体管具有较高的栅源电压。

24.进一步地,所述自举开关工作在采样阶段时,m2的导通电阻为:

25.26.其中,μ

p

为空穴的迁移率,c

ox

为单位面积的栅氧化层电容,w和l是m2的沟道宽度和长度,v

th

为阈值电压。

27.进一步地,所述自举开关工作在采样阶段时,m2的导通电阻不变,m2的栅源电压提高而宽长比减小,进而减小晶体管带来的寄生电容,降低电荷再分配对晶体管的栅极电位影响。

28.本发明的有益效果为:

29.1.本发明采用互补的nmos晶体管和pmos晶体管作为采样开关,自举开关状态切换时部分电子和空穴会相互抵消,削弱了沟道电荷注入效应。

30.2.关键节点1和2存在寄生电容,会和c1、c3的上极板电荷进行电荷分配,使得c1、c3的上极板电位降低,本发明通过引入自举电容c2和c4使m2和m15的栅源电压提升到大约2v

dd

,在m2和m15的导通电阻不变时,本发明提升了栅源电压进而减小了晶体管的宽长比,进而减小了由于mos管带来的寄生电容,提升了自举开关的性能。

附图说明

31.构成本技术的一部分的说明书附图用来提供对本技术的进一步理解,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。

32.图1为本发明的基于负电压自举电容的互补型自举开关的电路结构示意图;

33.图2为本发明的基于负电压自举电容的互补型自举开关保持阶段示意图;

34.图3为本发明的基于负电压自举电容的互补型自举开关采样阶段示意图;

35.图4为本发明的m2的栅源电压瞬态仿真示意图;

36.图5为本发明实施例中的基于负电压自举电容的互补型自举开关的快速傅里叶变换示意图。

具体实施方式

37.下面结合说明书附图和实施例对本发明作进一步限定,但不限于此。

38.实施例1

39.如图1所示,本实施例提供一种基于负电压自举电容的互补型自举开关,包括nmos采样开关控制部分和pmos采样开关控制部分。

40.nmos采样开关控制部分包括第一nmos晶体管m3、m4、m5、m6、m7、m9、m10、m13,以及第一pmos晶体管m1、m2、m8、m11、m12。m1、m8、m12的源极和m3的栅极接电源电压v

dd

,m4的漏极和m5、m13的源极接地v

ss

,m8、m9、m11、m12、m13的栅极接采样时钟clk,m4、m5的栅极接采样时钟clkb,m1的漏极接m2的源极,m2的漏极、m3的源极和m1、m6、m7的栅极连接,m3的漏极和m4的源极连接,m5的漏极和m6的源极连接,m6的漏极、m7的源极和输入信号v

in

连接,m7的漏极和输出信号v

out

连接,m8的漏极、m9的源极和m2、m10的栅极连接,m9的漏极和m10、m11的源极连接,m10和m11的漏极和输入信号v

in

连接,m12和m13的漏极连接,电容c1上极板连接m1的漏极,下极板接m5的漏极,电容c2的上极板接m11的源极,下极板接m13的漏极,c

p1

和c

p2

是对地的寄生电容,m1的衬底与m2的衬底连接到m1的漏极,m10的衬底与源极连接,其余nmos衬底接地v

ss

,pmos衬底接电源电压v

dd

。

41.pmos采样开关控制部分包括第二pmos晶体管m16、m17、m18、m19、m20、m22、m23、

m26,以及第二nmos晶体管m14、m15、m21、m24、m25。m14、m21、m25的源极和m16的栅极接地v

ss

,m21、m22、m24、m25、m26的栅极接采样时钟clkb,m14的漏极接m15的源极,m15的漏极、m16的源极和m14、m19、m20的栅极连接,m16的漏极和m17的源极连接,m5的漏极和m19的源极连接,m19的漏极、m20的源极和输入信号v

in

连接,m20的漏极和输出信号v

out

连接,m21的漏极、m22的源极和m15、m23的栅极连接,m22的漏极和m23、m24的源极连接,m23和m24的漏极和输入信号v

in

连接,m25和m26的漏极连接,电容c3上极板连接m14的漏极,下极板接m18的漏极,电容c4的上极板接m23的源极,下极板接m26的漏极,c

p3

和c

p4

是对地的寄生电容,m14的衬底与m15的衬底连接到m14的漏极,m23的衬底与源极连接,其余nmos衬底接地v

ss

,pmos衬底接电源电压v

dd

。

42.实施例2

43.如图2-3所示,本实施例提供一种基于负电压自举电容的互补型自举开关工作方法,具体包括:

44.设置采样时钟clk和clkb为相反的信号,负载电容为c

l

。

45.其中,nmos的阈值电压为正数,pmos的阈值电压为负数,clk和clkb作为控制信号控制nmos和pmos的通断,只靠clk一个信号无法实现自举开关所需的mos管的通断状态,因此需要相反的clk和clkb信号共同控制,实现自举开关正常工作所需的电路连接方式。

46.参见图2,自举开关工作在保持阶段时,clk为低电平,clkb为高电平。

47.对nmos采样开关控制部分:m1、m3、m4、m5开启,m2、m6、m7关闭,c1上极板电位为v

dd

,c1下极板电位为v

ss

;m8、m10、m11、m12开启,m9、m13关闭,c2上极板电位为v

in

,c2下极板电位为v

dd

。

48.对pmos采样开关控制部分:m14、m16、m17、m18开启,m15、m19、m20关闭,c3上极板电位为v

ss

,c3下极板电位为v

dd

;m21、m23、m24、m25开启,m22、m26关闭,c4上极板电位为v

in

,c4下极板电位为v

ss

。

49.参见图3,自举开关工作在采样阶段时,clk为高电平,clkb为低电平。

50.对nmos采样开关控制部分:m2、m6、m7开启,m1、m3、m4、m5关闭,c1的上极板电位为v

dd

+v

in

,下极板电位为v

in

;m9、m13开启,m8、m10、m11、m12关闭,c2的上极板电位为v

in-v

dd

,下极板电位为v

ss

。

51.对pmos采样开关控制部分:m15、m19、m20开启,m14、m16、m17、m18关闭,c3的上极板电位为v

in-v

dd

,下极板电位为v

in

;m22、m26开启,m21、m23、m24、m25关闭,c4上极板电位为v

in

+v

dd

,下极板电位为v

dd

。

52.采样阶段m7的栅源电压v

gs7

=(v

dd

+v

in

)-v

in

=v

dd

,m20的栅源电压v

sg20

=v

in

(v

in-v

dd

)=v

dd

,栅源电压保持为常数,m2的栅源电压v

sg2

=(v

in

+v

dd

)-(v

in-v

dd

)=2v

dd

,关键寄生节点的mos晶体管具有较高的栅源电压,m15的栅源电压v

gs15

=(v

in

+v

dd

)-(v

in-v

dd

)=2v

dd

。

53.实施例3

54.本实施例利用cadence virtuoso eda工具进行电路设计和仿真,采用0.18μmcmos工艺。电路原理图如图1所示,包括nmos采样开关控制部分和pmos采样开关控制部分。

55.本发明的主要参数设置如下:

56.电源电压v

dd

=1.8v,采样频率fs(clk信号)=50mhz,输入信号频率f

in

=378.418khz,输入信号v

in

的电压范围为0-1.8v,负载电容c

l

为1pf。

57.m2的导通电阻如公式(1)所示:

[0058][0059]

其中,μ

p

为空穴的迁移率,c

ox

为单位面积的栅氧化层电容,w和l是m2的沟道宽度和长度,v

th

为阈值电压。m2栅源电压的瞬态仿真结果如图4所示,通过仿真结果可以看出,采样阶段m2的栅源电压接近3.6v(2v

dd

),由公式(1)可知,在导通电阻不变时,v

sg2

增加则减小,进而减小了节点1的寄生电容,最终降低了电荷再分配对m7栅极电位的影响。m15的栅源电压以及减小节点2寄生电容的方式与m2类似。

[0060]

对图1所示原理图进行频域仿真,采样4096个点,最终fft结果如图5所示,可以看到在50mhz采样频率下,自举开关的有效位数(effective number of bits,enob)达到16.5bits,信噪失真比(signal to noise and distortion ratio,sndr)和无杂散动态范围(spurs free dynamic range,sfdr)分别达到101.11db和101.83db,体现了本发明所提的自举开关结构在高采样率下具有较好的性能。

[0061]

本领域内的技术人员应明白,本技术的实施例可提供为方法、系统、或计算机程序产品。因此,本技术可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本技术可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

[0062]

本技术是参照根据本技术实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

[0063]

以上所述仅为本技术的优选实施例而已,并不用于限制本技术,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

[0064]

上述虽然结合附图对本发明的具体实施方式进行了描述,但并非对本发明保护范围的限制,所属领域技术人员应该明白,在本发明的技术方案的基础上,本领域技术人员不需要付出创造性劳动即可做出的各种修改或变形仍在本发明的保护范围以内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1