静电防护电路及电子设备的制作方法

1.本技术涉及静电防护技术,尤其涉及一种静电防护电路及电子设备。

背景技术:

2.静电是一种处于静止状态的电荷或者说不流动的电荷,在日常生活中,人体常常会携带有静电。在人体接触电子设备时,静电从人体流向电子设备产生静电放电现象,从而可能影响电子设备的正常工作,严重的甚至导致电子设备中的芯片及其它元器件击穿,产生不可挽回的损失。

3.电子设备都具有完整的外壳,静电对电子设备内部元器件的影响一般通过电子设备上的外接接口实现。例如电子设备在设计时,经常会遇到输入/输出(input/ouput,简称i/o)接口裸露在外壳之外的情况,例如usb(universal serial bus,通用串行总线)接口要突出外壳,用于数据传输和充电、供电需求;耳机接口需要裸露出来与外部耳机连接,用于输出音乐。当遇到静电放电时,静电会通过这些输入/输出接口进入电子设备的内部,从而可能损坏电子设备内部的元器件,导致永久性的损坏。

4.因此,设计专门的静电防护电路,以降低静电放电对电子设备的影响十分必要。

技术实现要素:

5.本技术的目的在于提供一种静电防护电路及电子设备,本技术可以降低静电放电对电子设备的影响,有利于提高电子设备的使用寿命。

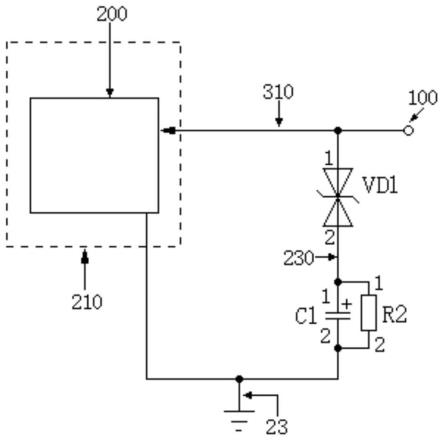

6.一方面,本技术提供一种静电防护电路,设置在连接电子设备的输入/输出接口和受保护的组件之间的信号线上,所述静电防护电路包括:第一静电防护器,所述第一静电防护器的第一端与所述输入/输出接口连接,所述第一静电防护器的第一端还连接所述受保护的组件;所述第一静电防护器的第二端连接第一电容的第一端,所述第一电容的第二端接地。

7.本技术在使用时,大部分的高压静电击穿第一静电防护器后被存储在第一电容中,变成低电压的电源能量,从而降低了流向受保护的组件的静电量,有利于提高电子设备的使用寿命。

8.如上所述的静电防护电路,可选地,所述第一静电防护器包括esd静电二极管、tvs二极管、开关二极管、tss二极管、稳压二极管、压敏电阻、气体放电管中的一种或多种。

9.如上所述的静电防护电路,可选地,所述受保护的组件与所述输入/输出接口之间的还串联连接有第一电子元件,所述第一电子元件的第一端连接所述输入/输出接口,所述第一电子元件的第二端连接所述受保护的组件;所述第一静电防护器的第一端连接在所述输入/输出接口和第一电子元件的第一端之间。

10.如上所述的静电防护电路,可选地,所述第一电子元件包括磁珠、电感和/或电阻。

11.如上所述的静电防护电路,可选地,所述第一电容的第一端还连接耗电元件的第一端,所述耗电元件的第二端接地。

12.如上所述的静电防护电路,可选地,所述耗电元件包括第二电阻,所述第二电阻的阻值大于20kω。

13.如上所述的静电防护电路,可选地,所述第一电子元件的第二端与所述受保护的组件之间还串联连接有第二电容,所述第二电容的第一端与所述受保护的组件相连接,所述第二电容的第二端与所述第一电子元件的第二端相连接。

14.如上所述的静电防护电路,可选地,所述第二电容的第一端与所述受保护的组件之间还串联连接有第一电阻,所述第一电阻的第一端与所述受保护的组件相连接,所述第一电阻的第二端与所述第二电容的第二端相连接。

15.如上所述的静电防护电路,可选地,所述第一电子元件与所述第二电容之间还设有第二静电防护器,所述第二静电防护器的第一端连接在所述第一电子元件与所述第二电容之间,且所述第二静电防护器的第二端接地。

16.如上所述的静电防护电路,可选地,所述电子设备内还设有电源电路,所述电源电路包括电源输入端和电源输出端;

17.所述第二静电防护器为三角管防护器,所述第二静电防护器包括第一二极管和第二二极管,所述第一二极管的阴极与所述第二二极管的阳极相连接,所述第一二极管的阳极通过所述第二静电防护器的第一端接地,所述第二二极管的阴极通过所述第二静电防护器的第二端接所述电源输入端或电源输出端,所述第二静电防护器的第三端设置在所述第一二极管的阴极与所述第二二极管的阳极之间,且所述第二静电防护器的第三端与所述第一电子元件的第二端相连接;

18.或者,所述第二静电防护器包括第三二极管和第四二极管,所述第三二极管的阴极与所述第四二极管的阳极相连接,所述第三二极管的阳极通过所述第二静电防护器的第一端接地,所述第四二极管的阴极通过所述第二静电防护器的第二端接所述电源输入端或电源输出端,所述第二静电防护器的第三端设置在所述第三二极管的阴极与所述第四二极管的阳极之间,且所述第二静电防护器的第三端与所述第一电子元件的第二端相连接。

19.如上所述的静电防护电路,可选地,所述电子设备内置电池,所述电池包括正极和负极,且所述电池的负极接地;

20.所述第二静电防护器为三角管防护器,所述第二静电防护器包括第一二极管和第二二极管,所述第一二极管的阴极与所述第二二极管的阳极相连接,所述第一二极管的阳极通过所述第二静电防护器的第一端接地,所述第二二极管的阴极通过所述第二静电防护器的第二端接电池的正极,所述第二静电防护器的第三端设置在所述第一二极管的阴极与所述第二二极管的阳极之间,且所述第二静电防护器的第三端与所述第一电子元件的第二端相连接;

21.或者,所述第二静电防护器包括第三二极管和第四二极管,所述第三二极管的阴极与所述第四二极管的阳极相连接,所述第三二极管的阳极通过所述第二静电防护器的第一端接地,所述第四二极管的阴极通过所述第二静电防护器的第二端接所述电池的正极,所述第二静电防护器的第三端设置在所述第三二极管的阴极与所述第四二极管的阳极之间,且所述第二静电防护器的第三端与所述第一电子元件的第二端相连接。

22.如上所述的静电防护电路,可选地,所述第二静电防护器为三角管防护器,所述第二静电防护器包括第一二极管和第二二极管,所述第一二极管的阴极与所述第二二极管的

阳极相连接,所述第一二极管的阳极通过所述第二静电防护器的第一端接地,所述第二二极管的阴极通过所述第二静电防护器的第二端接地,所述第二静电防护器的第三端设置在所述第一二极管的阴极与所述第二二极管的阳极之间,且所述第二静电防护器的第三端与所述第一电子元件的第二端相连接;

23.或者,所述第二静电防护器包括第三二极管和第四二极管,所述第三二极管的阴极与所述第四二极管的阳极相连接,所述第三二极管的阳极通过所述第二静电防护器的第一端接地,所述第四二极管的阴极通过所述第二静电防护器的第二端接地,所述第二静电防护器的第三端设置在所述第三二极管的阴极与所述第四二极管的阳极之间,且所述第二静电防护器的第三端与所述第一电子元件的第二端相连接。

24.如上所述的静电防护电路,可选地,所述第二静电防护器的第二端还连接第三电容的第一端,所述第三电容的第二端接地。

25.如上所述的静电防护电路,可选地,所述电子设备的供电电压接入所述第二静电防护器的第二端与所述第三电容的第一端之间。

26.如上所述的静电防护电路,可选地,所述耗电元件还包括所述电子设备的供电电源,所述供电电源的第一端连接在所述第二静电防护器的第二端与所述第三电容的第一端之间,所述供电电源的第二端接地;所述第一电容的第一端通过至少一个第五二极管连接所述供电电源的第一端。

27.如上所述的静电防护电路,可选地,所述第三电容的第二端与地线之间还设有金属片。

28.如上所述的静电防护电路,可选地,所述电感包括差模电感或共模电感。

29.如上所述的静电防护电路,可选地,所述第一电容至少包括两个阻抗特性曲线位于不同谐振点的电容,且每个所述电容的谐振点对应于静电放电或空气放电的不同干扰频点。

30.另一方面,本技术提供一种电子设备,包括屏蔽壳,所述屏蔽壳内设有受保护的组件,所述屏蔽壳外还设有输入/输出接口,所述输入/输出接口与所述受保护的组件之间通过信号线相连接,所述信号线上设有如上任一所述的静电防护电路。

31.本技术的电子设备由于设置了上述静电防护电路,当遇到静电放电时,静电对电子设备内的元器件影响较小,从而有利于提高电子设备的使用寿命。

附图说明

32.为了更清楚地说明本技术实施例或相关技术中的技术方案,下面将对实施例或相关技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

33.图1为相关技术中一种电子设备的结构简图;

34.图2为相关技术中另一种电子设备的结构简图;

35.图3为静电放电流波形图;

36.图4为静电放电设备的放电模型;

37.图5为一种电池供电设备中pcb板布局的俯视图;

38.图6为一种电池供电设备中各元器件在pcb板的电气模型;

39.图7为本技术一实施例提供的静电防护电路的简图;

40.图8为本技术另一实施例提供的静电防护电路的简图;

41.图9为本技术再一实施例提供的静电防护电路的简图;

42.图10为本技术一实施例中磁珠的阻抗频率的特性曲线图;

43.图11为图40对应的pcb板布局布线示意图;

44.图12为本技术又一实施例提供的静电防护电路的简图;

45.图13为电容的等效模型;

46.图14-图20为不同容值陶瓷电容的阻抗频率曲线图;

47.图21为150μf钽电容阻抗频率曲线图;

48.图22为本技术又一实施例提供的静电防护电路的简图;

49.图23为本技术又一实施例提供的静电防护电路的简图;

50.图24为同轴电缆供电电感频率特性曲线图;

51.图25为本技术又一实施例提供的静电防护电路的简图;

52.图26为本技术又一实施例提供的静电防护电路的简图;

53.图27为本技术又一实施例提供的静电防护电路的简图;

54.图28为本技术又一实施例提供的静电防护电路的简图;

55.图29为本技术又一实施例提供的静电防护电路的简图;

56.图30为本技术又一实施例提供的静电防护电路的简图;

57.图31为本技术又一实施例提供的静电防护电路的简图;

58.图32为本技术又一实施例提供的静电防护电路的简图;

59.图33为图32的局部剖视图;

60.图34为本技术又一实施例提供的静电防护电路的简图;

61.图35为图34的局部剖视图;

62.图36为本技术又一实施例提供的静电防护电路的简图;

63.图37为本技术一实施例提供的pcb地线的俯视图;

64.图38为本技术一实施例提供的pcb地铜箔的俯视图;

65.图39为本技术另一实施例提供的pcb地铜箔的俯视图;

66.图40为本技术又一实施例提供的静电防护电路的简图。

具体实施方式

67.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。

68.基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。在不冲突的情况下,下述的实施例及实施例中的特征可以相互组合。

69.人体触摸电子设备时,静电放电可能影响电子设备的正常工作,严重的甚至导致电子设备中的芯片及其它元器件击穿,产生不可挽回的损失。图1为相关技术中一种电子设

备的结构简图。请参照图1,电子设备包括外壳63以及设置在外壳63内的pcb板61,外壳63的一个端面65上设有缺口60,缺口60内安装有usb接口62,usb接口62与pcb板61相连接,用于pcb板61外接供电电源。在图1所示的电子设备中,usb接口62突出于外壳63设置,也即usb接口62的一部分位于端面65之外,从而方便外接电源适配器端子(图中未画出)穿过缺口60与usb接口62连接。图2为相关技术中另一种电子设备的结构简图。图2所示的电子设备与图1所示的电子设备差异在于,图2所示电子设备中,usb接口62与外壳63的端面65平齐。不管是图1中的电子设备,还是图2中的电子设备,手指都可以触摸到usb接口62,从而产生静电放电。静电放电通过接触放电的方式注入到产品的输入/输出接口时,产品会承受瞬间高压的静电能量,尤其是接口部分,很容易造成产品死机、复位、喇叭出现吱吱声音等功能异常,甚至出现产品内部芯片打坏导致产品不能正常开机。

70.为了降低静电放电对电子设备日常使用的影响,中国g6.2b/t1762标准(等同于国际标准iec61000-4-2)要求,电子设备的外壳上凡是手指能明显触摸到接口的金属部分,都需要做接触放电。图3示出了中国g6.2b/t1762标准要求静电放电流波形图;表1给出了不同级别接触放电测试在不同时段的放电电流值。

71.表1不同级别接触放电测试在不同时段的放电电流值

[0072][0073]

结合图3和表1可知,2kv级别接触放电测试条件下:在0.6ns~1ns放电电流上升时间内,放电电流达7.5a;在放电电流在30ns时,放电电流达4a;在放电电流在60ns时,放电电流达2a。4kv级别接触放电测试条件下:在0.6ns~1ns放电电流上升时间内,放电电流达15a;在放电电流在30ns时,放电电流达8a;在放电电流在60ns时,放电电流达4a。6kv级别接触放电测试条件下:在0.6ns~1ns放电电流上升时间内,放电电流达22.5a;在放电电流在30ns时,放电电流达12a;在放电电流在60ns时,放电电流达6a。8kv级别接触放电测试条件下:在0.6ns~1ns放电电流上升时间内,放电电流达30a;在放电电流在30ns时,放电电流达16a;在放电电流在60ns时,放电电流达8a。也就是说,接触放电测试级别越高,测试产生放电电流越大,几乎成正比例,对电子设备的静电防护设计带来巨大的挑战。接触放电测试的规格根据不同产品类型有所不同,例如,机顶盒的usb接口接触放电需要打4kv;工业级路由器的电源接口和usb接口接触放电需要打8kv;车载设备802的输入/输出接口接触放电需要打8kv;胎心监护仪耳机接口和usb接口接触放电需要打6kv;手机的指纹按键接触放电需要打12kv。

[0074]

结合图3和表1可知,接触放电的放电最小周期为0.6ns,周期t和频率f的换算公式如下:

[0075]

t=1/f,

[0076]

则f=1/t=1/0.6x10-9

s≈1.667x109hz=1.667ghz,也就是静电的干扰最高频段约为1.667ghz。

[0077]

接触放电的放电周期为1ns,周期t和频率f的换算公式如下:

[0078]

t=1/f,

[0079]

则f=1/t=1/1x10-9

s=1.0x109hz=1ghz,也就是静电的干扰频段为1ghz。

[0080]

接触放电的放电周期为30ns,周期t和频率f的换算公式如下:

[0081]

t=1/f,

[0082]

则f=1/t=1/30x10-9

s≈0.033333x109hz=0.033333ghz=33.33mhz,也就是静电的干扰频段约为33.33mhz。

[0083]

接触放电的放电周期为60ns,周期t和频率f的换算公式如下:

[0084]

t=1/f,

[0085]

则f=1/t=1/60x10-9

s≈0.01667x109hz=0.01667ghz=16.67mhz,也就是静电的干扰频段约为16.67mhz。

[0086]

图4为静电放电设备的放电模型。请参照图4,静电放电设备的规格如下:uo为静电放电设备直流高压电源,rc为直流高压电源的内阻(约在50兆欧~100兆欧),放电电容cs为150pf,内阻rd为330欧(330欧代表人体握钥匙和其它金属工具的人体电阻),k1为静电放电设备开关,m1静电放电设备的放电头,m2为放电回路连接点。相关标准认为用这种放电模型(包括电容量和电阻值)来描述静电放电是足够严酷的。

[0087]

图5为一种电池供电设备中pcb板布局的俯视图;图6为一种电池供电设备中各元器件在pcb板的电气模型。

[0088]

由于电池供电设备中电池内部电极表面有限,因此电池及pcb板对高压静电的吸收能力有限。如图5所示,usb连接器16设有第一金属触点10(usb+)、第二金属触点11(usb-),在usb连接器16的两个金属触点引出usb差分走线17,usb差分走线17分别对pcb地铜箔g并联静电防护器12、静电防护器13。也就是说,静电防护器12的一端与usb差分走线17的usb+电连接,另一端通过地过孔504(指n个地过孔,n≧1)与地铜箔g电连接(地铜箔g包括表层地铜箔及内层地铜箔),再通过地铜箔g、电池连接器134负极与电池132负极电连接。静电防护器13的一端与usb差分走线17的usb-电连接,另一端通过地过孔504(指n个地过孔,n≧1)与地铜箔g电连接(地铜箔g包括表层地铜箔及内层地铜箔),再通过地铜箔g、电池连接器134负极与电池132负极电连接。当在第一金属触点10、第二金属触点11之间注入4kv~12kv的接触放电时,会在usb差分走线17产生4kv~12kv的静电,并联在usb差分走线17两端的静电防护器12、静电防护器13瞬间被击穿导通,将4kv~12kv的静电钳制在十几伏左右。但是,还有十几伏残压向基带芯片55泄放,基带芯片55的usb管脚会出现乱码,可能导致usb眼图(眼图是衡量usb差分质量好坏的指标)发生问题。

[0089]

另外,电池供电设备如果将静电直接泄放到pcb地铜箔g,pcb地铜箔g就会静电产生泄放电流。例如,如图5所示,内存(ddr)颗粒56通过地过孔501(指n个地过孔,n≧1)与地铜箔g电连接(地铜箔g包括表层地铜箔及内层地铜箔);再通过地铜箔g、电池连接器134负极与电池132负极电连接。基带芯片55通过地过孔502(指n个地过孔,n≧1)与地铜箔g电连接(地铜箔g包括表层地铜箔及内层地铜箔);再通过pcb地铜箔g、电池连接器134负极与电

池132负极电连接。闪存芯片54通过地过孔≦5(指n个地过孔,n≧1)与地铜箔g电连接(地铜箔g包括表层地铜箔及内层地铜箔);再通过地铜箔g、电池连接器134负极与电池132负极电连接。射频芯片57通过地过孔503(指n个地过孔,n≧1)与地铜箔g电连接(地铜箔g包括表层地铜箔及内层地铜箔);再通过地铜箔g、电池连接器134负极与电池132负极电连接。基带芯片55通过内存走线51(敏感信号线)与内存颗粒56电连接,基带芯片55通过串行外设接口(spi)走线513(敏感信号线)与闪存芯片54电连接,基带芯片55通过iq走线512(敏感信号线)与射频芯片57电连接。

[0090]

基带芯片55位置的地铜箔g上静电产生的泄放电流为i2,基带芯片55通过地过孔502、地铜箔g到电池负极之间的电气阻抗约为r12,因此基带芯片55、地铜箔g到电池负极之间产生压降为v6(v6=r12

×

i2)。

[0091]

内存颗粒56位置的地铜箔g上静电产生的泄放电流为i1,内存颗粒56通过地过孔501、地铜箔g到电池负极之间的电气阻抗约为r13,因此内存颗粒56、地铜箔g到电池负极之间产生压降为v7(v7=r13

×

i1)。

[0092]

地过孔502通过地铜箔g到地过孔501之间静电产生的泄放电流为i11,地过孔502通过地铜箔g到地过孔501之间电气阻抗约为r21,因此地过孔502通过地铜箔g到地过孔501之间静电产生压降为v2(v2=r21

×

i11)。

[0093]

正常工作时,内存颗粒56与基带芯片55通过内存走线51进行信号连接,内存颗粒56的参考点为地过孔501,基带芯片55的参考点为地过孔502,地过孔501与地过孔502之间通过地铜箔g电连接。因内存走线51走线电流非常小,所以地过孔502到地过孔501回流电流较小,它们之间压降非常小;也就是说,基带芯片55的参考点的电位与内存颗粒56的参考点的电位几乎是相等的。但有静电注入usb连接器时,静电瞬间产生巨大脉冲电流会导致基带芯片55的参考点的电位与内存颗粒56的参考点的电位差非常大(基带芯片55的参考点与内存颗粒56的参考点的电位差为v2,v2等于v7-v6的绝对值)。此时基带芯片55与内存颗粒56之间通信就会产生乱码(例如丢包、死机等现象),严重时会损坏器件。

[0094]

闪存芯片54位置的地铜箔g上静电产生的泄放电流为i3,闪存芯片54通过地过孔505、地铜箔g到电池负极之间的电气阻抗约为r14,因此闪存芯片54、地铜箔g到电池负极之间产生压降为v8(v6=r14

×

i3)。

[0095]

射频芯片57位置的地铜箔g上静电产生的泄放电流i4,射频芯片57通过地过孔503、地铜箔g到电池负极之间的电气阻抗约为r15,因此射频芯片57、地铜箔g到电池负极之间产生压降为v9(v9=r15

×

i4)。

[0096]

本技术的发明人经过长期研究,在对电子设备进行静电防护时,归纳出以下原则:1、尽可能将静电堵在外壳(金属外壳接pcb地铜箔g可将静电导入大地;对于塑胶外壳,将静电堵在塑胶外壳外部,不让其泄放到内部元器件)。2、尽可能将输入/输出接口不外露,能不接触放电,就空气放电,空气放电没有接触放电带来的危害大。3、对于ac-dc(交流-直流)供电设备,能泄放到pcb地铜箔g,就尽量泄放在pcb地铜箔g,而不泄放在信号线上;泄放在信号线上的静电要用静电防护器导入到pcb地铜箔g或pcb板中的电源上,避免损坏元器件或导致输入/输出管脚功能失效。4、对于电池供电设备,如果不能将外露输入/输出接口密封,则尽量将输入/输出接口的静电泄放到电容(例如电解电容、超级电容),将高压静电储存在电容的两个极板,这样可以大大降低静电荷的电动势,大大消弱静电荷对输入/输出接口信

号的影响,防止对周围pcb地铜箔g的电平抬高,导致pcb地铜箔g对其它输入/输出接口进行泄放静电,引起其它输入/输出接口信号复位或对输入/输出接口产生损坏等一系列异常问题的出现。

[0097]

基于上述,本技术旨在提供一种静电防护电路及电子设备,通过在输入/输出接口和第一电子元件之间连接第一静电防护器,第一静电防护器和pcb地铜箔或pcb地线之间串联第一电容c1;高压静电从输入/输出接口流入后,大部分的高压静电击穿第一静电防护器后被存储在第一电容c1中,变成低电压的电源能量,从而降低了流向受保护的组件的静电量,有利于提高电子设备的使用寿命。

[0098]

而pcb地线23的宽度《0.8mm,且pcb地铜箔23的形状可以为规则的图形,也可以为不规则图形,而pcb地线23一般都是规则,且宽度是统一

[0099]

图37为本技术一实施例提供的pcb地线的俯视图;图38为本技术一实施例提供的pcb地铜箔的俯视图;图39为本技术另一实施例提供的pcb地铜箔的俯视图。请参照图37-图39,其中图38给出了规则图形pcb地铜箔的俯视图;图39给出了不规则图形pcb地铜箔的俯视图。需要说明是pcb地铜箔23与pcb地线23作用是一样,只不过pcb地铜箔23的宽度比pcb地线23的宽度要大:pcb地线23<1mm,pcb地铜箔23的宽度w1≧1mm。另外且pcb地线23的线宽是固定的,例如一条地线线宽w1全部都为0.8mm或0.9mm等。图37中的地线23为了绕开信号过孔901,地线23还有一个折弯903。不限制地线23的形状。pcb地铜箔23的形状可以为规则的图形,例如图38中pcb地铜箔23的形状为规则长方形,pcb地铜箔23的宽度w1≧1mm,在pcb地铜箔23还分布有多个地孔900。pcb地铜箔23的形状也可以为不规则的图形,例如图39中pcb地铜箔23的形状为规则的图形,在pcb地铜箔23下方还有一个开槽905,同时在pcb地铜箔23还可以有地孔900,还有电源过孔903、信号过孔901,为了避免电源过孔903、信号过孔901在pcb地铜箔23中发生短路,在pcb地铜箔23与电源过孔903之间设置了净空区域904(无铜区域),在pcb地铜箔23与信号过孔901之间设置了净空区域906(无铜区域)。也就是图39中地铜箔23有开槽905、净空区域906、净空区域904等,地铜箔23是一个不形状为规则的图形。

[0100]

需要说明是受保护的组件200既可以为受保护的组件(例mcu、基带芯片等),也可以为受保护的组件及其外围电路组成受保护的模组,因为有些受保护的组件可以直接与图7~图9、图11、图12、图22、图23、图25~图32所示电路防护方案连接后,再与输入/输出接口100连接,例如mcu普通i/o的管脚引出信号线可以通过图7~图9、图11、图12、图22、图23、图25~图32所示电路防护方案连接后,再与输入/输出接口100(例如复位信号)连接。这种方案定义为受保护的组件,它也是受保护的组件200的一种类型。而有些受保护的组件需要添加一些阻容匹配电路才能与图7~图9、图11、图12、图22、图23、图25~图32所示电路防护方案其中一种连接,再与输入/输出接口100:例如音频codec(coder-decoder,视频和音频压缩与解压缩的编解码器)芯片引出mic(麦克风)电路需要增加一些mic音频的阻容匹配电路,阻容匹配电路再通过信号线与图7~图9、图11、图12、图22、图23、图25~图32所示电路防护方案其中一种连接后,再与mic(属于输入/输出接口100)连接;wifi芯片引出巴伦电路将差分射频信号合成单路射频信号后,需要增加50欧匹配电路,50欧匹配电路再通过信号线与图7~图9、图11、图12、图22、图23、图25~图32所示电路防护方案其中一种连接,再与外置天线(属于输入/输出接口100)连接,wifi芯片不能直接通过信号线直接与图7~图9、

图11、图12、图22、图23、图25~图32所示电路防护方案其中一种连接后,再与外置天线(属于输入/输出接口100)连接。将音频codec芯片+mic音频的阻容匹配电路定义为受保护的模组,它也是受保护的组件200的一种类型。wifi(wireless fidelity,无线保真)芯片+巴伦电路+50欧匹配电路定义为受保护的模组,它也是受保护的组件200的一种类型。

[0101]

下面将结合附图详细的对本技术实施例的内容进行描述,以使本领域技术人员能够更加详细的了解本技术的内容。

[0102]

图7为本技术一实施例提供的静电防护电路的简图;图8为本技术另一实施例提供的静电防护电路的简图;图9为本技术再一实施例提供的静电防护电路的简图。

[0103]

请参照图7-图9,本实施例提供一种静电防护电路,用于设置在连接电子设备的输入/输出接口100和受保护的组件200之间的信号线300上。静电防护电路包括第一静电防护器vd1,第一静电防护器vd1的第一端与输入/输出接口100连接,第一静电防护器vd1的第一端还连接受保护的组件200;第一静电防护器vd1的第二端连接第一电容c1的第一端,第一电容c1的第二端接地(需要说明的是,本实施例中并不限定接地的具体形式,例如,可以是接pcb地铜箔、pcb地线、电池的负极、ac-dc适配器的次级输出端接地、机壳地、大地等任意一种)。

[0104]

本实施例在使用时,大部分的高压静电击穿第一静电防护器vd1后被存储在第一电容c1中,变成低电压的电源能量,从而降低了流向受保护的组件200的静电量,有利于提高电子设备的使用寿命。

[0105]

本实施例中,第一静电防护器vd1包括esd静电二极管(electro-static discharge,静电保护管)、tvs二极管(transient voltage suppressors,瞬态抑制二极管)、开关二极管、tss二极管(thyristor surge suppressors,浪涌抑制晶闸管)、稳压二极管、压敏电阻、气体放电管中的一种或多种。例如,在一个可选地实施方式中,第一静电防护器vd1可以为esd静电二极管,esd静电二极管的第一端与输入/输出接口100连接,esd静电二极管的第二端连接第一电容c1。又如,在另一个可选地实施方式中,第一静电防护器vd1可以为esd静电二极管和压敏电阻,esd静电二极管的第一端与输入/输出接口100连接,esd静电二极管的第二端连接压敏电阻的第一端,压敏电阻的第二端连接第一电容c1。本领域技术人员清楚的是,本实施例中第一静电防护器vd1的具体结构可根据实际需要进行确定。

[0106]

本实施例还包括串联连接在输入/输出接口100和受保护的组件200之间的第一电子元件(本实施例中以第一电子元件是磁珠l1为例进行说明);第一电子元件的第一端连接输入/输出接口100,第一电子元件的第二端连接受保护的组件200;第一静电防护器vd1的第一端连接在输入/输出接口100和第一电子元件的第一端之间。

[0107]

也就是说,磁珠l1的第一端(即磁珠l1的1脚)连接输入/输出接口100,磁珠l1的第二端(即磁珠l1的2脚)连接受保护的组件200;第一静电防护器vd1的第一端(即第一静电防护器vd1的1脚)连接在输入/输出接口100和磁珠l1之间,第一静电防护器vd1的第二端(即第一静电防护器vd1的2脚)连接第一电容c1的第一端(即第一电容c1的1脚),第一电容c1的第二端(即第一电容c1的2脚)连接pcb地铜箔或pcb地线23。

[0108]

本实施例中,第一电子元件包括磁珠、电感或电阻。上述实施例中描述了第一电子元件为磁珠l1的实施方式,在其他可能的实施方式中,本实施例中的第一电子元件还可以为磁珠和电阻,此时磁珠l1的第一端连接输入/输出接口100,磁珠l1的第二端连接电阻的

第一端,电阻的第二端连接受保护的组件200。本领域技术人员清楚的是,在其他可能的实施方式中,本实施例的第一电子元件还可以为电感、磁珠和电感、磁珠电感和电阻等。

[0109]

本实施例通过在电子设备的输入/输出接口100和受保护的组件200的信号线300上连接磁珠l1,在输入/输出接口100和磁珠l1之间连接第一静电防护器vd1,且在第一静电防护器vd1和pcb地铜箔或pcb地线23之间串联第一电容c1。当高压静电从输入/输出接口100流入后,磁珠l1可以阻止大部分的高压静电流向受保护的组件200,因此大部分的高压静电击穿第一静电防护器vd1后被存储在第一电容c1中,变成低电压的电源能量,从而降低了流向受保护的组件200的静电量,有利于提高电子设备的使用寿命。

[0110]

在一个可能的实施方式中,请继续参照图7-图9,本实施例的第一电容c1的第一端还连接耗电元件的第一端,耗电元件的第二端接pcb地铜箔或pcb地线23。

[0111]

本实施例通过设置耗电元件以利于第一电容c1内存储的电能,从而合理的利用了静电的能量,实现了将静电“变害为利”的转换。

[0112]

进一步地,耗电元件包括第二电阻r2,第二电阻r2与第一电容c1并联连接,第二电阻r2的第一端(即第二电阻r2的1脚)连接第一静电防护器vd1的第二端,第二电阻r2的第二端(即第二电阻r2的2脚)接pcb地铜箔或pcb地线23。

[0113]

本实施例中,第二电阻r2的阻值大于20kω。

[0114]

本实施例通过设置第二电阻r2可以将存储在第一电容c1内的电能以发热方式消耗掉。

[0115]

在一个可能的实施方式中,请继续参照图7-图9,本实施例的磁珠l1的第二端与受保护的组件200之间还串联连接有第二电容c2和第一电阻r1,第二电容c2的第一端(即第二电容c2的2脚)与磁珠l1的第二端相连接,第二电容c2的第二端(即第二电容c2的1脚)与第一电阻r1的第一端(即第一电阻r1的2脚)相连接,第一电阻r1的第二端(即第一电阻r1的1脚)连接受保护的组件200。

[0116]

本实施例通过在磁珠l1和受保护的组件200之间串联第二电容c2和第一电阻r1以组成电阻-电容电路,第二电容c2可以阻止静电流向受保护的组件200;第一电阻r1相当于一个分压模块,可以将静电的残压进行分压,进一步降低静电对受保护的组件200的影响。

[0117]

可选地,本实施例在高速电路或高频电路中,第一电阻r1的阻值为2.0-2.2ω;在中低速电路或中低频电路中,第一电阻r1的阻值为5.1ω。

[0118]

在一个可能的实施方式中,本实施例的磁珠l1与第二电容c2之间还设有第二静电防护器vd2,第二静电防护器vd2的第一端连接在磁珠l1与第二电容c2之间,且第二静电防护器vd2的第二端接pcb地铜箔或pcb地线23。

[0119]

本实施例通过在磁珠l1与第二电容c2之间设置第二静电防护器vd2,第二静电防护器vd2被击穿后可以将通过磁珠l1的静电导向接地,从而更进一步的降低了静电对受保护的组件200的影响。

[0120]

在一个可能的实施方式中,电子设备内还设有电源电路,电源电路包括电源输入端和电源输出端;

[0121]

第二静电防护器vd2为三角管防护器,第二静电防护器vd2包括第一二极管a1和第二二极管a2,第一二极管a1的阴极与第二二极管a2的阳极相连接,第一二极管a1的阳极通过第二静电防护器vd2的第一端接pcb地铜箔或pcb地线,第二二极管a2的阴极通过第二静

电防护器vd2的第二端接电源输入端或电源输出端,第二静电防护器vd2的第三端设置在第一二极管a1的阴极与第二二极管a2的阳极之间,且第二静电防护器vd2的第三端与第一电子元件的第二端相连接。

[0122]

或者,电子设备内还设有电源电路,电源电路包括电源输入端和电源输出端;

[0123]

第二静电防护器vd2包括第三二极管和第四二极管,第三二极管的阴极与第四二极管的阳极相连接,第三二极管的阳极通过第二静电防护器vd2的第一端接pcb地铜箔或pcb地线,第四二极管的阴极通过第二静电防护器vd2的第二端接电源输入端或电源输出端,第二静电防护器vd2的第三端设置在第三二极管的阴极与第四二极管的阳极之间,且第二静电防护器vd2的第三端与第一电子元件的第二端相连接。

[0124]

在一个可能的实施方式中,电子设备内置电池,电池包括正极和负极,且电池的负极接pcb地铜箔或pcb地线;

[0125]

第二静电防护器vd2为三角管防护器,第二静电防护器vd2包括第一二极管a1和第二二极管a2,第一二极管a1的阴极与第二二极管a2的阳极相连接,第一二极管a1的阳极通过第二静电防护器vd2的第一端接pcb地铜箔或pcb地线,第二二极管a2的阴极通过第二静电防护器vd2的第二端接电池的正极,第二静电防护器vd2的第三端设置在第一二极管a1的阴极与第二二极管a2的阳极之间,且第二静电防护器vd2的第三端与第一电子元件的第二端相连接。

[0126]

或者,电子设备内置电池,电池包括正极和负极,且电池的负极接pcb地铜箔或pcb地线;

[0127]

第二静电防护器vd2包括第三二极管和第四二极管,第三二极管的阴极与第四二极管的阳极相连接,第三二极管的阳极通过第二静电防护器vd2的第一端接pcb地铜箔或pcb地线,第四二极管的阴极通过第二静电防护器vd2的第二端接电池的正极,第二静电防护器vd2的第三端设置在第三二极管的阴极与第四二极管的阳极之间,且第二静电防护器vd2的第三端与第一电子元件的第二端相连接。

[0128]

在一个可能的实施方式中,第二静电防护器vd2为三角管防护器,第二静电防护器vd2包括第一二极管a1和第二二极管a2,第一二极管a1的阴极与第二二极管a2的阳极相连接,第一二极管a1的阳极通过第二静电防护器vd2的第一端接pcb地铜箔或pcb地线,第二二极管a2的阴极通过第二静电防护器vd2的第二端接pcb地铜箔或pcb地线,第二静电防护器vd2的第三端设置在第一二极管a1的阴极与第二二极管a2的阳极之间,且第二静电防护器vd2的第三端与第一电子元件的第二端相连接。

[0129]

或者,第二静电防护器vd2包括第三二极管和第四二极管,第三二极管的阴极与第四二极管的阳极相连接,第三二极管的阳极通过第二静电防护器vd2的第一端接pcb地铜箔或pcb地线,第四二极管的阴极通过第二静电防护器vd2的第二端接pcb地铜箔或pcb地线,第二静电防护器vd2的第三端设置在第三二极管的阴极与第四二极管的阳极之间,且第二静电防护器vd2的第三端与第一电子元件的第二端相连接。

[0130]

更进一步地,第二静电防护器vd2的第二端还连接有第三电容c3的第一端(即第三电容c3的1脚),第三电容c3的第二端(即第三电容c3的2脚)接pcb地铜箔或pcb地线23。

[0131]

可选地,电子设备的供电电压(vcc)410接入第二静电防护器vd2的第二端与第三电容c3的第一端之间。

[0132]

本实施例通过在第二静电防护器vd2的第二端与pcb地铜箔或pcb地线23之间串联第三电容c3,第三电容c3可以存储流经第二静电防护器vd2的静电能量,由于电子设备的供电电压410与第三电容c3相连接,因此存储在第三电容c3内的静电能量可以为电子设备供电。

[0133]

更近一步地,如图9所示,耗电元件还包括电子设备的供电电源400,供电电源400的第一端连接在第二静电防护器vd2的第二端与第三电容c3的第一端之间,供电电源400的第二端接pcb地铜箔或pcb地线23;第一电容c1的第一端通过至少一个第五二极管vd6连接供电电源400的第一端。

[0134]

本实施例通过将第一电容c1与供电电源400通过第五二极管vd6相连接,从而可以利用存储在第一电容c1内的电能补充供电电源400的能量。

[0135]

可选地,如图8和图9所示,本实施例在第三电容c3的第二端与pcb地铜箔或pcb地线23之间还设有金属片500。

[0136]

本实施例通过在第三电容c3和地线之间设置金属片500以存储静电,从而进一步避免了产品功能出现异常及对降低对pcb板内元件器的损伤。

[0137]

本实施例的电感包括差模电感或共模电感。

[0138]

本实施例中输入/输出接口100和受保护的组件200之间的信号线300可以传输低频信号、低速信号、高速信号、高频信号其中任意一种。

[0139]

本实施例中第一电容c1至少包括两个阻抗特性曲线位于不同谐振点的电容,且每个电容的谐振点对应于静电放电或空气放电的不同干扰频点。

[0140]

本实施例还提供一种电子设备,包括屏蔽壳210,屏蔽壳210内设有pcb板和受保护的组件200,屏蔽壳210上还设有输入/输出接口100,输入/输出接口100与受保护的组件200之间通过信号线300相连接,信号线300上设有如上任一的静电防护电路。

[0141]

本实施例的电子设备由于设置了上述静电防护电路,当遇到静电放电时,静电对电子设备内的元器件影响较小,从而有利于提高电子设备的使用寿命。

[0142]

下面结合附图对本实施例的静电防护电路进行进一步地详细说明。

[0143]

由于接触放电的能量非常高(约在2kv~10kv),而输入和输出接口100的工作电压一般为1.8v-3.3v,也就是说输入和输出接口100的门限电压就是1.8v-3.3v。静电枪可以产生2kv-8kv的电压,若直接加载在输入和输出接口100,则输入和输出接口100无法承受而直接损坏。因此,本实施例设计了如图7所示的静电防护电路。

[0144]

如图7所示,与外接输入/输出接口100连接的信号线(例如麦克风信号线)300一端分别与第一静电防护器vd1(例如瞬态抑制二极管、压敏电阻、气体放电管等)的1脚、磁珠l1的1脚连接,第一静电防护器vd1的2脚与第一电容c1的1脚连接,第一电容c1的2脚与受保护的组件200的pcb板(printed circuit board,印制电路板,以下简称“pcb板”)地铜箔23连接,也就是第一静电防护器vd1的2脚通过第一电容c1连接到pcb地铜箔或pcb地线23;在第一电容c1的1脚和2脚两端并联第二电阻r2,也就是第二电阻r2的1脚与第一静电防护器vd1的2脚连接,第二电阻r2的2脚与pcb地铜箔或pcb地线23连接。磁珠l2的2脚分别与第二静电防护器vd2(本实施例中第二静电防护器vd2为三管脚防护器件)的3脚、第二电容c2的2脚连接,第二静电防护器vd2内部第二二极管a2的阴极通过第二静电防护器vd2的2脚与第三电容c3的1脚(如果第三电容c3是有极性电容,1脚一定要是正极,无极性就没有限制)连接,同

时在第三电容c3的1脚及第二静电防护器vd2的2脚再与pcb板中供电电压(vcc)连接;第三电容c3的2脚与pcb地铜箔或pcb地线23连接。第二静电防护器vd2中的第一二极管a1的阳极通过第二静电防护器vd2的1脚与pcb地铜箔或pcb地线23连接。第二电容c2的1脚与电阻r1的2脚连接,电阻r1的1脚与受保护的组件200管脚(例如芯片的信号脚)连接。pcb地铜箔或pcb地线23既可以为地线,也可以为地平面,优选地平面。在受保护的组件200(例如芯片)及其外围元件上方添加一个金属屏蔽盖210,金属屏蔽盖210焊接在pcb板上并完全覆盖受保护的组件200及其外围元器件。

[0145]

本实施例中,第一静电防护器vd1、储能第一电容c1、第二电阻r2组成前级泄放通道。第二静电防护器vd2的击穿电压略高于信号线303的最高电平。因第二电阻r2跨接在第一电容c1两端,所以第一电容c1即使有电荷,也会被第二电阻r2以发热方式消耗掉,平时无静电泄放到输入/输出接口100时,可以认为第一电容c1两端电平为0。这样信号线300平时工作时,第二静电防护器vd2未达到击穿的临界状态,完全是截止,不影响信号线303的正常工作。如果第二静电防护器vd2的击穿电压低于信号的最高电平,这样信号在正常传输过程中,当信号的电平处于第二静电防护器vd2的击穿阀值电压时,就会出现信号被钳位,也就是信号超过第二静电防护器vd2的击穿阀值电压就会被“削顶”,导致信号波形失真,这不符合硬件设计要求。因此第二静电防护器vd2的击穿阀值电压要略高于信号的最高电平,这样信号在正常传输过程中,信号不会超过第二静电防护器vd2的阀值电压,也就是正常信号传输时,第二静电防护器vd2不工作。

[0146]

当信号线303传输高速信号或高频信号时,由于高速信号或高频信号摆幅较低,不会高于电源电压(例如常用电源电压3.3v、1.8v等),只要第一静电防护器vd1击穿的阀值电压感略高于高速信号或高频信号的摆幅,第一静电防护器vd1击穿就不会被击穿,因此即使第一电容c1虽然接pcb地铜箔或pcb地线23,但第一电容c1不会将信号线303中的高速信号或高频信号对pcb地铜箔或pcb地线23对地短路(高速信号或高频信号类似于交流信号,而交流信号经过电容相对于短路),因此不影响高速信号或高频信号在信号线303上正常传输,符号高速信号或高频信号的设计规则。

[0147]

当在信号线303的外接输入/输出接口100注入4kv到12kv接触放电时,第一静电防护器vd1瞬间被击穿,巨大放电电流通过第一电容c1的正极释放到负极(此时电容相当于短路),最后再到pcb地铜箔或pcb地线23,静电电荷瞬间聚集在第一电容c1的两个极板之间,也就是在第一电容c1的两个极板形成静电场,将4kv到12kv接触放电的静电电荷储存在第一电容c1的两个极板之间,再通过第二电阻r2逐渐以发热方式消耗掉。当接触放电的静电电荷遇到磁珠l1时,磁珠l1会呈现非常高的阻抗,阻止静电电流快速通过磁珠l1,同时在磁珠l1的两端产生较高的压降,尽可能将静电电荷阻挡在第一静电防护器vd1、第一电容c1、第二电阻r2组成的前级泄放通道进行充分泄放。由于第一电容c1的容值较大,可以将75%~85%的接触放电的静电电荷吸收,储存在第一电容c1的两端。而第二电阻r2跨接在第一电容c1两端,第二电阻r2会以发热方式逐渐将第一电容c1中存储的静电荷消耗掉。第二电阻r2在选择阻值较大电阻(优选20kω以上),因为当输入/输出接口100注入接触放电且第一静电防护器vd1击穿时,如果第二电阻r2取值较低(例如几十欧),则第二电阻r2会将静电电荷以接pcb地铜箔或pcb地线方式泄放到pcb地铜箔或pcb地线23。设计的初衷是将接触放电的静电电荷存储在第一电容c1中,这个是设计核心思想,尤其是对于电池供电的设备或

产品。电池供电的设备或产品在做空气放电或接触放电时,没有可以泄放的通道,不能像带ac-dc适配器的设备或产品,可以通过设备或产品通过ac-dc适配器将高压静电荷泄放到大地。

[0148]

跨接在信号线300和供电电压410、pcb地铜箔或pcb地线23三个网络之间的第二静电防护器vd2、第三电容c3组成第二级泄放通道。跨接在信号线300和供电电压410两个网络之间的第二静电防护器vd2中内部二极管正极与信号线300相连接,而负极与供电电压410端的第三电容c3连接。信号的最高电平略低于供电电压410,这样信号线300平时工作时,第二静电防护器vd2中二极管处于截止状态,不影响信号线300的正常工作。当+4kv~+12kv接触放电的静电电荷经第一静电防护器vd1、储能第一电容c1、第二电阻r2等组成的泄放回路及磁珠l1阻挡后,还有约15%~25%能量进入磁珠l1后级连接的第二静电防护器vd2中的第一二极管a1、第三电容c3,将此时静电残压产生电平高于供电电压410加上第二静电防护器vd2导通的压降,静电残压经第二静电防护器vd2中第一二极管a1,会快速往供电电压410的储能第三电容c3的正极和负极注入静电电荷,静电残压储存在第三电容c3的两个极板之间,该静电残压在第三电容c3中变成供电电压410的能量,相当于给供电电压410充电,给整个电源网络的负载供电。第三电容c3为静电能量转换器,将高压静电转换为可以给pcb板负载供电的电源能量,实现了“变害为利”的转换。经过第二静电防护器vd2、第三电容c3组成的二级泄放电路可以将信号钳位在供电电压410加上第二静电防护器vd2的正向压降到第二静电防护器vd2的正向压降之间,大大削弱了高压静电能量对受保护的组件200的敏感管脚(例如信号线管脚)及受保护的组件200内部的骚扰。本实施例中,第二静电防护器vd2的正向压降约为0.2v~0.7v。

[0149]

如果第二静电防护器vd2压降为0.7v(例如硅管),则信号线300的钳位电压在-0.7v~vcc+0.7v之间。当在输入/输出接口100注入接触放电为2kv~8kv正电压时,信号线300的钳位电压在0v~vcc+0.7v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常,当在输入/输出接口100注入接触放电为2kv~8kv负电压时,信号线300的钳位电压在-0.7v~0v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常。

[0150]

如果第二静电防护器vd2压降为0.3v(例锗管),则信号线300的钳位电压在-0.3v~vcc+0.3v之间。当在输入/输出接口100注入接触放电为2kv~8kv正电压时,信号线300的钳位电压在0v~vcc+0.3v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常,当在输入/输出接口100注入接触放电为2kv~8kv负电压时,信号线300的钳位电压在-0.3v~0v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常。

[0151]

第二静电防护器vd2具体选硅管,还是锗管,根据实际应用情况来定,原则是二极管vd4、二极管vd5的压降要略超过信号线300的工作电平,二极管vd4、二极管vd5的压降小于信号线300的工作电平阀值,就会导致信号线300的信号被“削顶”,二极管vd4、二极管vd5的压降远远大于信号线300的工作电平阀值,就会有较高的静电残压注入c2、r1、受保护的组件200等后级电路,导致后级电路的功能异常或损坏。

[0152]

另外,第二静电防护器vd2具体选硅管,还是锗管,或其它类型二极管,但要求开关速度较高的二极管,这样第二静电防护器的响应速度才赶得上0.6ns静电泄放的响应速度。

[0153]

本实施例在第二静电防护器vd2与芯片之间串联的第二电容c2、第一电阻r1组成第三级防护电路,第二电容c2、第一电阻r1组成的电阻-电容电路实际组成为带通滤波器。经第二静电防护器vd2、第三电容c3组成的二级泄放电路泄放后,约还有5%的能量往受保护的组件200注入,但第二电容c2通低频阻高频,通交阻直的特性,直接可以阻止低频静电能量往受保护的组件200端注入。可根据信号的工作频率来选择第二电容c2,信号的工作频率高,第二电容c2可选择工作频率高点电容;这样第二电容c2的截止频率不影响信号的正常工作,但可以阻止第二电容c2的截止频率(较高频率)以下静电残压注入芯片敏感管脚及芯片内部。信号的工作频率低,第二电容c2可选择工作频率低点电容;可以阻止第二电容c2的截止频率(较低频率)以下静电残压注入芯片敏感管脚及芯片内部。第二电容c2容值越小,阻止静电残压频段越长,也就是第二电容c2容值越小,可以阻止中低频段的静电残压。约阻碍1%~2%静电残压。第二电容c2到芯片之间串入了第一电阻r1,第一电阻r1相当于一个分压模块,经过第二电容c2隔中低频静电残压后,在第二电容c2添加串联分压第一电阻r1可以将雷击的残压进行分压,进一步减小对受保护的组件200的敏感管脚及受保护的组件200内部骚扰影响,在高速电路或高频电路中,第一电阻r1一般选择2.0欧或2.2欧的电阻;在中低速电路或中低频电路中,第一电阻r1一般选择5.1欧的电阻。经第一电阻r1分压后,具体可以将雷击的残压抑制约2%~3%分量。第一电阻r1可选择0201封装或0201以上封装(优选0402封装)的电阻,不建议选择0201以下的封装。第一电阻r1的功率应满足泄放要求,避免封装太小,功率不够。

[0154]

需要说明的是,本实施例中各级泄放通道不能交换。例如将第二电阻r2放在输入和输出接口100位置,静电枪产生的高压通过第二电阻r2后,产生2a~30a泄放电流(不同规格不一样,不同时间点泄放电流不一样),因此会在第二电阻r2产生非常高的压降。

[0155]

如果电阻阻值较小,起不到阻止静电的作用,同时产生巨大功耗。例如第二电阻r2选2欧,按功率计算公式p=i2r=30

×

30

×

2=1800w,而现在产品中pcb板密度越来越高,pcb板中的电子元器件的电阻都会选0201、0402、0805、1206封装等贴片,只要接触放电注入静电,第二电阻r2无法承受立即烧毁。表2给出了各封装类型电阻的承受功率大小:0201封装的电阻承受功率为1/20w,0402封装的电阻承受功率为1/16w,0603封装的电阻承受功率为1/10w,0805封装的电阻承受功率为1/8w,1206封装的电阻承受功率为1/4w。根据上述所计算第二电阻r2选2欧时功耗就达1800w,0201封装、0402封装、0603封装、0805封装、1206封装的电阻无法满足这个要求,瞬间就会被烧坏。

[0156]

表2各封装类型电阻的承受功率大小

[0157][0158][0159]

而第二电阻r2阻值较大,会影响产品的功能。假设输入和输出接口100为音频耳机

输出,第二电阻r2阻值较大,输出功率会在第二电阻r2消耗较大,导致传输给外接耳机功率非常小,不符合设计要求。例如第二电阻r2设计为10ω,耳机输出电流为500ma,在第二电阻r2的压降为500ma

×

10ω=5w,显然是不符合设计要求。另外,如果输入和输出接口100为usb接口,电阻超过10ω,就会导致usb的眼图睁不开,不符合设计要求。

[0160]

而本技术将第一静电防护器vd1与第一电容c1串联直接与输入和输出接口100连接,当静电枪产生的高压静电通过时,会超过第一静电防护器vd1的门限值,会立即导通,而对于瞬间脉冲电压,第一电容c1相当于短路,也就是会在第一电容c1两个极板产生电动势,也就是将高压静电的能量存储在第一电容c1的两个极板上,第一电容c1的容值越大,能存储的静电能量越多,对静电吸收能力越好。

[0161]

根据计算可知:

[0162]

当静电接触放电电压为2kv时,储存在静电枪中电荷量为q,根据库仑定律得到储存在静电枪中电荷量q1=u1

×

c=2kv

×

150pf=3x10-7

c。

[0163]

当静电接触放电电压为4kv时,储存在静电枪中电荷量为q,根据库仑定律得到储存在静电枪中电荷量q2=u2

×

c=4kv

×

150pf=6x10-7

c。

[0164]

当静电接触放电电压为6kv时,储存在静电枪中电荷量为q,根据库仑定律得到储存在静电枪中电荷量q3=u3

×

c=6kv

×

150pf=9x10-7

c。

[0165]

当静电接触放电电压为8kv时,储存在静电枪中电荷量为q,根据库仑定律得到储存在静电枪中电荷量q4=u4

×

c=8kv

×

150pf=12x10-7

c。

[0166]

当静电接触放电电压为12kv时,储存在静电枪中电荷量为q,根据库仑定律得到储存在静电枪中电荷量q5=u5

×

c=12kv

×

150pf=18x10-7

c。

[0167]

本实施例中,磁珠l1和第二电容c2的位置不能互换。磁珠放在第二静电防护器vd2与第一静电防护器vd1和第一电容c1的串联组合之间。当静电枪产生的高压静电通过时,80%的静电能量会被第一静电防护器vd1和第一电容c1的串联组合存储在第一电容c1中;但还有20%能量流过,这20%能量对于输入和输出接口100也是非常高能量,远远超过输入和输出接口100的门限值。而磁珠l1的特性就是,对于静电的快速(ns级别)脉冲,它表现出非常高的阻抗,阻止静电通过,也就是静电来到磁珠l1时,会被磁珠l1反射回来,让第一静电防护器vd1和第一电容c1串联组合充分吸收,存储在第一电容c1的两端。大约只有5%的静电穿过磁珠l1,且还有约1%的能量会以热损耗方式,被磁珠l1消耗掉。图10为本技术一实施例中磁珠的阻抗和频率的特性曲线图;如图10所示,本实施例的磁珠l1的谐振点在1ghz左右,磁珠在谐振点的阻抗是最高,约为380ω;从图10可得知,在磁珠l1的谐振点的左边(在1hz~1ghz带宽范围内),磁珠l1体现出电感的特性;在磁珠的谐振点的右边(在1ghz以上带宽范围),磁珠l1体现出电容的特性;结合图3和表1可知,接触放电的放电最小周期为0.6ns,周期t和频率f的换算公式如下:

[0168]

t=1/f,

[0169]

则f=1/t=1/0.6x10-9

s=1.667x109hz=1.667ghz,也就是静电的干扰最高频段约为1.667ghz。

[0170]

结合图10可知,本实施例中磁珠的阻抗在1ghz的谐振点的阻抗达到最大,约为383欧,在60mhz达到100欧阻抗,在160mhz达到200欧阻抗,290mhz达到300欧阻抗,在2ghz达到300欧阻抗,在3ghz达到220欧阻抗,也就是磁珠也就是在静电的干扰频段范围,本实施例的

磁珠都体现出较高阻抗。

[0171]

而图5中的第1级就将静电瞬间产生中绝大部分能量(约占90%能量)存储在电容c2的两个极板内,大大消弱了静电瞬间产生对脉冲电流通过整板地铜箔23对器件管脚、信号走线的影响,尤其是共地阻抗带来两个器件之间通信产生乱码(例如丢包、死机等现像),严重时会出损坏器件。同时接触放电注入到外接口,也不会影响片受保护的组件200内部管脚的正常功能。

[0172]

图11为图40对应的pcb板布局布线示意图;请继续参照图11和图40,输入/输出接口100露出于屏蔽壳之外或靠近屏蔽壳开口的位置,输入/输出接口100例如是usb接口。第一静电防护器vd1的1脚与输入/输出接口100连接,第一静电防护器vd1的2脚与通过信号线230与第一电容c1的1脚、第二电阻r2的1脚连接,第一电容c1的2脚、第二电阻r2的2脚与pcb地铜箔23连接。磁珠l1的1脚通过信号线303与第一静电防护器vd1的1脚连接,磁珠l1的2脚通过信号线303与第二静电防护器vd2(双向静电防护器)的1脚、第二电容c2的2脚连接,第二静电防护器vd2的2脚与pcb地铜箔23连接。第二电容c2的1脚通过信号线97与第一电阻r1的2脚连接,第一电阻r1的1脚通过信号线98与芯片200(受保护的组件)连接。当在输入/输出接口100注入4kv到8kv接触放电时,在输入/输出接口100到第一静电防护器vd1之间第一段信号线330上产生瞬间高压,击穿第一静电防护器vd1,在第一静电防护器vd1产生十几安以上的静电放电电流i2,该静电放电电流i2注入到第一电容c1的1脚(正极管脚),由于电容的“隔直通交”的特性,瞬间大量的静电电荷通过第一电容c1的1脚注入第一电容c1内部正极极板(正极和负极内含大面积的极板,图11未标示),在第一电容c1内部负极极板(正极和负极内含大面积的极板,图11未标示)同时感应出静电电荷,将在第一电容c1内部负极板感应出的静电电荷接到第一电容c1的负极管脚22,最后将感应出的静电电荷注入到pcb地铜箔或pcb地线23。瞬间大量的静电电荷以低电动势的方式存储在第一电容c1的两个正负两个极板(图11未标示),再逐渐向并联在第一电容c1两端的第二电阻r2的释放能量,产生电流i3,缓慢消耗存储在第一电容c1的两个正负两个极板的静电电荷,直到全部消耗完毕。

[0173]

经过第一静电防护器vd1吸收静电能量约为注入到输入/输出接口100的能量的85%~90%。经过第一静电防护器vd1后第二段信号线303上还有一定残压,瞬间静电泄放电i4遇到磁珠l1的1脚,由于瞬间静电16.67mhz~1.667ghz干扰频段,在磁珠l1中体现非常高的阻抗(图10给出了磁珠l1的阻抗频率的特性曲线图),阻止静电电流快速通过磁珠l1,同时在磁珠l1的两端产生较高的压降,尽可能将静电电荷阻挡在第一静电防护器vd1、第一电容c1、第二电阻r2组成的前级泄放通道进行充分泄放。只有非常小的残余电流i5穿越磁珠l1,当穿越磁珠l1中静电残压超过了跨接在信号线303中的第二静电防护器vd2阀值时,第二静电防护器vd2瞬间导通,产生泄放电流i6到pcb地铜箔23或地线23,此时注入到第二电容c2的残压非常小,经电容c2的“隔直通交”后,通过第二电容c2的低频成分基本被第二电容c2过滤掉,再经第一电阻r1分压后,最后到达芯片200(受保护的组件)的管脚16静电残压几乎微乎其微,也就是对受保护的组件200的管脚16信号没有干扰,不影响产品正常工作,更不会打坏芯片200(受保护的组件)。

[0174]

下面以静电接触放电电压为4kv为例进行分析说明:

[0175]

当静电接触放电电压为4kv时,储存在静电枪中电荷量为q,根据库仑定律得到储存在静电枪中电荷量q=u2

×

c=4kv

×

150pf=6x10-7

c。瞬间大量的静电电荷通过第一电容

c1的正负两极板,当第一电容c1的正负两极板达到最高电动势时,此时存储在第一电容c1的正负两极板的电荷量为q几乎吸收85%~90%静电荷能量。第一电容c1吸收85%静电枪中电荷量为5.1x10-7

c;第一电容c1吸收90%静电枪中电荷量为5.4x10-7

c。

[0176]

根据紧凑型产品中电容耐压一般选6.3v,安全工作电压不能超过5v(电容耐压的80%降额),因此存储在第一电容c1两端静电荷的电压u1=5v。根据库仑定律可知,当静电接触放电电压为2kv,第一电容c1吸收90%静电枪中电荷量时,第一电容c1所需容值为0.54μf。也就是当静电接触放电电压为2kv时,第一电容c1选型为0.54μf的容值时,第一电容c1吸收90%静电枪中电荷量为2.7x10-7

c的电荷量,在第一电容c1两端静电荷的电压约为5v,5v电压不会对与第一电容c1正极连接的电源网络产生高压击穿危险。根据中国g6.2b/t1762标准(等同于国际标准iec61000-4-2),需要对输入/输出接口100做接触正放电10次,再负放电10次。也就是在正放电10次期间,第一电容c1要吸收10倍0.54μf,才能避免接触正放电10次注入至输入/输出接口100。因此第一电容c1选为0.54μf

×

10=5.4μf,考虑到第一电容c1的容值存在正负公差,因此要预留余量,在实际使用时,第一电容c1可选为6.8μf。

[0177]

当静电接触放电电压为4kv,第一电容c1吸收90%静电枪中电荷量时,第一电容c1所需容值为1.08μf。也就是当静电接触放电电压为4kv时,第一电容c1选型为1.08μf的容值时,第一电容c1吸收90%静电枪中电荷量为5.4x10-7

c的电荷量,在第一电容c1两端静电荷的电压约为5v,5v电压不会对与第一电容c1正极连接的电源网络产生高压击穿危险。根据中国g6.2b/t1762标准(等同于国际标准iec61000-4-2),需要对输入/输出接口100做接触正放电10次,再负放电10次。也就是在正放电10次期间,第一电容c1要吸收10倍1.08μf,才能避免接触正放电10次注入至输入/输出接口100。因此第一电容c1选为1.08μf

×

10=10.8μf。在实际使用时,第一电容c1可选为22μf,或第一电容c1选两颗电容:10μf电容+2.2μf电容(考虑到第一电容c1两个电容的容值存在正负公差,因此要预留余量)。

[0178]

当静电接触放电电压为6kv,第一电容c1吸收90%静电枪中电荷量时,第一电容c1所需容值为1.62μf;也就是当静电接触放电电压为6kv时,第一电容c1选型为1.62μf的容值时,第一电容c1吸收90%静电枪中电荷量为8.1x10-7

c的电荷量,在第一电容c1两端静电荷的电压约为5v,5v电压不会对与第一电容c1正极连接的电源网络产生高压击穿危险。根据中国g6.2b/t1762标准(等同于国际标准iec61000-4-2),需要对输入/输出接口100做接触正放电10次,再负放电10次。也就是在正放电10次期间,第一电容c1要吸收10倍1.62μf,才能避免接触正放电10次注入至输入/输出接口100。因此第一电容c1选为1.62μf

×

10=16.2μf。在实际使用时,第一电容c1可选为22μf,或第一电容c1选两颗电容:10μf电容+6.8μf电容(考虑到第一电容c1两个电容的容值存在正负公差,因此要预留余量)。

[0179]

当静电接触放电电压为8kv,第一电容c1吸收90%静电枪中电荷量时,第一电容c1所需容值为2.16μf;也就是当静电接触放电电压为8kv时,第一电容c1选型为2.16μf的容值时,第一电容c1吸收90%静电枪中电荷量为10.8x10-7

c的电荷量,在第一电容c1两端静电荷的电压约为5v,5v电压不会对与第一电容c1正极连接的电源网络产生高压击穿危险。根据中国g6.2b/t1762标准(等同于国际标准iec61000-4-2),需要对输入/输出接口100做接触正放电10次,再负放电10次。也就是在正放电10次期间,第一电容c1要吸收10倍2.16μf,才能避免接触正放电10次注入至输入/输出接口100。因此第一电容c1选为2.16μf

×

10=21.6μf。在实际使用时,第一电容c1可选为22μf(考虑到第一电容c1两个电容的容值存在正负公

差,因此要预留余量)。

[0180]

当静电接触放电电压为10kv,第一电容c1吸收90%静电枪中电荷量时,第一电容c1所需容值为3.24μf;也就是当静电接触放电电压为10kv时,第一电容c1选型为3.24μf的容值时,第一电容c1吸收90%静电枪中电荷量为16.2x10-7

c的电荷量,在第一电容c1两端静电荷的电压约为5v,5v电压不会对与第一电容c1正极连接的电源网络产生高压击穿危险。根据中国g6.2b/t1762标准(等同于国际标准iec61000-4-2),需要对输入/输出接口100做接触正放电10次,再负放电10次。也就是在正放电10次期间,第一电容c1要吸收10倍3.24μf,才能避免接触正放电10次注入至输入/输出接口100。因此第一电容c1选为3.24μf

×

10=32.4μf。在实际使用时,第一电容c1可选为32.4μf(考虑到第一电容c1两个电容的容值存在正负公差,因此要预留余量)。

[0181]

需要说明一点是,该方案的好处在于,对输入/输出接口100做接触正放电10次后:静电接触放电电压为4kv时,在第一电容c1的两个极板存储了5.4x10-7c×

10=5.4x10-6

c的正电荷量;对输入/输出接口100再接触负放电10次时,存储在第一电容c1的两个极板5.4x10-7

c的电荷量在10次接触负放电时,将静电枪是泄放出来负电荷中和。也就是静电枪接触放电电压为-4kv,10次产生5.4x10-6

c的负电荷量,会与静电枪接触放电电压为4kv,10次产生5.4x10-6

c的正电荷量中和,对整个电路没有任何破坏作用。

[0182]

静电接触放电电压为6kv时,在第一电容c1的两个极板存储了8.1x10-7c×

10=8.1x10-6

c的正电荷量;对输入/输出接口100再接触负放电10次时,存储在第一电容c1的两个极板8.1x10-6

c的电荷量在10次接触负放电时,将静电枪是泄放出来负电荷中和。也就是静电枪接触放电电压为-6kv,10次产生8.1x10-7c×

10=8.1x10-6

c的负电荷量,会与静电枪接触放电电压为6kv,10次产生8.1x10-7c×

10=8.1x10-6

c的正电荷量中和,对整个电路没有任何破坏作用。

[0183]

静电接触放电电压为8kv时,在第一电容c1的两个极板存储了10.8x10-7c×

10=10.8x10-6

c的正电荷量;对输入/输出接口100再接触负放电10次时,存储在第一电容c1的两个极板10.8x10-6

c的电荷量在10次接触负放电时,将静电枪是泄放出来负电荷中和。也就是静电枪接触放电电压为-8kv,10次产生10.8x10-7c×

10=10.8x10-6

c的负电荷量,会与静电枪接触放电电压为8kv,10次产生10.8x10-7c×

10=10.8x10-6

c的正电荷量中和,对整个电路没有任何破坏作用。

[0184]

静电接触放电电压为10kv时,在第一电容c1的两个极板存储了16.2x10-7c×

10=16.2x10-6

c的正电荷量;对输入/输出接口100再接触负放电10次时,存储在第一电容c1的两个极板16.2x10-6

c的电荷量在10次接触负放电时,将静电枪是泄放出来负电荷中和。也就是静电枪接触放电电压为-8kv,10次产生16.2x10-7c×

10=16.2x10-6

c的负电荷量,会与静电枪接触放电电压为8kv,10次产生16.2x10-7c×

10=16.2x10-6

c的正电荷量中和,对整个电路没有任何破坏作用。

[0185]

第二静电防护器vd2的一端与磁珠l1连接,另一端与第二电容c2连接。经第一静电防护器vd1吸收后,电流还有10%到15%的残压注入到磁珠l1,产生瞬间电流i4,但磁珠l1对于瞬间电流i4有较大交流阻抗,类似于电感特性“总是阻碍电流的突变”,其中一部分会以热损耗方式消耗掉,另外一部分被阻止通过磁珠l1,返回到第一静电防护器vd1,充分吸收,泄放至第一电容c1中存储起来。

[0186]

极小部分瞬间电流i7通过磁珠l1,如果静电的残压超过第二静电防护器vd2的击穿电压,第二静电防护器vd2会击穿,最后泄放到pcb地铜箔或pcb地线23,此时注入到pcb地铜箔或pcb地线23的静电电流i7较小,产生残压较小,对整个pcb板中的敏感信号走线影响极其微弱。

[0187]

第二静电防护器vd2的另一端与第二电容c2连接,经第二静电防护器vd2吸收后的静电产生较低残压,经第二电容c2隔离后,已经是非常微弱,对受保护的组件200的影响及对外接输入/输出接口100的影响非常微弱。

[0188]

第二电容c2容值非常重要,选择越小的容值,能隔离高中低频段的静电的分量,选择越大的容值,只能隔离中低频段的静电的分量,选择越小的容值能隔离静电的分量越多,但同时会传输信号的也有一定范围的隔离,可能会影响信号质量,因此要根据实际信号频率情况来定。

[0189]

在第二电容c2到受保护的组件200之间串接了一个第一电阻r1,第一电阻r1相当于一个分压模块,经过第二电容c2隔中低频静电残压后,在第二电容c2添加串联分压第一电阻r1可以将静电的残压进行分压,进一步减小对受保护的组件200的影响。经串联分压电阻分压后,可以将静电的残压抑制约2%~3%分量。

[0190]

图12为本技术又一实施例提供的静电防护电路的简图。请参照图12,与图7所示静电防护电路不同的是,本实施例中第一静电防护器的第二端与pcb地铜箔或pcb地线23之间设有多个并联的第一电容c1(图中仅示出了四个第一电容c1)。

[0191]

具体来说,本实施例中的第一电容c1包括c4、c5、c6、c7,且c4、c5、c6、c7、r2之间采用并联方式后再与第一静电防护器vd1串联,电路的其它部分与图7所示电路相同。

[0192]

本实施例中可以将c4选为30pf陶瓷电容,30pf陶瓷电容的谐振频率点约为1.67ghz,谐振频率点的阻抗约为89mω,刚好覆盖接触放电的放电最小周期为0.6ns~1ns时的干扰频率1ghz~1.667ghz,因为陶瓷电容的在谐振点的阻抗最小,此时表现为电阻的特性,它在谐振点吸收效果是最佳的。也就是30pf陶瓷电容在工作带宽范围内可以吸收1ghz~1.667ghz接触放电的放电的干扰频段。

[0193]

可以将c5选为100nf陶瓷电容,100nf陶瓷电容的谐振频率点约为38mhz,谐振频率点的阻抗约为34mω,刚好覆盖接触放电的放电周期为30ns时的干扰频率33.33mhz,因为陶瓷电容的在谐振点的阻抗最小,此时表现为电阻的特性,它在谐振点吸收效果是最佳的。

[0194]

可以将c6选为1μf陶瓷电容,1μf陶瓷电容的谐振频率点约为13mhz,谐振频率点的阻抗约为15mω,刚好覆盖接触放电的放电周期为60ns时的干扰频率16.67mhz,因为陶瓷电容的在谐振点的阻抗最小,此时表现为电阻的特性,它在谐振点吸收效果是最佳的。

[0195]

可以将c7选为阻抗频率特性曲线图呈“u”形(工作带宽较宽)钽电解电容、铝电解电容,铝固态电容、钽固态电容,而用于满足吸收90%静电枪中电荷量最小容量,同时100nf陶瓷电容的谐振频率点约为38mhz,可以覆盖接触放电的放电周期为30ns时的干扰频率33.33mhz。也就是0.6ns~1ns时接触放电的干扰频率1ghz~1.667ghz的接触放电产生静电荷是被c4(30pf陶瓷电容)耦合到pcb地铜箔或pcb地线23,同时存储在c4的两个极板上,同时向并联c4两端的c5、c6、c7、r2放电;周期为30ns时的干扰频率33.33mhz的接触放电产生静电荷是被c5(100nf陶瓷电容)耦合到pcb地铜箔或pcb地线23,同时存储在c5的两个极板上,同时向并联c5两端的c4、c6、c7、r2放电,最小周期为60ns时的干扰频率16.67mhz的接触

放电产生静电荷是被c6(1μf陶瓷电容)耦合到pcb地铜箔或pcb地线23,同时存储在c6的两个极板上,同时向并联c6两端的c4、c5、c7、r2放电;而c7的容值较大,esr较大、esl较大,只做存储电容使用,c7做为备选电容也可以省去,因为c6容值已经满足满足吸收90%静电枪中电荷量最小容量;r2因阻值非常大,对高压大电流放电几乎没有影响,它只是长时间放电损耗元件,产生损耗功率计算如下:p=i2r,其中i为流过r2中的电流。

[0196]

图13为电容的等效模型。请参照图13,理想电容器就是介质损耗为零,没有漏电,分布电感为零,频率特性一致,可以输出趋于无穷大的电流,所以趋于零的时间就可以充满电。而理想电容是不存在,实际电容包含等效串联电阻esr(r11)和等效串联电感(esl)l11、电容c11组成,产生的原因是生产工艺以及封装体积大小导致的问题,比如引脚引线产生的寄生电感(也就是串联等效电感esl),由于所有物质都不是超导体,所以有阻抗。静电在泄放过程中(例如空气放电、接触放电)会生产不同频段的尖峰,不同频段的尖峰要对应不同谐振点的电容来吸收,也就是不同频段静电的尖峰在第一时间给用不同谐振点的电容充电,同时各电容还要对其它谐振点的电容进行放电。电容的充电、放电响应速度与电容的esr(串联等效电阻)、esl(串联等效电感)有关,经多次实验得到结论:静电的噪声频段越高,要求电容的esl越小,对电容的esr要求不高;静电的噪声频段越低,要求电容的esr越小,对电容的esl要求不高。

[0197]

对于接触放电的放电周期为60ns时的干扰频率16.67mhz对应1μf陶瓷电容(谐振频率点约为13mhz,谐振频率点的阻抗约为15mω),16.67mhz频率的干扰属于低频,影响1μf陶瓷电容的充电和放电速度是最主要因素是电容的esr,电容的esl不是主要因素。要求1μf陶瓷电容的esr越小对接触放电的放电周期为60ns时的干扰频率16.67mhz吸收效果越好。

[0198]

对于接触放电的放电周期为30ns时的干扰频率33.33mhz,对应是100nf陶瓷电容(谐振频率点约为38mhz,谐振频率点的阻抗约为34mω),33.33mhz频率的干扰属于中低频噪声,影响100nf陶瓷电容的充电和放电速度是最主要因素是电容的esr,但esl也占次要因素,要求100nf陶瓷电容的esr越小对接触放电的放电周期为30ns时的干扰频率33.33mhz吸收效果越好,同时100nf陶瓷电容的esl也要关注。

[0199]

对于接触放电的放电周期为0.6ns~1ns时的干扰频率1ghz~1.667ghz,对应是30pf陶瓷电容(谐振频率点约为1.67ghz,谐振频率点的阻抗约为89mω),1ghz~1.667ghz频率的干扰属于高频噪声,影响30pf陶瓷电容的充电和放电速度是最主要因素是电容的esl,esr不是重点,则要求30pf陶瓷电容的esl越小对接触放电的放电周期为0.6ns~1ns时的干扰频率1ghz~1.667ghz吸收效果越好。

[0200]

图14-图20为不同容值陶瓷电容的阻抗频率曲线图。请参照图14-图20,陶瓷电容的阻抗频率特性曲线呈“v”形。图14给出了10pf陶瓷电容阻抗频率曲线图,阻抗频率曲线最低点表示谐振频率点,10pf陶瓷电容的谐振频率点约为2.8ghz,谐振频率点的阻抗约为400mω,此时阻抗最小;谐振点之前为容性,超过谐振点,电容逐渐成为感性。图15给出了30pf陶瓷电容阻抗频率曲线图,30pf陶瓷电容的谐振频率点约为1.56ghz,谐振频率点的阻抗约为89mω,此时阻抗最小;谐振点之前为容性,超过谐振点,电容逐渐成为感性。图16给出了100pf陶瓷电容阻抗频率曲线图,100pf陶瓷电容的谐振频率点约为1.25ghz,谐振频率点的阻抗约为89mω,此时阻抗最小;谐振点之前为容性,超过谐振点,电容逐渐成为感性。图17给出了1nf陶瓷电容阻抗频率曲线图,1nf陶瓷电容的谐振频率点约为420mhz,谐振频

率点的阻抗约为280mω,此时阻抗最小;谐振点之前为容性,超过谐振点,电容逐渐成为感性。图18给出了10nf陶瓷电容阻抗频率曲线图,10nf陶瓷电容的谐振频率点约为85mhz,谐振频率点的阻抗约为15mω,此时阻抗最小;谐振点之前为容性,超过谐振点,电容逐渐成为感性。图19给出了100nf陶瓷电容阻抗频率曲线图,100nf陶瓷电容的谐振频率点约为38mhz,谐振频率点的阻抗约为34mω,此时阻抗最小;谐振点之前为容性,超过谐振点,电容逐渐成为感性。图20给出了1μf陶瓷电容阻抗频率曲线图。1μf陶瓷电容的谐振频率点约为13mhz,谐振频率点的阻抗约为15mω,此时阻抗最小;谐振点之前为容性,超过谐振点,电容逐渐成为感性。

[0201]

图21为150μf钽电容阻抗频率曲线图。请参照图21,150μf钽电容阻抗频率特性曲线图呈“u”形,谐振点工作带宽范围较大。从图中可以看到,它在100khz到1mhz的之间阻抗在30.5mω,在10khz到10mhz的之间的esr约在60mω~70mω,esr最低可达28.6mω,esl约为2.4nh。

[0202]

图22为本技术又一实施例提供的静电防护电路的简图;请参照图22,与图7所示电路比较,本实施例的差异在于将图7中的三角管防护器vd2(第二静电防护器vd2)改为图22中两个分立的二极管:vd4、vd5,二极管vd5阳极a、二极管vd4阴极k与信号线300电连接;而二极管vd4阳极a与供电电压(vcc)410电连接,二极管vd5阴极k与pcb地铜箔或pcb地线23连接;如果二极管vd4、二极管vd5压降为0.7v(例如硅管),则信号线300的钳位电压在-0.7v~vcc+0.7v之间。当在输入/输出接口100注入接触放电为2kv~8kv正电压时,信号线300的钳位电压在0v~vcc+0.7v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常,当在输入/输出接口100注入接触放电为2kv~8kv负电压时,信号线300的钳位电压在-0.7v~0v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常。

[0203]

如果二极管vd4、二极管vd5压降为0.3v(例锗管),则信号线300的钳位电压在-0.3v~vcc+0.3v之间。当在输入/输出接口100注入接触放电为2kv~8kv正电压时,信号线300的钳位电压在0v~vcc+0.3v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常,当在输入/输出接口100注入接触放电为2kv~8kv负电压时,信号线300的钳位电压在-0.3v~0v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常。

[0204]

二极管vd4、二极管vd5具体选硅管,还是锗管,根据实际应用情况来定,原则是二极管vd4、二极管vd5的压降要略超过信号线300的工作电平,二极管vd4、二极管vd5的压降小于信号线300的工作电平阀值,就会导致信号线300的信号被“削顶”,二极管vd4、二极管vd5的压降远远大于信号线300的工作电平阀值,就会有较高的静电残压注入c2、r1、受保护的组件200,导致等后级电路的功能异常或损坏。

[0205]

图23为本技术又一实施例提供的静电防护电路的简图;请参照图23,与图22所示电路比较,本实施例的差异在于将图22中二极管vd5阴极k接pcb地铜箔或pcb地线23,也就是将二极管vd4阴极k与二极管vd5阳极a并联后与信号线300电连接,将二极管vd4阳极a与二极管vd5阴极k并联后与pcb地铜箔或pcb地线23电连接。

[0206]

如果二极管vd4、二极管vd5压降为0.7v(例硅管),则信号线300的钳位电压在-0.7v~0.7v之间。当在输入/输出接口100注入接触放电为2kv~8kv正电压时,信号线300的

钳位电压在0v~0.7v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常,当在输入/输出接口100注入接触放电为2kv~8kv负电压时,信号线300的钳位电压在-0.7v~0v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常。

[0207]

如果二极管vd4、二极管vd5压降为0.3v(例锗管),则信号线300的钳位电压在-0.3v~0.3v之间。当在输入/输出接口100注入接触放电为2kv~8kv正电压时,信号线300的钳位电压在0v~0.3v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常,当在输入/输出接口100注入接触放电为2kv~8kv负电压时,信号线300的钳位电压在-0.3v~0v之间,保护c2、r1、受保护的组件200等后级电路不会损坏,也不容易产生功能异常。

[0208]

另外,第二静电防护器vd2具体选硅管,还是锗管,但必须是开关速度较高的器件,这样第二静电防护器响应速度才赶得上0.6ns静电泄放的响应速度。第二静电防护器vd2也可以选择esd静电二极管、tvs二极管、开关二极管、tss二极管、压敏电阻、气体放电管、稳压二极管,优选esd静电二极管。

[0209]

图24为poc电感(同轴电缆供电电感)频率特性曲线图。请参照图24,本实施例的电感的谐振点在116mhz左右,电感在谐振点的阻抗是最高,约为20kω;在1.05ghz左右的的阻抗约为1kω,也就是poc电感在接触放电静电干扰频段都会表现较高阻抗,也就是poc电感对接触放电静电干扰频段16.67mhz~1.667ghz都表现出较高阻抗。如果对图7、图8、图9、图22、图23中的磁珠l1替换为电感,同样可以达到相同的效果。需要说明的是poc电感只适合应用在传输低频信号或低速信号,不适合传输高速信号或高频信号,以免poc电感在传输高速信号或高频信号时,阻抗过高,导致高速信号或高频信号的插损过大、阻抗跳变,导致信号质量发生畸变。

[0210]

图25为本技术又一实施例提供的静电防护电路的简图。请参照图25,与图7所示静电防护电路不同的是,本实施例中将图7中的第一电阻r1去掉,也就是受保护的组件200通过信号线300直接与磁珠l1的第2脚、第二静电防护器vd2的第3脚连接,电路的其它部分与图7所示电路相同。与图7比较,本实施例可以节省一个电阻(第一电阻r1),进一步降低了成本,同时节省了pcb板空间,在高密pcb板中,这个非常实用。同时它可以降低第一电阻r1对在信号线300传输信号的损耗。第一静电防护器vd1和第一电容c1、磁珠l1、第二静电防护器vd2、第二电容c2、第二电阻r2的功能及作用与图7是一样的,不再重复描述。

[0211]

图26为本技术又一实施例提供的静电防护电路的简图。请参照图26,与图25所示静电防护电路不同的是,本实施例中将图25中的第二电容c2去掉,也就是受保护的组件200通过信号线300直接与磁珠l1的第2脚、第二静电防护器vd2的第3脚连接,电路的其它部分与图25所示电路相同。与图25比较,本实施例可以节省一个电容(第二电容c2),进一步降低了成本,同时节省了pcb板空间,在高密pcb板中,这个非常实用。同时它可以降低第二电容c2对在信号线300中低频信号的阻抗,也就是去掉第二电容c2后,可以在信号线300/信号线303传输极低频信号,甚至是直流信号。本实施例中的第一静电防护器vd1、第一电容c1、磁珠l1、第二静电防护器vd2的功能及作用与图25中的方案是一样的,不再重复描述。

[0212]

图27为本技术又一实施例提供的静电防护电路的简图。请参照图27,与图26所示静电防护电路不同的是,本实施例中将图26中的第二静电防护器vd2去掉,也就是磁珠l1的

第2脚与输入/输出接口100连接,电路的其它部分与图26所示电路相同。与图26比较,本实施例可以节省一个静电防护器(第二静电防护器vd2),进一步降低了成本,同时节省了pcb板空间,在高密pcb板中,这个非常实用。同样可以在信号线300/信号线303极低频信号,甚至是直流信号。本实施例中的第一静电防护器vd1、第一电容c1、第二电阻r2的功能及作用与图26中的方案是一样的,不再重复描述。

[0213]

图28为本技术又一实施例提供的静电防护电路的简图。请参照图28,与图27所示静电防护电路不同的是,本实施例中将图27中的磁珠l1去掉,也就是受保护的组件200通过信号线310直接与输入/输出接口100连接,电路的其它部分与图27所示电路相同。电路的其它部分与图27所示电路相同。与图27中方案比较,本实施例可以节省一个磁珠(磁珠l1),进一步降低了成本,同时节省了pcb板空间,在高密pcb板中,这个非常实用。可以在信号线300/信号线303极低频信号,甚至是直流信号,也可以传输高速信号和高频信号(例如射频信号)。本实施例中的第一静电防护器vd1、第二电阻r2、第一电容c1的功能及作用与图27中的方案是一样的,不再重复描述。

[0214]

图29为本技术又一实施例提供的静电防护电路的简图。请参照图29,与图7所示静电防护电路不同的是,本实施例中将图7中的第二静电防护器vd2去掉,电路的其它部分与图7所示电路相同。与图7中方案比较,本实施例可以节省一个静电防护器(第二静电防护器vd2),进一步降低了成本,同时节省了pcb板空间,在高密pcb板中,这个非常实用。可以在信号线300/信号线303极低频信号,甚至是直流信号。本实施例中的第一电阻r1、第二电容c2、第一电容c1、磁珠l1、第二电阻r2、第一静电防护器vd1的功能及作用与图7中的方案是一样的,不再重复描述。

[0215]

图30为本技术又一实施例提供的静电防护电路的简图。请参照图30,与图29所示静电防护电路不同的是,本实施例中将图29中的第二电容c2、磁珠l1去掉,也就是第一电阻r1的第1脚与受保护的组件200,将第一电阻r1的第2脚与通过信号线303与第一静电防护器vd1的第1脚连接,电路的其它部分与图29所示电路相同。与图29中方案比较,本实施例可以节省一个电容(第二电容c2)、磁珠(磁珠l1),进一步降低了成本,同时节省了pcb板空间,在高密pcb板中,这个非常实用。可以在信号线300/信号线303极低频信号,甚至是直流信号,也可以传输高速信号和高频信号(例如射频信号)。本实施例中的第一电阻r1、第一电容c1、第二电阻r2、第一静电防护器vd1的功能及作用与图29中的方案是一样的,不再重复描述。

[0216]

图31为本技术又一实施例提供的静电防护电路的简图。请参照图31,与图7所示静电防护电路不同的是,本实施例中将图7中的第二电容c2去掉,也就是第一电阻r1通过信号线300直接与磁珠l1的第2脚、第二静电防护器vd2的第3脚连接,电路的其它部分与图7所示电路相同。与图7比较,本实施例可以节省一个电容(第二电容c2),进一步降低了成本,同时节省了pcb板空间,在高密pcb板中,这个非常实用。同样可以在信号线300/信号线303极低频信号,甚至是直流信号。第一静电防护器vd1和第一电容c1、磁珠l1、第二静电防护器vd2、第一电阻r1、第二电阻r2的功能及作用与图7是一样的,不再重复描述。

[0217]

图40为本技术又一实施例提供的静电防护电路的简图。请参照图40,与图23所示静电防护电路不同的是,本实施例中将图23中的第二静电防护器中的二极管vd4和二极管vd5替换成双向静电防护器vd2。双向静电防护器vd2(第二静电防护器)的击穿阀值电压要略高于信号线300的工作电压,而第一静电防护器vd1要略高于信号线303的工作电压,避免

信号线300及信号线303正常工作时,第一静电防护器vd1、双向静电防护器vd2(第二静电防护器)异常造成信号被“削顶”,导致信号发生畸变。第一电阻r1去掉,也就是双向静电防护器vd2通过信号线300直接与磁珠l1的第2脚、第二电容c2的第2脚连接,电路的其它部分与图23所示电路相同。与图23比较,本实施例可以节省第二静电防护器中其中一个二极管(例如二极管vd4或二极管vd5),进一步降低了成本,同时节省了pcb板空间,在高密pcb板中,这个非常实用。第一静电防护器vd1和第一电容c1、磁珠l1、第二电容c2、第二电阻r2的功能及作用与图23是一样的,不再重复描述。

[0218]

图32为本技术又一实施例提供的静电防护电路的简图;图33为图32的局部剖视图。请参照图32和图33,图32是图28在路由器产品的具体应用实例;受保护的组件200包括wifi芯片157、巴伦电路组件171、wifi芯片匹配组件153、fem芯片176、wifi射频滤波器152、wifi射频滤波器匹配组件151、天线匹配组件173。wifi芯片157通过射频走线172与巴伦电路组件171连接;巴伦电路组件171通过射频走线154与wifi芯片匹配组件153连接;wifi芯片匹配组件153通过射频走线155与fem芯片176连接;fem芯片176通过射频走线175与wifi射频滤波器152连接;wifi射频滤波器152与通过射频走线156与wifi射频滤波器匹配组件151连接;wifi射频滤波器匹配组件151通过射频走线174与天线匹配组件173连接;天线匹配组件173通过信号线310(在图32中的信号线310为射频走线)与第一静电防护器vd1的第1脚、输入/输出接口100(在图32中的输入/输出接口100为sma母座)连接。该路由器采用外置天线184,外置天线184突出在产品外部,且sma母座100(输入/输出接口100)如果裸露在产品外部,则需要做4kv~8kv接触放电,sma母座100(输入/输出接口100)与外置天线184接口位置有缝隙:例如外置天线旋转接口181与sma母座100(输入/输出接口100)有缝隙,外置天线184的旋转接口181与塑胶壳185的缝隙(内置有天线电缆182),在产品有缝隙位置需要做空气放电,这样会引入在外置天线184引入空气放电。第一静电防护器vd1、第一电容c1、第二电阻r2要尽可能靠近sma母座100,尽可能将外置天线184引入空气放电在信号线300带来的静电泄放在电容c1中存储,天线匹配组件173尽可能靠近第一静电防护器vd1、输入/输出接口100(在图32中的输入/输出接口100为sma母座)。sma母座100焊接pcb板170靠近外壳180的位置,也就是在sma母座100位置将外壳180开孔526,用于安装外置天线184的旋转接口181。如果外壳180为塑胶壳体,在外壳180开孔526,就会产生缝隙,而sma母座100是金属材料,如果人体手指可以明显触摸到,则需要做4kv~8kv的接触放电,如果人体手指不能直接触摸到,则要做6kv~15kv的空气放电,此时不管是4kv~8kv的接触放电,还是6kv~15kv的空气放电,都会从sma母座100向信号线300(在图32中的信号线310为射频走线)注入高压静电。

[0219]

如果不添加第一静电防护器vd1、第一电容c1、第二电阻r2组成的静电防护电路,外置天线引入空气放电经信号线300(在图32中的信号线310为射频走线)注入天线匹配组件173,导致wifi射频信号功能异常;经射频走线174注入wifi射频滤波器匹配组件151,导致wifi射频信号功能异常;经射频走线156注入wifi射频滤波器152,导致wifi射频信号功能异常;经射频走线175注入fem芯片176,导致wifi射频信号功能异常;经射频走线155注入wifi芯片匹配组件153,导致wifi射频信号功能异常;经射频走线154注入巴伦电路组件171,导致wifi射频信号功能异常;经射频走线155注入wifi芯片157,导致wifi射频信号功能异常;甚至wifi射频滤波器匹配组件151、wifi射频滤波器152、fem芯片176、wifi芯片匹

配组件153、巴伦电路组件171、wifi芯片157都有被静电骚扰导致永久损坏的风险,因此在输入/输出接口100(在图32中的输入/输出接口100为sma母座)与天线匹配组件173添加第一静电防护器vd1、第一电容c1、第二电阻r2组成的静电防护电路,可以最大限度将来自外置天线184引入空气放电或接触放电带来的静电对wifi射频滤波器匹配组件151、wifi射频滤波器152、fem芯片176、wifi芯片匹配组件153、巴伦电路组件171、wifi芯片157中射频信号的影响(例如丢包,死机等异常现象),同时保护wifi射频滤波器匹配组件151、wifi射频滤波器152、fem芯片176、wifi芯片匹配组件153、巴伦电路组件171、wifi芯片157不会被静电损坏。

[0220]

外置天线184的塑胶壳185设置了辐射体183,而辐射体183通过天线电缆182与外置天线184的旋转接口181连接)。外置天线旋转接口181(也就是sma公座)与路由器中pcb板170中的sma母座紧密结合后,wifi芯片157调制后的射频信号经巴伦电路组件171、wifi芯片匹配组件153、fem芯片176、wifi射频滤波器152、wifi射频滤波器匹配组件151、天线匹配组件173、sma母座100(在图32中的输入/输出接口100为sma母座)通过外置天线184谐振,朝周围设备发送无线电波信号。

[0221]

以4层pcb板为例,wifi芯片157的地管脚503、巴伦电路组件171的地管脚(图32和图33未标示)、wifi外置天线旋转接口181芯片匹配组件153的地管脚(图32和图33未标示)、fem芯片176的地管脚(图32和图33未标示)、wifi射频滤波器152的地管脚、wifi射频滤波器匹配组件151的地管脚(图32和图33未标示)、天线匹配组件173的地管脚(图32和图33未标示)、sma母座100分别通过地孔504、地孔505、地孔506、地孔507、地孔508、地孔509、地孔520与top层(顶层)500的地铜箔514、第2层的地铜箔510、第3层的地铜箔522、bottom层(底层)501的地铜箔513连接,实现与pcb地铜箔或pcb地线23(指整板地铜箔)连接。

[0222]

而在天线匹配组件173与sma母座100之间添加第一静电防护器vd1、第一电容c1、第二电阻r2组成的静电防护电路,可以将来自外置天线184产生的静电吸收存储在第一电容c1中,而不是直接泄放到top层(顶层)500的地铜箔514、第2层的地铜箔510、第3层的地铜箔522、bottom层(底层)501的地铜箔513,导致静电通过地孔504、地孔505、地孔506、地孔507、地孔508、地孔509、地孔520分别注入wifi芯片157的地管脚503、巴伦电路组件171的地管脚(图32和图33未标示)、wifi芯片匹配组件153的地管脚(图32和图33未标示)、fem芯片176的地管脚(图32和图33未标示)、wifi射频滤波器152的地管脚、wifi射频滤波器匹配组件151的地管脚(图32和图33未标示)、天线匹配组件173的地管脚(图32和图33未标示)、sma母座100等,导致射频信号回流路径受静电的骚扰,而导致wifi芯片157、巴伦电路组件171、wifi芯片匹配组件153、fem芯片176、wifi射频滤波器152、wifi射频滤波器匹配组件151、天线匹配组件173、sma母座100中的射频信号工作异常,例如wifi信号出现丢包、死机等异常现象。

[0223]

另外,由于第一静电防护器vd1选取结电容非常小的esd防护器件,例如选pf级别的esd防护器件。请参考图32,第一静电防护器vd1的结电容c10与第一电容c1串联后的再并联在信号线310(信号线310在图32中为射频走线)与pcb地铜箔或pcb地线23之间,那么第一静电防护器vd1的结电容c10与第一电容c1串联的等效电容c11计算为:

[0224]

[0225]

也就是第一静电防护器vd1的结电容c10与第一电容c1串联的等效电容c11要小于第一静电防护器vd1的结电容c10,c11也要远远小于第一电容c1。因此只要第一静电防护器vd1选择pf级别的esd防护器件,第一静电防护器vd1的结电容c10与第一电容c1串联的等效电容c11比单独第一静电防护器vd1的结电容c10还要小,因此在天线匹配组件173与sma母座100之间添加第一静电防护器vd1、第一电容c1、第二电阻r2组成的静电防护电路,不影响信号线310的分布参数(分布电容、分布电感),不会对信号线310(在图32、图33中信号线310为射频走线)中射频信号造成分布电容过大,因此不会影响射频信号的阻抗(如果分布电容过大,会导致信号线310阻抗明显变低),因为如果第一静电防护器vd1的分布参数变化(例如分布电容变大),会导致信号线310的阻抗变化(例如低于50欧

±

5欧阻抗),会导致信号线310中射频信号阻抗发生跳变,导致信号线310中射信号出现vswr(voltage standing wave ratio,电压驻波比)及s11(回波损耗)等一系列性能指标变差。

[0226]

同时由于第一静电防护器vd1的击穿电压的阀值略超过信号线310中射频信号的摆幅,因此外置天线184无静电通过sma母座100注入信号线310时,信号线310中的射频信号不会引起第一静电防护器vd1击穿导通,因此第一电容c1也不影响信号线310中的分布电容,也就是正常工作时,第一电容c1不影响信号线310的50欧的正常阻抗。

[0227]

参考图33,sma母座100(在图32中的输入/输出接口100为sma母座)为通孔连接器,在pcb板170的bottom面(底面)焊接来固定。第一静电防护器vd1的第1脚焊接在pcb板170上的焊盘160上,焊盘160与信号线310(在图32、图33中信号线310为射频走线)连接,且第一静电防护器vd1的第1脚及焊盘160要放在信号线310的主通道上,这样第一静电防护器vd1可以快速吸收来自外置天线184带来的静电。

[0228]

wifi芯片157、射频走线172、巴伦电路组件171、射频走线154、wifi芯片匹配组件153、射频走线155、fem芯片176、射频走线175、wifi射频滤波器152、射频走线156、wifi射频滤波器匹配组件151需要设置在屏蔽盖210内部,也就是屏蔽盖210覆盖wifi芯片157、射频走线172、巴伦电路组件171、射频走线154、wifi芯片匹配组件153、射频走线155、fem芯片176、射频走线175、wifi射频滤波器152、射频走线156、wifi射频滤波器匹配组件151,避免它们裸露在屏蔽盖外部,导致wifi的杂散超标。天线匹配组件173、静电防护器vd1的结电容c10与第一电容c1、第二电阻r2、sma母座100需要设置在屏蔽盖210的外部。

[0229]

图34为本技术又一实施例提供的静电防护电路的简图;图35为图34的局部剖视图。请参照图34和图35,其中图34是图28在车载设备802中的具体应用实例;受保护的组件200包括wifi芯片257(内置巴伦电路组件)、wifi射频滤波器251、天线匹配组件258。第一静电防护器vd1、第一电容c1、第二电阻r2组成静电防护电路。第一静电防护器vd1的第1脚与天线匹配组件258与输入/输出接口100(在图34和图35中的输入/输出接口100为天线馈点露铜)连接。

[0230]

wifi芯片257通过射频走线254与wifi射频滤波器251连接;wifi射频滤波器251通过信号线310(图34和图35中的信号线310为射频走线)与输入/输出接口100(在图34和图35中的输入/输出接口100为天线馈点露铜)连接;车载设备802采用内置pifa天线526,且pifa天线526的辐射体166固定在支架528上,从pifa天线526的辐射体166引出弹片167,通过弹片167的触点168与pcb板170中的馈点露铜100(在图34和图35中的输入/输出接口100为天线馈点露铜)接触,来实现pifa天线526与信号线310(在图34和图35中信号线310为射频走

线)连接。由于pifa天线526的辐射体166靠近塑胶壳体165的内侧,且在pifa天线526的辐射体166位置塑胶壳体165的外侧存在缝隙,按中国3c认证、欧盟的ce认证中,塑胶壳体存在缝隙位置需要做6kv~15kv空气放电,因此在pifa天线526附近空气放电产生的静电通过弹片167的触点168、天线馈点露铜100注入信号线310、天线匹配组件258、射频走线258、wifi射频滤波器251、射频走线254、wifi芯片257,会导致信号线310、天线匹配组件258、射频走线258、wifi射频滤波器251、射频走线254、wifi芯片257中的射频信号受到静电的干扰,导致功能异常(例如wifi信号出现丢包、死机等),甚至会导致天线匹配组件、wifi射频滤波器251、wifi芯片257损坏。

[0231]

在天线匹配组件258与输入/输出接口100之间添加第一静电防护器vd1、第一电容c1、第二电阻r2组成静电防护电路后,来自弹片167的触点168、天线馈点露铜100注入信号线310的静电,会经第一静电防护器vd1击穿导通,注入第一电容c1存储起来,再缓慢通过第二电阻r2消耗掉。

[0232]

而在天线匹配组件258与天线馈点露铜100之间添加第一静电防护器vd1、第一电容c1、第二电阻r2组成的静电防护电路,可以将来自天线馈点露铜100产生的静电吸收存储在第一电容c1中,而不是直接泄放到pcb板170top层(顶层)500的地铜箔514、第2层的地铜箔510、第3层的地铜箔522、bottom层(底层)501的地铜箔513,也就是最终都注入到pcb地铜箔或pcb地线23(地铜箔23为pcb板中整板地铜箔),导致静电通过地孔525、地孔524、地孔523分别注入wifi芯片匹配组件258的地管脚(图34和图35未标示)、wifi射频滤波器251的地管脚(图34和图35未标示)、wifi芯片257的地管脚527等,导致射频信号回流路径受静电骚扰,而导致wifi芯片257、wifi射频滤波器251、天线匹配组件258中的射频信号工作异常,例如wifi信号出现丢包、死机等异常现象。

[0233]

图36为本技术又一实施例提供的静电防护电路的简图。请参照图36,图36给出了车载设备802引出5v外接电源电缆800给外接设备801供电的应用场景。与图23比较,图36将第二静电防护器:二极管vd4、二极管vd5替换成静电防护器vd5(优选双向esd静电二极管、双向tvs二极管),将静电防护器vd5的2脚接pcb地铜箔或pcb地线23,而静电防护器vd5的1脚接电源线300(图23中信号线300,而图36中电源线300,差异在于信号线走线较细,而电源线较粗,需要满足通流和压降的要求)。同时去掉图23中的第一电阻r1、第二电容c2,而将图23中磁珠l1更换为poc电感l1。从电源转换组件200输出5v电源,经电源线300送至poc电感l1,再经电源线303(图23中信号线303,而图36中电源线303,差异在于信号线走线较细,而电源线较粗,需要满足通流和压降的要求)及第一静电防护器vd1+第一电容c1+第二电阻r2组成静电防护器电路送至焊盘100(在图36中的输入/输出接口100为焊盘100),焊盘100焊接了外接电源电缆800,外接电源电缆800引出至车载设备802外部给外接设备801供电。根据中国g6.2b/t1762标准(等同于国际标准iec61000-4-2),需要从外接电源电缆800注入4kv~8kv接触放电,车载设备802不能出现异常。当外接电源电缆800注入4kv~8kv接触放电时,来自外接电源电缆800、焊盘100、电源线303产生4kv~8kv高压静电会瞬间将第一静电防护器vd1击穿,绝大部分静电荷存储在第一电容c1内部的两个极板,残余一部分被poc电感l1反弹回第一静电防护器vd1,第一静电防护器vd1击穿,再次被第一电容c1存储在第一电容c1内部的两个极板,只有极少量静电荷穿过了poc电感l1,当电源线300残压超过静电防护器vd5阀值电压,静电防护器vd5瞬间击穿,将电源线300残压钳位在第二静电防护器

vd5阀值电压附近,保护电源转换组件200不会损坏,同时可以维持与电源线300在静电防护器vd5阀值电压附近,保护与电源线300相连接的其它器件供电电压不会突然出现异常导致车载设备802不能正常工作。第二静电防护器vd5击穿的阀值电压要略高于电源线300、第一静电防护器vd1击穿的阀值电压要略高于电源线303,避免电源转换组件200朝外接外接电源电缆800给外接设备801正常供电时,第二静电防护器vd5、第一静电防护器vd1导通产生误动作,导致对外供电异常。由于电源线303、电源线300中传输是直流电,所以第二静电防护器vd5、第一静电防护器vd1中的结电容不做特别要求,不影响电源转换组件200通过外接电源电缆800向外接设备801供电传输的正常工作。

[0234]

对于图7~图9、图12、图22、图23、图25~图35,如果在图7~图9、图12、图22、图23、图25~图27中的输入/输出接口100到受保护的组件200之间信号线(例如图7中的信号线300及信号线303、图32中的信号线310)需要传输高速信号(例如usb信号、hdmi信号、pcie信号、dvi信号、ldvs信号等)、高频信号(例如wifi射频信号、lte射频信号、蓝牙射频信号等)时,第一静电防护器vd1的结电容一定要低,例如usb2.0需要第一静电防护器vd1的结电容选择小于3pf,usb3.0需要第一静电防护器vd1的结电容选择小于0.3pf。

[0235]

如果在图7~图9、图11、图12、图22、图23、图25、图26、图31、图36、图40中输入/输出接口100到受保护的组件200之间信号线(例如图7中的信号线300及信号线303等)传输高速信号(例如usb信号、hdmi信号、pcie信号dvi信号等)、高频信号(例如wifi射频信号、lte射频信号、蓝牙射频信号等)时,第二静电防护器vd2的结电容一定要低,例如usb2.0需要第二静电防护器vd2的结电容选择小于3pf,usb3.0需要第二静电防护器vd2的结电容选择小于0.3pf。

[0236]

综上所述,图7~图9、图11、图12、图22、图23、图25~图32、图34、图36、图40中信号线300、信号线310、信号线303中传输信号(包括电源,电源属于直流信号)速率越高或频率越高,要求第一静电防护器vd1、第二静电防护器vd2的结电容越小。

[0237]

需要说明是,如果图7~图9、图11、图12、图22、图23、图25~图27、图29、图32、图36、图40中传输的差分信号(例如usb2.0、usb3.0、hdmi、lvds、mipi、pcie等接口差分线信号)时,可以将磁珠l1改成共模电感l1,用于滤去来pcb板内产生噪声(例如受保护的组件200等产生噪声),避免电子设备中emi辐射超标。

[0238]

需要说明的是,图7~图9、图11、图12、图23、图26~图36、图39、图40中仅以pcb地铜箔或pcb地线23做为接地举例说明,并不限定接地的具体形式,例如,可以是接pcb地铜箔、pcb地线、电池的负极、ac-dc适配器的次级输出端接地、机壳地、大地等任意一种。图37给出了pcb地线一种具体实施方式,图38给出了pcb地铜箔一种具体实施方式。

[0239]

在本技术的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”、“轴向”、“径向”、“周向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

[0240]

在本技术中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关

系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本技术中的具体含义。

[0241]

需要说明的是,在本技术的描述中,术语“第一”、“第二”仅用于方便描述不同的部件,而不能理解为指示或暗示顺序关系、相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。

[0242]

本技术中各实施例或实施方式采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分相互参见即可。

[0243]

在本技术的描述中,参考术语“一个实施方式”、“一些实施方式”、“示意性实施方式”、“示例”、“具体示例”、或“一些示例”等的描述意指结合实施方式或示例描述的具体特征、结构、材料或者特点包含于本技术的至少一个实施方式或示例中。在本技术中,对上述术语的示意性表述不一定指的是相同的实施方式或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施方式或示例中以合适的方式结合。

[0244]

最后应说明的是:以上各实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述各实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1