半导体结构及其形成方法与流程

本公开涉及半导体,涉及但不限于一种半导体结构及其形成方法。

背景技术:

1、随着半导体器件尺寸的不断缩小,栅极结构的栅极诱导漏极漏电流(gateinduced drain leakage,gidl)越来越大,导致栅极结构的控制能力越来越弱,半导体器件的性能越来越差。

技术实现思路

1、有鉴于此,本公开实施例提供一种半导体结构及其形成方法。

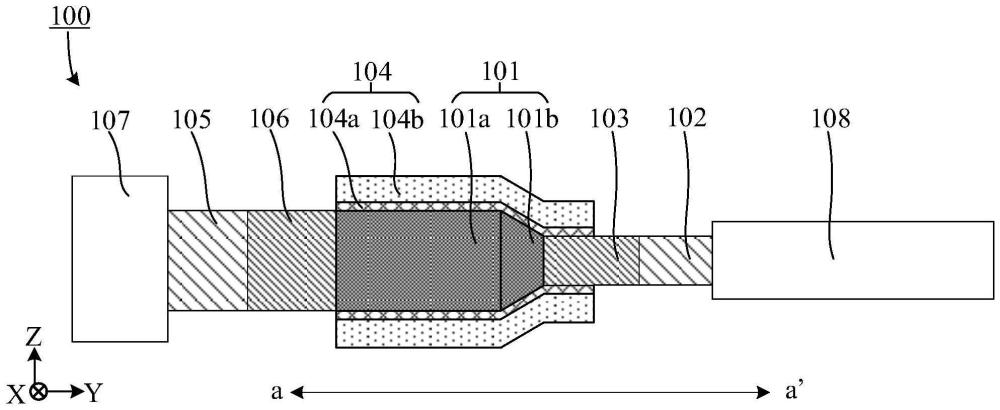

2、第一方面,本公开实施例提供一种半导体结构,包括:

3、衬底;

4、位于所述衬底表面、且沿第一方向和第三方向阵列排布的存储单元;所述存储单元至少包括沿第二方向排布的沟道结构和漏极;所述沟道结构包括第一沟道区和第二沟道区;所述沟道结构的主体材料的电子迁移率大于所述漏极的主体材料的电子迁移率;

5、所述第二沟道区与所述漏极相接,且所述第二沟道区的尺寸小于或者等于所述第一沟道区的尺寸。

6、在一些实施例中,所述存储单元还包括:位于所述漏极与所述第二沟道区之间的第一轻掺杂区、以及覆盖所述沟道结构和所述第一轻掺杂区表面的栅极结构;

7、所述栅极结构包括栅极介质层、以及位于所述栅极介质层表面的栅极导电层;

8、所述第二沟道区的尺寸沿朝向所述第一轻掺杂区的方向递减,且所述第一轻掺杂区的尺寸等于所述第二沟道区的最小尺寸。

9、在一些实施例中,所述存储单元还包括源极、以及位于所述源极与所述第一沟道区之间的第二轻掺杂区;

10、所述第二轻掺杂区的尺寸等于所述第一沟道区的尺寸。

11、在一些实施例中,所述沟道结构还包括与所述第一沟道区相接的第三沟道区;所述存储单元还包括源极、以及位于所述源极与所述第三沟道区之间的第二轻掺杂区;

12、其中,所述第三沟道区的尺寸沿朝向所述第二轻掺杂区的方向递减,且所述第三沟道区的主体材料的电子迁移率大于所述源极的主体材料的电子迁移率;所述第二轻掺杂区的尺寸等于所述第三沟道区的最小尺寸。

13、在一些实施例中,所述第一轻掺杂区的掺杂类型与所述第二轻掺杂区的掺杂类型相同;

14、所述第一轻掺杂区的掺杂类型与所述第一沟道区的掺杂类型相反,或者,所述第一轻掺杂区的掺杂类型与所述第一沟道区的掺杂类型相同,且所述第一轻掺杂区的掺杂浓度大于或者等于所述第一沟道区的掺杂浓度。

15、在一些实施例中,所述源极的尺寸等于所述第二轻掺杂区的尺寸;

16、且所述漏极的尺寸等于所述第一轻掺杂区的尺寸。

17、在一些实施例中,所述第一方向和所述第二方向为所述衬底所在平面内的任意两个方向,所述第三方向垂直于所述衬底所在的平面;

18、所述存储单元还包括与所述源极相接的位线结构,与所述栅极结构相接的字线结构,以及与所述漏极相接、且沿所述第二方向延伸的电容结构;

19、其中,所述位线结构沿所述第一方向与所述第三方向中的一者延伸,所述字线结构沿所述第一方向与所述第三方向中的另一者延伸。

20、第二方面,本公开实施例提供一种半导体结构的形成方法,所述方法包括:

21、提供衬底;

22、在所述衬底表面形成沿第一方向和第三方向阵列排布存储单元;所述存储单元至少包括沿第二方向排布的沟道结构和漏极;所述沟道结构包括第一沟道区和第二沟道区;所述沟道结构的主体材料的电子迁移率大于所述漏极的主体材料的电子迁移率;

23、其中,所述第二沟道区与所述漏极相接,且所述第二沟道区的尺寸小于或者等于所述第一沟道区的尺寸。

24、在一些实施例中,所述存储单元还包括源极;在所述衬底表面形成沿第一方向和第三方向阵列排布存储单元,包括:

25、在所述衬底表面形成沿所述第一方向和所述第三方向阵列排布、且沿所述第二方向延伸的初始有源条;

26、在所述初始有源条中形成初始沟道结构;所述初始沟道结构位于沿所述第二方向间隔排列的第一初始有源条和第二初始有源条之间,且所述初始沟道结构的主体材料的电子迁移率大于所述初始有源条的主体材料的电子迁移率;

27、处理所述初始沟道结构,形成所述沟道结构;

28、在所述第一初始有源条和所述第二初始有源条中分别形成所述漏极和所述源极。

29、在一些实施例中,所述处理所述初始沟道结构,形成所述沟道结构,包括:

30、在所述初始有源条和所述初始沟道结构的表面形成具有第一预设图案的第一光阻层;所述第一预设图案暴露出所述第二初始有源条、以及与所述第二初始有源条相接触的部分所述初始沟道结构;

31、刻蚀暴露出的所述初始沟道结构和所述第二初始有源条,对应形成所述第二沟道区和第二有源条;其中,未被刻蚀的初始沟道结构构成所述第一沟道区;所述第二沟道区的尺寸沿朝向所述第二有源条的方向递减。

32、在一些实施例中,所述沟道结构还包括:第三沟道区;所述方法还包括:

33、在形成第二沟道区和第二有源条的同时,刻蚀所述第一初始有源条、以及与所述第一初始有源条相接触的部分初始沟道结构,对应形成第一有源条和第三沟道区;

34、所述第三沟道区的尺寸沿朝向所述第一有源条的方向递减,且所述第三沟道区的主体材料的电子迁移率大于所述源极的主体材料的电子迁移率。

35、在一些实施例中,在所述第一初始有源条和所述第二初始有源条中分别形成所述漏极和所述源极,包括:

36、对所述第一初始有源条或者所述第一有源条沿所述第二方向远离所述沟道结构的一端进行第一重掺杂,形成所述源极;

37、对所述第二有源条沿所述第二方向远离所述沟道结构的一端进行所述第一重掺杂,形成所述漏极。

38、在一些实施例中,所述方法还包括:

39、对所述漏极进行热处理,以使得所述第一重掺杂过程中的掺杂离子扩散至所述第二有源条靠近所述沟道结构的一端,形成第一轻掺杂区;

40、其中,所述第一轻掺杂区的尺寸等于所述第二沟道区的最小尺寸;

41、对所述源极进行热处理,以使得所述第一重掺杂过程中的掺杂离子扩散至所述第一初始有源条或者所述第一有源条靠近所述沟道结构的一端,形成第二轻掺杂区;其中,所述第二轻掺杂区的尺寸等于所述第一沟道区的尺寸,或者,所述第二轻掺杂区的尺寸等于所述第三沟道区的最小尺寸。

42、在一些实施例中,在形成所述源极和所述漏极之前,所述方法还包括:

43、在所述第一沟道区和所述第二沟道区的表面形成栅极结构;或者,

44、在所述第一沟道区、所述第二沟道区和所述第三沟道区的表面形成所述栅极结构;所述栅极结构包括栅极介质层、以及位于所述栅极介质层表面的栅极导电层。

45、在一些实施例中,所述方法还包括:

46、在所述第一轻掺杂区的表面形成所述栅极结构。

47、在一些实施例中,所述初始沟道结构通过以下步骤形成:

48、在多个所述初始有源条之间的间隙中形成牺牲结构;

49、刻蚀所述牺牲结构和所述初始有源条,形成沿所述第一方向延伸的刻蚀凹槽;所述刻蚀凹槽将所述初始有源条分割为所述第一初始有源条和所述第二初始有源条;所述刻蚀凹槽暴露出所述第一初始有源条和所述第二初始有源条的侧壁;

50、在所述刻蚀凹槽暴露出的侧壁表面外延形成所述初始沟道结构。

51、在一些实施例中,在形成所述初始沟道结构之后,所述方法还包括:

52、对所述初始沟道结构进行第二重掺杂;其中,所述第一重掺杂与所述第二重掺杂的掺杂类型相同或者相反。

53、在一些实施例中,所述第一方向和所述第二方向为所述衬底所在平面内的任意两个方向,所述第三方向垂直于所述衬底所在的平面;所述方法还包括:

54、形成与所述源极相接的位线结构;

55、形成与所述栅极结构相接的字线结构;其中,所述位线结构沿所述第一方向和所述第三方向中的一个方向延伸,所述字线结构沿所述第一方向和所述第三方向中的另一个方向延伸;

56、形成与所述漏极相接、且沿所述第二方向延伸的电容结构。

57、本公开实施例提供的半导体结构及其形成方法,其中,半导体结构包括多个存储单元,每一存储单元至少包括沟道结构和漏极。由于存储单元的沟道结构包括两个大小不同的沟道区,且沟道结构的主体材料的电子迁移率大于漏极的主体材料的电子迁移率,因此,可以改善栅极诱导漏极漏电流,提高半导体结构的电性能。

- 还没有人留言评论。精彩留言会获得点赞!