一种晶体振荡器基座的制作方法

1.本方案属于石英振荡器领域,更具体地,涉及一种晶体振荡器基座。

背景技术:

2.最新一代蜂窝移动通信技术5g将逐渐渗透进我们的生产生活当中,作为新型的通信技术,5g技术对中高频器件也提出更高的要求。由于晶片极薄,传统尺寸晶片在生产加工过程中极易出现破碎的情况,对承载晶体基座的工艺、温度、设备都有很高的要求,且现有高频产品存在抗干扰性弱,布线不合理,加工难度大等问题,容易导致封装后漏气、起泡现象。

技术实现要素:

3.鉴于此,本方案旨在克服现有技术中的至少一种不足,提供一种晶体振荡器基座,在基座上直接开设置用于贴装石英晶体和ic的腔体,使基座结构简化并且小型化,适合安装小型化的石英晶体。

4.为了解决上述技术问题,采取下述技术方案:提供一种晶体振荡器的基座,所述基座由四层基板层压烧结而成,四层基板由下至上分别为底板、ic芯片贴装层、ic芯片连接层、晶体搭载平台层、所述底板包括上表面和下表面,所述底板的下表面设置有外电极;

5.所述ic芯片贴装层上设置有ic芯片贴装部,在ic芯片连接层上连接ic贴装部的位置开设第一镂空部,所述第一镂空部的周围设置有多个ic引脚内电极;

6.在所述晶体搭载平台层上开设第二镂空部,所述晶体搭载平台层还设置个石英晶体引脚内电极;

7.所述底板、ic芯片贴装层、ic芯片连接层、晶体搭载平台层之间电导通。

8.进一步地,所述基座的侧壁上开设有多个导电槽,所述导电槽分别穿过底板、ic芯片贴装层、ic芯片连接层、晶体搭载平台层,其中ic芯片贴装层、ic芯片连接层、晶体搭载平台层分别设置多个接触孔,所述底板、ic搭载平台层、晶体搭载平台层之间通过导电槽和/或接触孔实现电导通。

9.优选地,所述基座的侧壁上开设有十个导电槽,其中,基座的四角边设置四个导电槽,基座的一对较长对应的一对侧壁上,分别设置两个导电槽。

10.所述底板的上表面设置多个导电线路,导电线路与导电槽连接。

11.所述ic芯片贴装层的中间部位设有ic贴装部,在ic贴装部的四周设有多个ic引脚内电极,ic芯片贴装层还设置有多条用于内外电极导通的导电通路以及多个接触孔,ic芯片贴装层上的导电通路通过接触孔与底板上的导电线路导通,ic芯片贴装层与底板之间通过接触孔和导电槽实现电导通。

12.进一步地,所述底板的下表面的四边角上分布有四个外电极,与导电槽相连。

13.进一步地,所述第二镂空贯穿晶体搭载平台层的上表面和下表面,并且第二镂空部的尺寸大于第一镂空部的尺寸,以便暴露位于ic芯片贴装层上的ic贴装部,第一镂空部

与ic芯片贴装层构成安装ic芯片的空腔。

14.进一步地,所述晶体搭载平台层的四个边角处还设置四个石英晶体引脚内电极,石英晶体引脚内电极分别通过相应的接触孔与ic芯片连接层相连。

15.11.所述基座的镀层材质有金和镍两种,所述镀层金的厚度最小0.3μm,镍厚度为1.27~8.89um,基座整体翘曲度不大于0.05mm。

16.本方案与现有技术相比较有如下有益效果:在基座上直接开设置用于贴装石英晶体和ic的腔体,使基座结构简化并且小型化,适合安装小型化的石英晶体,从而通过利用小尺寸晶体实现高频率的晶体振荡器,防止起泡现象的产生,且本发明提供的晶体振荡器基座结构简单、布线合理、加工方便,具有一定的抗干扰性和防静电性。

附图说明

17.附图仅用于示例性说明,不能理解为对本方案的限制;为了更好说明本方案,附图某些部件会有省略、放大或缩小,并不代表实际产品的尺寸;对于本领域技术人员来说,附图中某些公知结构及其说明可能省略是可以理解的;附图中描述位置关系的用于仅用于示例性说明,不能理解为对本方案的限制。

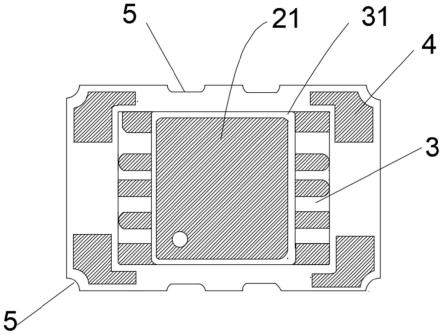

18.图1为本发明的一种晶体振荡器基座的结构正面示意图。

19.图2为本发明的一种晶体振荡器基座的结构侧面示意图。

20.图3为本发明一种晶体振荡器基座的底板上表面的结构示意图。

21.图4为本发明一种晶体振荡器基座的底板的下表面的结构示意图。

22.图5为本发明一种晶体振荡器的基座的ic芯片贴装层的结构示意图。

23.图6为本发明一种晶体振荡器的基座的ic芯片连接层的结构示意图。

24.图7为本发明一种晶体振荡器的基座的晶体搭载层的结构示意图。

具体实施方式

25.为了让本领域的技术人员更好地理解本方案的技术方案,下面结合具体实施例对本方案做进一步详细说明。实施例中所使用的工艺方法如无特殊说明,均为常规方法;所用的材料,如无特殊说明,均可从商业途径得到。

26.实施例1

27.本发明的较佳的实施例中,基于现有技术中存在的上述问题,现提供一种晶体振荡器基座,所述基座为采用四层布线熟瓷图方案的陶瓷基座,其每层厚度均有严格的控制。所述基座的镀层材质有金和镍两种,且镀层厚度有明确要求,其中,金的厚度最小为0.3μm,镍厚度为1.27~8.89um,基座整体翘曲度不大于0.05mm。

28.实施例1

29.如图1-图7所示,本发明提供的一种晶体振荡器的基座,所述基座由四层基板层压烧结而成,四层基板由下至上分别为底板1、ic芯片贴装层2、ic芯片连接层3、晶体搭载平台层4。

30.所述基座的侧壁上开设有十个导电槽5,其中,基座的四角边设置四个导电槽,基座的一对较长边对应的侧壁上,分别设置两个导电槽,每个导电槽分别穿过ic芯片贴装层2、ic芯片连接层3、晶体搭载平台层4,其中ic芯片贴装层2、ic芯片连接层3、晶体搭载平台

层4分别设置多个接触孔,底板1、ic芯片贴装层2、ic芯片连接层3、晶体搭载平台层4之间通过导电槽和/或接触孔实现电导通。

31.在本实施例中,如图3所示,底板1的下表面设置四个外电极11,分布在底板1下表面的四个边角处,与四个边角处的四个导电槽导通,如图4所示,底板的上表面设置包括六个导电线路12和多个接触孔13,其中五个导电线路12与导电槽5连接。

32.在本实施例中,如图5所示,ic芯片贴装层2的中间部位设有ic贴装部21,在ic贴装部21的四周设有三个ic引脚内电极22,ic芯片贴装层2还设置有多条用于内外电极导通的导电线路23以及多个接触孔24,ic芯片贴装层2上的导电线路23通过接触孔24与底板1上的部分接触孔24重叠,实现与底板1上的导电线路12导通。

33.在本实施例中,如图6所示,ic芯片连接层3,在ic芯片连接层上连接ic贴装部21的部位开设第一镂空部31,镂空部31贯穿ic芯片连接层3的上表面和下表面,从而暴露位于ic芯片贴装层2上的ic贴装部21,第一镂空部31与ic芯片贴装层2构成安装集成ic的空腔,第一镂空部31的周围设置有十个ic引脚内电极32,ic芯片连接层3还设置多条用于内外电极导通的导电线路33以及多个接触孔34,导电线路33连接导电槽或接触孔34与ic芯片贴装层2上的导电线路23接通。

34.在本实施例中,如图7所示,在所述晶体搭载平台层4上开设第二镂空部41,所述第二镂空部41贯穿晶片搭载平台层4的上表面和下表面,并且第二镂空部41的尺寸大于第一镂空部31的尺寸,从而暴露位于ic芯片连接层3的ic引脚内电极32和ic贴装部21,晶体搭载平台层4,所述晶体搭载平台层4的四个边角处还设置四个石英晶体引脚内电极42,石英晶体引脚内电极42通过ic芯片连接层3上的相应的接触孔34与ic芯片连接层3相连。

35.显然,本方案的上述实施例仅仅是为清楚地说明本方案所作的举例,而并非是对本方案的实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。凡在本方案的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本方案权利要求的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1