一种带同步功能DDS电路的制作方法

一种带同步功能dds电路

技术领域

1.本发明涉及集成电路技术领域,特别涉及一种带同步功能dds电路。

背景技术:

2.dds(direct digital synthesizer,直接式数字频率合成器)是一种采用全数字化方式合成的信号发生器电路,可通过内置的数模转换电路生成灵活调制的正弦模拟波形,具有快速配置、精密调频和高精度调制等特点,在雷达、测试及通讯等领域广泛应用。该类器件在多通道应用时由于外围电路、上电配置和时钟端的影响,实际使用时很难保证输出信号的相位一致,传统方法会配置外围时钟电路并进行同步上电配置,或对输出信号进行移相处理,硬件消耗较大且配置复杂。

技术实现要素:

3.本发明的目的在于提供一种带同步功能dds电路,以解决目前多片dds电路使用时初始相位不一致的问题。

4.为解决上述技术问题,本发明提供了一种带同步功能dds电路,包括:

5.相位累加器,接收输入的config信号,生成连续相位信号phase(1)~phase(m);

6.相幅转换器,将连续相位信号转换为连续幅度信号amp(1)~amp(m);

7.数据合成器,将连续幅度信号转换为交织数字正弦信号data(1)~data(n);

8.模拟接收及合成器,接收交织数字正弦信号,并合成为模拟差分信号adata(p)和adata(q);

9.数模转换器,将模拟差分信号转换为模拟正弦输出;

10.同步接收电路,接收外部同步输入信号sync_in并产生内部同步时钟f

clk/

2;

11.同步发送电路,将内部同步时钟f

clk/

2转换为外部输出的同步输出信号sync_out;

12.时钟分频及控制器,将内部同步时钟f

clk

/2处理为已同步的模块时钟f

clk

/m、f

clk

/m、f

clk

/n、f

clk/

2、f

clk

,并分别提供给相位累加器、相幅转换器、数据合成器、模拟接收及合成器和数模转换器。

13.在一种实施方式中,所述同步接收电路包括延时电路、缓冲器二、缓冲器四、缓冲器六、缓冲器八、缓冲器十、缓冲器十三、d触发器三、d触发器五、d触发器七、d触发器九、d触发器十一、d触发器十五、与非门十二和与非门十四;

14.所述延时电路的输入端连接外部同步输入信号sync_in和延时参数input_delay《n:0》,输出端通过缓冲器二连接d触发器三的d端;d触发器三的q端通过缓冲器四连接d触发器五的d端,d触发器五的q端通过缓冲器六连接d触发器七的d端,d触发器七的q端通过缓冲器八连接d触发器九的d端;

15.d触发器九的q端同时连接缓冲器十的输入端和d触发器十一的d端,接缓冲器十的输出端和d触发器十一的q端同时连接与非门十二的输入端;与非门十二的输出端通过缓冲器十三连接与非门十四的一个输入端,与非门十四的输出端连接d触发器十五的d端,d触发

器十五的q端连接与非门十四的另一个输入端;

16.所述d触发器三、d触发器五、d触发器七、d触发器九、d触发器十一、d触发器十五的时钟信号端均连接系统时钟f

clk

。

17.在一种实施方式中,所述同步发送电路包括d触发器二十一、d触发器二十三、d触发器二十五、d触发器二十七、d触发器三十、反向器二十、反向器二十二、反向器二十四、反向器二十六、反向器二十八和与门二十九;

18.所述d触发器二十一的时钟输入端连接f

clk

/2,d端连接反向器二十的输出端,q端连接反向器二十的输入端;

19.所述d触发器二十三的时钟输入端连接d触发器二十一的q端,d端连接反向器二十二的输出端,q端连接反向器二十二的输入端;

20.所述d触发器二十五的时钟输入端连接d触发器二十三的q端,d端连接反向器二十四的输出端,q端连接反向器二十四的输入端;

21.所述d触发器二十七的时钟输入端同时连接d触发器二十五的q端和反向器二十八的输入端,d端连接反向器二十六的输出端,q端连接反向器二十六的输入端;

22.所述与门二十九的输入端分别连接d触发器二十七的q端和反向器二十八的输出端,输出端连接d触发器三十的d端;d触发器三十的时钟输入端连接内部同步时钟f

clk

/2,q端连接同步输出信号sync_out。

23.在一种实施方式中,所述config信号用于配置dds电路的相位、频率、幅度参数。

24.在一种实施方式中,所述连续相位信号phase(1)~phase(m)的位数m由实际需求决定,取4、8、16...,对应的,其时钟为f

clk

/m。

25.在一种实施方式中,所述连续幅度信号amp(1)~amp(m)的位数m与所述连续相位信号一致,对应的,其时钟为f

clk

/m。

26.在一种实施方式中,所述交织数字正弦信号data(1)~data(n)由实际需求决定,取2或4,对应的,其时钟为f

clk

/n。

27.在一种实施方式中,所述时钟分频及控制器输入有同步使能信号sync_en,用于开启电路同步功能。

28.在一种实施方式中,所述同步输出信号sync_out的频率为f

clk

/16,占空比为25%。

29.本发明提供的一种带同步功能dds电路,实现多个dds电路同时使用的场景下输出信号相位一致。本发明通过输入的同步信号进行边缘检测并实现内核时钟的同步,从而生成初始相位一致的数字正弦波形,实现多个dds电路的输出同步。本发明提出的dds电路包括同步接收电路、同步发送电路、时钟分频及控制器、相位累加器、相幅转换器、数据合成器和数模转换器,在外部输入同步信号后,数字内核会自动与同步输入信号上升沿同步。本发明可解决多片dds电路使用时初始相位不一致的问题,无需外部配置时钟或同步机制电路,简化了dds应用时的电路配置及使用难度,可广泛应用于dds或相关高速数模转换器电路中。

附图说明

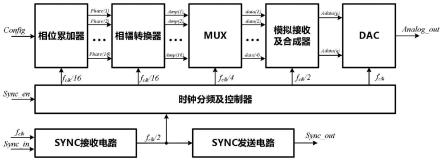

30.图1是本发明提供的一种带同步功能dds电路结构示意图;

31.图2是本发明中同步接收电路的结构示意图;

32.图3是本发明中同步接收电路的信号时序图;

33.图4是本发明中同步发送电路的结构示意图;

34.图5是本发明中同步发送电路的信号时序图。

具体实施方式

35.以下结合附图和具体实施例对本发明提出的一种带同步功能dds电路作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

36.图1是本发明提供的一种带同步功能dds电路,电路为典型的直接数字频率合成器架构,不同的是,加入了同步机制,同步功能模块由同步信号(sync)接收和同步信号(sync)发送组成。

37.请继续参阅图1,所述带同步功能dds电路由相位累加器、相幅转换器、mux(即数据合成器)、模拟接收及合成器、dac(即数模转换器)、时钟分频及控制器、同步接收电路和同步发送电路组成。所述相位累加器接收输入的config信号,生成连续相位信号phase(1)~phase(m);所述相幅转换器将连续相位信号转换为连续幅度信号amp(1)~amp(m);所述数据合成器将连续幅度信号转换为交织数字正弦信号data(1)~data(n);所述模拟接收及合成器接收交织数字正弦信号,并合成为模拟差分信号adata(p)和adata(q);所述数模转换器将模拟差分信号转换为模拟正弦输出;所述同步接收电路接收外部同步输入信号sync_in并产生内部同步时钟f

clk/

2;所述同步发送电路将内部同步时钟f

clk/

2转换为外部输出的同步输出信号sync_out;所述时钟分频及控制器将内部同步时钟f

clk

/2处理为已同步的模块时钟f

clk

/m、f

clk

/m、f

clk

/n、f

clk/

2、f

clk

,并分别提供给相位累加器、相幅转换器、数据合成器、模拟接收及合成器和数模转换器。

38.其中,所述config信号用于配置dds电路的相位、频率、幅度等参数。所述连续相位信号phase(1)~phase(m)的位数m由实际需求决定,取4、8、16...,对应的,其时钟为f

clk

/m;所述连续幅度信号amp(1)~amp(m)的位数m与所述连续相位信号一致,对应的,其时钟为f

clk

/m。所述交织数字正弦信号data(1)~data(n)由实际需求决定,一般取2或4,或者也有不交织的单通路;对应的,其时钟为f

clk

/n。所述时钟分频及控制器输入有同步使能信号sync_en,用于开启电路同步功能。

39.本发明实施例中相位累加器和相幅转换器均为16位结构,即m=16;由mux转换为4位交织数字正弦信号data(1:4),即n=4。sync接收电路(即同步接收电路)抓取外部的同步输入信号sync_in的上升沿,并生成同相位的二分频时钟f

clk

/2。sync发送电路(同步发送电路)将内部的二分频时钟f

clk

/2处理为同相位的占空比为25%的16分频信号sync_out,并提供给外部需同步的从设备,作为其同步信号输入。

40.图2是本发明的同步接收电路的结构示意图,包括延时电路1、缓冲器二2、缓冲器四4、缓冲器六6、缓冲器八8、缓冲器十10、缓冲器十三13、d触发器三3、d触发器五5、d触发器七7、d触发器九9、d触发器十一11、d触发器十五15、与非门十二12和与非门十四14。所述延时电路的输入端连接外部同步输入信号sync_in和延时参数input_delay《n:0》,输出端通过缓冲器二连接d触发器三的d端;d触发器三的q端通过缓冲器四连接d触发器五的d端,d触发器五的q端通过缓冲器六连接d触发器七的d端,d触发器七的q端通过缓冲器八连接d触发

器九的d端;d触发器九的q端同时连接缓冲器十的输入端和d触发器十一的d端,接缓冲器十的输出端和d触发器十一的q端同时连接与非门十二的输入端;与非门十二的输出端通过缓冲器十三连接与非门十四的一个输入端,与非门十四的输出端连接d触发器十五的d端,d触发器十五的q端连接与非门十四的另一个输入端;所述d触发器三、d触发器五、d触发器七、d触发器九、d触发器十一、d触发器十五的时钟信号端均连接系统时钟f

clk

。

41.其中,所述延时电路用来微调同步时钟的相位,可由n+1的t值调节;同步输入信号sync_in经四个时钟延迟采样后,通过与非门十二生成一个系统时钟(sysclk)脉宽的同步脉冲,最后通过与非门十四和d触发器十五组成的二分频电路生成一个已同步的二分频时钟f

clk

/2。

42.图3是同步接收电路的工作时序,由于主设备和从设备的系统时钟sysclk是相同时钟,所以同步信号sync_in与系统时钟sysclk是相干时钟,经同步接收电路处理后可生成与同步信号sync_in相位差为4个系统时钟的二分频时钟f

clk

/2。

43.图4是本发明中同步发送电路的结构示意图,包括d触发器二十一21、d触发器二十三23、d触发器二十五25、d触发器二十七27、d触发器三十30、反向器二十20、反向器二十二22、反向器二十四24、反向器二十六26、反向器二十八28和与门二十九29。所述d触发器二十一的时钟输入端连接f

clk

/2,d端连接反向器二十的输出端,q端连接反向器二十的输入端;所述d触发器二十三的时钟输入端连接d触发器二十一的q端,d端连接反向器二十二的输出端,q端连接反向器二十二的输入端;所述d触发器二十五的时钟输入端连接d触发器二十三的q端,d端连接反向器二十四的输出端,q端连接反向器二十四的输入端;所述d触发器二十七的时钟输入端同时连接d触发器二十五的q端和反向器二十八的输入端,d端连接反向器二十六的输出端,q端连接反向器二十六的输入端;所述与门二十九的输入端分别连接d触发器二十七的q端和反向器二十八的输出端,输出端连接d触发器三十的d端;d触发器三十的时钟输入端连接内部同步时钟f

clk

/2,q端连接同步输出信号sync_out。

44.在所述同步发送电路中,同步后的二分频时钟f

clk

/2经四次二分频后,生成同步后的16分频时钟f

clk

/16;通过反向器二十八和与门二十九进行占空比调整,生成25%占空比的16分频时钟信号’f

clk

/16,最终经d触发器三十生成与二分频时钟f

clk

/2对齐的同步信号输出,具体信号时序图见图5。

45.特别指出的是,时钟分频及控制器不在本发明的描述中,在同步使能时,所述时钟分频及控制器将生成与输入的二分频时钟f

clk

/2延迟固定的各分频时钟,包括f

clk

/16、f

clk

/4和f

clk

/2,f

clk

无特别要求,设计中可选择dll方式自动对齐。

46.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1