一种并行IIR通用滤波器的实现方法及装置与流程

本发明属于滤波器领域,具体涉及一种并行iir通用滤波器的实现方法及装置。

背景技术:

1、iir(infinite impulse response)滤波器是无限冲击响应滤波器,又称为递归型滤波器,具有非线性相频响应、单位冲激响应无限长、阶数要求低、有反馈环路、幅频特性精度高等特点,同fir相比在相同阶数时取得更好的滤波效果。因此,iir滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

2、iir滤波器有软件实现和硬件实现两种方案,iir滤波器算法与输入的待处理数据的前后数据都有关联,且每个输入数据的累乘加次数与向量数据的阶数直接相关。软件实现的时候受限于软件实现方式及cpu乘累加资源的限制,一般是一个数据接着一个数据的进行处理,即处理完一个数据的乘累加得到结果后,再处理下一个数据,对cpu的资源和总线的占用情况较多,处理速度较慢。硬件实现的时候,如果直接完全按通用iir计算公式实现,要获得较快的处理效果,就需要较多的乘累加单元同步处理,需要的硬件资源较多;如果节省资源就需要牺牲处理时间。有的设计为了节省资源和获得较快的处理速度,对iir的公式进行了简化,但是这种方式对输入数据和向量数据有特殊要求,会牺牲部分iir的性能。

3、基于上述分析,如何在不增加乘累加单元的前提下,获得较快的处理速度本领域技术人员急需解决的技术问题。

技术实现思路

1、基于现有技术存在的问题,本发明提出了一种新的实现方案一种并行iir通用滤波器的实现方法及装置。利用并行方式同时处理多组数据,提高处理效率;使用的乒乓buf及循环取数、共用乘法器资源等方式,节约了数据处理、存储的资源消耗。对待处理数据及向量数据的取值和长度没有特殊要求,实现了通用性。

2、在本发明的第一方面,本发明提出了一种并行iir通用滤波器的实现方法,所述方法包括:

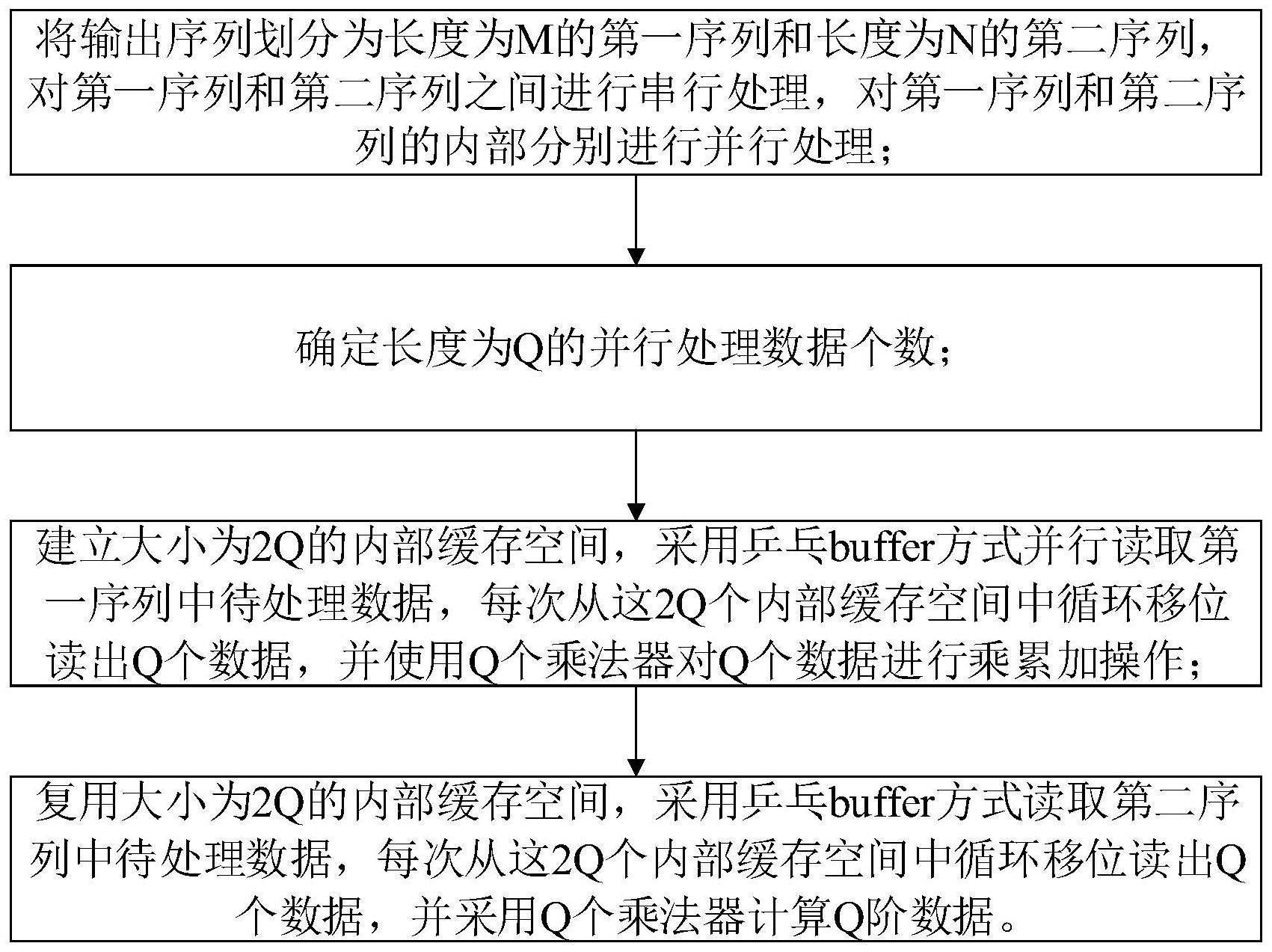

3、将输出序列划分为长度为m的第一序列和长度为n的第二序列,对第一序列和第二序列之间进行串行处理,对第一序列和第二序列的内部分别进行并行处理;

4、确定长度为q的并行处理数据个数;

5、建立大小为2q的内部缓存空间,采用乒乓buffer方式并行读取第一序列中待处理数据,每次从这2q个内部缓存空间中循环移位读出q个数据,并使用q个乘法器对q个数据进行乘累加操作;

6、复用大小为2q的内部缓存空间,采用乒乓buffer方式读取第二序列中待处理数据,每次从这2q个内部缓存空间中循环移位读出q个数据,并采用q个乘法器计算q阶数据。

7、在本发明的第二方面,本发明还提供了一种并行iir通用滤波器的实现装置,所述实现装置包括配置寄存器、ahb总线控制模块、amem存储器、bmem存储器、xmem存储器、ymem存储器、乒乓buffer控制模块以及乘累加模块;所述配置寄存器连接有ahb总线控制模块和乒乓buffer控制模块,所述ahb总线控制模块连接有amem存储器、bmem存储器、xmem存储器以及乘累加模块;所述amem存储器、bmem存储器、xmem存储器以及ymem存储器连接有乒乓buffer控制模块;所述乒乓buffer模块连接有乘累加模块。

8、本发明的有益效果:

9、本发明将滤波器的输出序列分为两部分进行处理,每个部分同时并行处理多个数据,能够提升处理速度和效率;同时,本发明的两个部分之间是串行处理数据的,只需要占用较少的硬件资源;本发明的并行处理数据个数可以根据本领域技术人员按照实际情况进行选择,对待处理数据及向量数据的取值和长度没有特殊要求,因此本发明具有通用性。

技术特征:

1.一种并行iir通用滤波器的实现方法,其特征在于,所述方法包括:

2.根据权利要求1所述的一种并行iir通用滤波器的实现方法,其特征在于,输出序列划分的公式表示为:

3.根据权利要求1所述的一种并行iir通用滤波器的实现方法,其特征在于,采用乒乓buffer方式并行处理数据的过程包括:

4.一种并行iir通用滤波器的实现装置,其特征在于,所述实现装置包括配置寄存器、ahb总线控制模块、amem存储器、bmem存储器、xmem存储器、ymem存储器、乒乓buffer控制模块以及乘累加模块;所述配置寄存器连接有ahb总线控制模块和乒乓buffer控制模块,所述ahb总线控制模块连接有amem存储器、bmem存储器、xmem存储器以及乘累加模块;所述amem存储器、bmem存储器、xmem存储器以及ymem存储器连接有乒乓buffer控制模块;所述乒乓buffer模块连接有乘累加模块。

5.根据权利要求4所述的一种并行iir通用滤波器的实现装置,其特征在于,所述amem存储器、bmem存储器、xmem存储器、ymem存储器均为可读可写存储器。

6.根据权利要求4所述的一种并行iir通用滤波器的实现装置,其特征在于,所述amem存储器、bmem存储器、xmem存储器以及ymem存储器连接有乒乓buffer控制模块包括所述amem存储器和所述bmem存储器连接有第一数据选择器,所述xmem存储器和所述ymem存储器连接有第二数据选择器;所述乒乓buffer控制模块分别与所述第一数据选择器和所述第二数据选择器双向连接;所述乒乓buffer控制模块通过存储器读总线连接所述ymem存储器。

7.根据权利要求4所述的一种并行iir通用滤波器的实现装置,其特征在于,所述乒乓buffer控制模块连接有第一数据选择器和第二数据选择器,并从其中读入q个数据,对输入数据进行移位取数后,送出q个乘数a和q个乘数b,和乘法使能信号。

8.根据权利要求4所述的一种并行iir通用滤波器的实现装置,其特征在于,所述乘累加模块包括q个乘法器和q个累加器,每个乘法器分别连接一个乘数a一个乘数b,q个乘法器输出的积分别送到q个累加器进行累加。

9.根据权利要求4所述的一种并行iir通用滤波器的实现装置,其特征在于,所述乘累加模块还包括q个乘法器和q个累加器,q个乘法器分别连接一个乘数a一个乘数b,q个乘法器输出的积一起送到一个累加器进行累加。

10.根据权利要求8或9所述的一种并行iir通用滤波器的实现装置,其特征在于,所述累加器后连接有ahb总线控制模块输出。

技术总结

本发明属于滤波器领域,具体涉及一种并行IIR通用滤波器的实现方法及装置;所述方法包括将输出序列划分为第一序列和第二序列;建立大小为2Q的内部缓存空间,采用乒乓buffer方式并行读取第一序列中待处理数据,每次循环移位读出Q个数据,并使用Q个乘法器对Q个数据进行乘累加操作;复用2Q的内部缓存空间,采用乒乓buffer方式读取第二序列中待处理数据循环移位取数,每次循环移位读出Q个数据,并采用Q个乘法器计算Q阶数据。本发明将滤波器的输出序列分为两部分进行处理,每个部分同时并行处理多个数据,能够提升处理速度和效率;同时,本发明具有硬件资源占用小、处理速度快、通用性等特点。

技术研发人员:请求不公布姓名

受保护的技术使用者:思澈科技(重庆)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!