基于正反馈的电流型并串转换电路

1.本发明涉及集成电路设计领域,具体涉及一种适用于超大阵列图像传感器的并串转换电路。

背景技术:

2.互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)图像传感器主要结构包括像素阵列、读出电路、行驱动电路以及时序控制等外围电路。对于cmos图像传感器来说,分辨率是一个非常重要的指标,分辨率越高,越能清晰分辨图像中的细节。一般来说,分辨率取决于图像传感器像素数目,像素阵列越大,分辨率便越高。而伴随着像素阵列的扩大,读出电路阵列也增大,一系列非理想效应愈加明显,比如寄生电阻、寄生电容等,导致图像传感器设计的难度和复杂度也随之增加。

3.一般的,模拟信号经过读出电路处理后,仍需通过并串转换电路,将并行数据转换为串行数据,而大多数的并串转换电路是基于电压传输的。然而,对于超大阵列图像传感器而言,超大的读出阵列将引入大的寄生电阻和寄生电容,而这些寄生效应使得电压型的读出信号在传输过程中产生一定程度的衰减。因此,电流型并串转换电路便被提出了,该电路的工作过程分为两步,读出信号通过由图2、图3和图4共同组成的电流型感知放大器(sensor amplifier,sa)完成第一步并串转换,再通过如图6所示的三态门模块和如图7所示的移位寄存器完成第二步并串转换。第一步并串转换将输入信号转换为逻辑电平,从而有效抑制读出信号在传输过程中的衰减,但该工作过程涉及电容的充放电,如图2所示电容c1与c2以及如图4所示电容c3与c4为电流型sa电路中主要寄生电容,大阵列的读出电路使得这些电容变得足够相当大,从而影响了充放电的速度,导致读出信号在快速读出时产生误码,故提出了基于正反馈的电流型并串转换电路,利用该电路解决误码问题。

技术实现要素:

4.为克服现有技术的不足,本发明旨在提出基于正反馈的电流型并串转换电路设计方法,该电路适用于超大阵列图像传感器,用于解决读出信号在传输过程中发生衰减的问题以及因寄生电容过大导致读出信号误码的问题,以提高图像传感器的性能。为此,本发明采取的技术方案是,基于正反馈的电流型并串转换电路,包括电流型sa电路、三态门模块和移位寄存器,其中电流型sa电路分为两部分,即列并行局部电路和全局电路,分别记为local模块和global模块;图像传感器全阵列像素共有s列,每列模数转换器adc(analog-to-digital converter)的精度为n位,1个local模块对应1位输出数据,则每列电路包含n个并行的local模块,另将全阵列划分为若干组,记作若干block,每个block包含m列读出电路,则共有s/m个block,而每个block包含n个并行global模块,那么并串转换电路的组成为s*n个local模块、s*n/m个global模块、1个三态门模块和1个移位寄存器;其工作过程分为两步:第一步由电流型sa电路完成,将s列并行数据转换为s/m组并行数据;第二步由三态门模块和移位寄存器完成,将s/m组并行数据转换为s/m组串行数据。

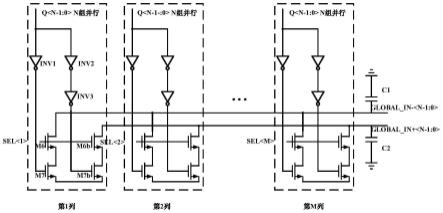

5.每组local模块包括反相器inv1、inv2和inv3,nmos管m6、m6b、m7和m7b,以及输出端寄生电容c1和c2;每列adc输出n位数据q《0》、q《1》、q《2》、q《3》、

···

、q《n-2》、q《n-1》,分别由n组local模块一一对应接收,则一个block包含m*n个local模块;

6.local模块接收数据q《0》时,q《0》有两条流通路径可选,一条是通过所述反相器inv1连接到m7的栅极,另一条是依次通过所述反相器inv2和inv3连接到m7b的栅极,所述nmos管m7与m7b源极接地,m7与m7b漏极分别连接所述nmos管m6与m6b的源极,sel《1》信号连接到m6与m6b的栅极,m6与m6b的漏极作为输出端,输出信号分别为global_in-《0》和global_in+《0》。

7.每组global模块包括复位电路和正反馈输出电路,其中复位电路包括pmos管m1和m1b,nmos管m2、m2b和m3;正反馈输出电路包括pmos管m4、m4b、m8、m8b、m9和m9b,nmos管m5、m5b、m10和m10b,传输门tg,反相器inv4和inv5,与非门nand1和nand2,以及寄生电容c3和c4。

8.local模块接收数据q《0》时,其输出信号global_in+《0》与global_in-《0》分别连接到所述nmos管m5与m5b的源极,m5与m5b的漏极分别连接所述pmos管m4与m4b的漏极,m4与m4b的源极接电源电压vdd,m4与m5的栅极相连,并连接m4b的漏极,该漏极电压记为global_bus+《0》,m4b与m5b的栅极相连,并连接m4的漏极,该漏极电压记为global_bus-《0》,m4与m4b的栅极通过所述传输门tg相连,tg两个控制信号分别为rst与rstb,rstb信号由rst信号通过所述反相器inv4产生,当rst置为高电平时,tg导通,且复位电路开始工作。所述pmos管m9与所述nmos管m10栅极相连,并连接m4的漏极,m10源极接地,m10漏极连接m9漏极,并连接m6的漏极,m9源极连接所述pmos管m8漏极,m8栅极连接使能信号en,m8源极接vdd,所述pmos管m9b与所述nmos管m10b栅极相连,并连接m4b的漏极,m10b源极接地,m10b漏极连接m9b漏极,并连接m6b的漏极,m9b源极连接所述pmos管m8b漏极,m8b栅极连接en信号,m8b源极接vdd,由m8、m9和m10以及m8b、m9b、m10b组成正反馈结构,en信号控制正反馈结构是否工作,当tg断开后,en信号置为低电平,正反馈结构开始工作。global_bus+《0》与控制信号sc作为所述与非门nand1的输入端,nand1输出端连接所述反相器inv4的输入端,inv4输出信号为global_out+《0》,global_bus-《0》与控制信号sc作为所述与非门nand2的输入端,nand2输出端连接所述反相器inv5的输入端,inv5输出信号为global_out-《0》。同时,m6b的漏极与m6的漏极分别连接所述nmos管m3的源极和漏极,m3的源极和漏极分别连接所述nmos管m2的源极与所述nmos管m2b的源极,rst信号连接到m2、m2b和m3栅极,m2的漏极连接所述pmos管m1的漏极,m2b的漏极连接所述pmos管m1b的漏极,m1与m1b源极接vdd,m1与m1b栅极接参考信号vref,vref信号用以控制复位电压大小。以此类推,当local模块接收q《1》、q《2》、

···

、q《n-2》、q《n-1》时,分析方式相同,n位数据同步转换。在选通信号sel控制下,各列数据依次转换,完成第一步并串转换。

9.三态门模块电路结构,其结构由n个三态门、1个电阻和1个缓冲器组成。所述n个三态门输入端依次为global_out+《0》、global_out+《1》、global_out+《2》、global_out+《3》、

···

、global_out+《n-2》、global_out+《n-1》,使能信号依次为enable《0》、enable《1》、enable《2》、enable《3》、

···

、enable《n-2》、enable《n-1》;移位寄存器电路由n个带复位的d触发器首尾相连组成,时钟clk上升沿有效,依次产生n位有效使能,使得n位数据经过缓冲器按最低位至最高位串行输出,完成第二步并串转换。

10.本发明的特点及有益效果是:

11.本发明提出了一种基于正反馈的电流型并串转换电路,用于解决读出信号误码的问题,以提高图像传感器性能。采用两步式电流型并串转换电路,通过电流型sa完成第一步并串转换,将全阵列并行数据转换为若干列并行数据,一方面抑制了读出信号在传输过程中衰减问题,另一方面通过正反馈结构提高充放电的速度,保证了读出信号的准确度;再通过移位寄存器和三态门将若干列并行数据转换为串行数据,实现最终的并串转换。

附图说明:

12.图1展示的是超大阵列图像传感器系统架构。

13.图2展示的是电流型sa电路的local模块电路结构。

14.图3展示的是电流型sa电路的global模块中的复位电路结构。

15.图4展示的是电流型sa电路的global模块中的正反馈输出电路结构。

16.图5展示的是电流型sa电路的工作时序图。

17.图6展示的是三态门模块电路结构。

18.图7展示的是移位寄存器电路结构。

具体实施方式

19.一种基于正反馈的电流型并串转换电路,包括电流型sa电路、三态门模块和移位寄存器,其中电流型sa电路分为两部分,即列并行local模块和global模块。假设图像传感器全阵列像素共有s列,每列adc的精度为n位,1个local模块对应1位输出数据,则每列电路包含n个并行的local模块,另将全阵列划分为若干组,记作若干block,每个block包含m列读出电路,则共有s/m个block,而每个block包含n个并行global模块,那么并串转换电路的组成为s*n个local模块、s*n/m个global模块、1个三态门模块和1个移位寄存器。其工作过程分为两步:第一步由电流型sa电路完成,将s列并行数据转换为s/m组并行数据;第二步由三态门模块和移位寄存器完成,将s/m组并行数据转换为s/m组串行数据。

20.图2展示了电流型sa电路的local模块电路结构,每组local模块包括反相器inv1、inv2和inv3,nmos管m6、m6b、m7和m7b,以及输出端寄生电容c1和c2。每列adc输出n位数据q《0》、q《1》、q《2》、q《3》、

···

、q《n-2》、q《n-1》,分别由n组local模块一一对应接收,则一个block包含m*n个local模块。

21.以local模块接收数据q《0》为例,q《0》有两条流通路径可选,一条是通过所述反相器inv1连接到m7的栅极,另一条是依次通过所述反相器inv2和inv3连接到m7b的栅极,所述nmos管m7与m7b源极接地,m7与m7b漏极分别连接所述nmos管m6与m6b的源极,sel《1》信号连接到m6与m6b的栅极,m6与m6b的漏极作为输出端,分别为global_in-《0》和global_in+《0》。

22.图3展示了电流型sa电路的global模块中的复位电路结构,图4展示了电流型sa电路的global模块中的正反馈输出电路结构。每列adc的精度为n位,一个block的m列读出电路包含m*n组local模块和n组global模块,这样的设计一方面保证输出数据的一致性,另一方面减小版图面积,提高电路利用率。global模块分为复位电路和正反馈输出电路,其中复位电路包括pmos管m1和m1b,nmos管m2、m2b和m3;输出电路包括pmos管m4、m4b、m8、m8b、m9和m9b,nmos管m5、m5b、m10和m10b,传输门tg,反相器inv4和inv5,与非门nand1和nand2,以及

寄生电容c3和c4。

23.以local模块接收数据q《0》为例,其输出信号global_in+《0》与global_in-《0》分别连接到所述nmos管m5与m5b的源极,m5与m5b的漏极分别连接所述pmos管m4与m4b的漏极,m4与m4b的源极接电源电压vdd,m4与m5的栅极相连,并连接m4b的漏极,该漏极电压记为global_bus+《0》,m4b与m5b的栅极相连,并连接m4的漏极,该漏极电压记为global_bus-《0》,m4与m4b的栅极通过所述传输门tg相连,tg两个控制信号分别为rst与rstb,rstb信号由rst信号通过所述反相器inv4产生,当rst置为高电平时,tg导通,且复位电路开始工作。所述pmos管m9与所述nmos管m10栅极相连,并连接m4的漏极,m10源极接地,m10漏极连接m9漏极,并连接m6的漏极,m9源极连接所述pmos管m8漏极,m8栅极连接使能信号en,m8源极接vdd,所述pmos管m9b与所述nmos管m10b栅极相连,并连接m4b的漏极,m10b源极接地,m10b漏极连接m9b漏极,并连接m6b的漏极,m9b源极连接所述pmos管m8b漏极,m8b栅极连接en信号,m8b源极接vdd,由m8、m9和m10以及m8b、m9b、m10b组成正反馈结构,en信号控制正反馈结构是否工作,当tg断开后,en信号置为低电平,正反馈结构开始工作。global_bus+《0》与sc信号作为所述与非门nand1的输入端,nand1输出端连接所述反相器inv4的输入端,inv4输出信号为global_out+《0》,global_bus-《0》与sc信号作为所述与非门nand2的输入端,nand2输出端连接所述反相器inv5的输入端,inv5输出信号为global_out-《0》。同时,m6b的漏极与m6的漏极分别连接所述nmos管m3的源极和漏极,m3的源极和漏极分别连接所述nmos管m2的源极与所述nmos管m2b的源极,rst信号连接到m2、m2b和m3栅极,m2的漏极连接所述pmos管m1的漏极,m2b的漏极连接所述pmos管m1b的漏极,m1与m1b源极接vdd,m1与m1b栅极接参考信号vref,vref信号用以控制复位电压大小。以此类推,当local模块接收q《1》、q《2》、

···

、q《n-2》、q《n-1》时,分析方式相同,n位数据同步转换。在选通信号sel控制下,各列数据依次转换,完成第一步并串转换。

24.图6展示了三态门模块电路结构,其结构由n个三态门、1个电阻和1个缓冲器组成。所述n个三态门输入端依次为global_out+《0》、global_out+《1》、global_out+《2》、global_out+《3》、

···

、global_out+《n-2》、global_out+《n-1》,使能信号依次为enable《0》、enable《1》、enable《2》、enable《3》、

···

、enable《n-2》、enable《n-1》。图7展示了移位寄存器电路结构,其结构由n个带复位的d触发器首尾相连组成,时钟clk上升沿有效,依次产生n位有效使能,使得n位数据经过缓冲器按最低位至最高位串行输出,完成第二步并串转换。

25.本发明为电流型并串转换电路,下面对工作过程展开详细介绍。

26.图5显示了电流型sa电路的工作时序,sel信号依次置为高电平,不同列依次开始工作。以local模块接收数据q《0》为例,sel《1》信号置为高电平,m6与m6b导通,假设q《0》为低电平,则m7导通,m7b截止,那么m6与m7形成对地导电通路。

27.t0~t1时刻,global模块中的复位电路开始工作,rst信号置为高电平,则m2、m2b和m3导通,对节点global_in+《0》与global_in-《0》进行复位操作。vref信号为某一固定电压值,控制节点global_in+《0》与global_in-《0》初始复位电压的大小。同时,输出电路中的传输门tg导通,m4、m4b、m5和m5b栅极相连,处在同一电压,并且其电压大小与节点global_in+《0》和global_in-《0》初始复位电压大小相关。

28.t1~t2时刻,rst信号置为低电平,en信号置为低电平,则传输门tg断开,m4、m4b、

m5和m5b形成交叉耦合结构,由m8、m9和m10以及m8b、m9b、m10b组成的正反馈结构开始工作。在传输门tg断开瞬间,节点global_bus+《0》与global_bus-《0》的电压会在tg电流与m6、m6b充电电流作用下稍微上升。此时,节点global_bus+《0》与global_bus-《0》均处于高电平状态,使得m10与m10b导通,形成对地通路。又因为q《0》为低电平,local模块中的m6与m7形成对地导电通路,那么对于节点global_bus+《0》来说,其放电速度将快于节点global_bus-《0》,当节点global_bus+《0》电压低于vdd的一半时,m10b截止,m8b与m9b将节点global_in+《0》上拉为高电平,那么节点global_bus-《0》的充电速度将加快,并且在交叉耦合结构作用下一直呈现为高电平状态,因此,节点global_in-《0》一直被下拉为低电平,反作用于节点global_bus+《0》的放电过程,从而形成正反馈,直至节点global_bus+《0》放电至0,而节点global_bus-《0》充电至vdd。

29.t2~t3时刻,en信号置为高电平,正反馈结构停止工作,此时sc信号作为输出控制信号,被置为高电平,在与非门和反相器的逻辑关系下,使得最终输出global_out+《0》为0,global_out-《0》为vdd。

30.global模块电路结构完全对称,若q《0》为高电平,分析方式依旧适用。以此类推,当local模块接收q《1》、q《2》、

···

、q《n-2》、q《n-1》时,分析方式相同,n位数据同步转换。在sel、rst、en和sc信号控制下,各列数据依次转换,完成第一步并串转换。

31.接下来,将global_out+《0》、global_out+《1》、global_out+《2》、global_out+《3》、

···

、global_out+《n-2》、global_out+《n-1》n位数据送到三态门模块输入端。三态门由使能信号enable控制,高电平有效,该信号由移位寄存器产生,通过移位操作,enable《0》、enable《1》、enable《2》、enable《3》、

···

、enable《n-2》、enable《n-1》依次有效,使得n位数据经过缓冲器按最低位至最高位串行输出,完成第二步并串转换。

32.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

33.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明披露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1