一种差分谐波混频器电路、芯片及接收机

1.本发明涉及微电子技术领域,特别涉及一种差分谐波混频器电路、芯片及接收机。

背景技术:

2.混频器是无线收发机射频前端中实现频率变换的重要器件,接收机的射频前端将天线接收的射频信号转换为基带信号,发射机的射频前端将基带信号转变为射频信号。因此,射频前端中混频器技术指标的优劣将很大程度地影响整个毫米波系统的整体性能。

3.谐波混频器由于只需使用本振频率为射频频率的一半乃至更低频率的本振源,即可实现混频器的变频功能,因而谐波混频器对本振频率的要求不高,具有本振源成本低和设计较为简单的优势;但由于谐波混频器是基于本振信号的高次谐波分量进行混频,转换损耗较大且无法很好地抑制基波及谐波分量。

4.目前,在谐波混频器电路中常采用巴伦或变压器结构将单端本振信号lo转换为差分信号驱动平衡结构的混频器核心电路,以抑制lo偶次谐波信号,或者将中频差分输出转换为单端输出,以抑制二次谐波的泄漏,但巴伦和变压器电路会引入平衡度的限制,限制了中频输出端口和射频端口对本振信号的抑制效果,中频信号单端输出也会不可避免地引入或难以消除共模信号的干扰;而且,在谐波混频器电路中还常采用巴伦或移相结构进行隔离,以抑制射频信号对本振的干扰,但限于巴伦和移相结构的工作原理,针对射频信号的抑制被限制在满足某些特定条件的射频信号。

5.因此,有必要提出一种对谐波混频器的本振信号及其谐波分量有较好抑制效果,且能够较好地降低射频信号对本振的干扰的解决方案。

技术实现要素:

6.本技术的第一个方面,提供一种差分谐波混频器电路,不仅能够对本振信号及其谐波分量有较好抑制效果,还能够较好地降低射频信号对本振的干扰。

7.在本技术的第一方面中,提供的一种差分谐波混频器电路,其包括:

8.第一mos管,第二mos管;

9.第一谐振电路,第二谐振电路;

10.第一匹配电路,第二匹配电路;

11.以及,缝隙巴伦;

12.其中,所述第一mos管的栅极与所述第二mos管的栅极共同耦接于直流偏压输入端,且由本振信号输入端输入的本振信号耦合至所述第一mos管的栅极与所述第二mos管的栅极;

13.所述缝隙巴伦的第一输出端分别耦接于所述第一谐振电路的一端与所述第一匹配电路的一端,所述缝隙巴伦的第二输出端分别耦接于所述第二谐振电路的一端与所述第二匹配电路的一端,且由射频输入端输入的射频信号耦合至所述缝隙巴伦的输入端;

14.所述第一谐振电路的另一端耦接于所述第一mos管的漏极,所述第二谐振电路的

另一端耦接于所述第二mos管的漏极;所述第一匹配电路的另一端耦接至第一差分信号输出端,所述第二匹配电路的另一端耦接至第二差分信号输出端。

15.在一些可能的实施例中,构成所述缝隙巴伦的槽线的顶部和底部分别安装两个终端接地的1/4波长槽线。

16.在一些可能的实施例中,所述第一谐振电路和所述第二谐振电路被配置为具有相同的谐振电路结构;所述第一匹配电路和所述第二匹配电路被配置为具有相同的匹配电路结构。

17.在一些可能的实施例中,所述谐振电路结构为lc并联谐振电路。

18.在一些可能的实施例中,所述匹配电路结构包括:一条传输线、一个电容和一个电阻;其中,所述传输线的一端耦接于所述第一差分信号输出端或第二差分信号输出端,并分别通过所述电容以及所述电阻耦接于地,所述传输线的另一端耦接于所述缝隙巴伦的第一输出端或第二输出端。

19.在一些可能的实施例中,所述传输线被配置为通过一电容耦接于所述第一差分信号输出端或所述第二差分信号输出端。

20.在一些可能的实施例中,还包括:第一传输线、第二传输线、第三传输线以及第四传输线;

21.其中,所述第一传输线的一端耦接于所述第一mos管的栅极,所述第二传输线的一端耦接于所述第二mos管的栅极,所述第一传输线和所述第二传输线的另一端共同耦接于所述第三传输线的一端;所述直流偏压输入端通过所述第四传输线耦接于所述第三传输线的另一端,所述本振信号输入端通过一电容耦接于所述第三传输线的另一端。

22.本技术的第二方面,提供一种芯片,其包括:

23.衬底;以及,形成于所述衬底上的本技术的第一方面所提供的差分谐波混频器电路。

24.本技术的第三方面,提供一种接收机,其包括本技术的第一方面所提供的差分谐波混频器电路或本技术的第二方面所提供的芯片。

25.如此,本技术提供的差分谐波混频器电路中,射频信号单端输入至缝隙巴伦后,经缝隙巴伦转换为接近理想的差分信号,当差分信号加载到lo端口后会相互抵消,实现射频信号及其谐波到lo端口的高抑制度;而本振信号lo经mos差分对管的栅极共模馈入后,本振信号lo及其谐波加载至缝隙巴伦的差分信号的输出端口,由于缝隙巴伦对共模信号具有高抑制度,会阻碍共模信号的传输,即可实现本振信号lo及其谐波到rf端口的高抑制度;而且,由于中频信号由mos差分对管的漏极差分输出,可消除共模信号对中频信号的干扰,提高共模抑制度。

附图说明:

26.图1为本技术实施例中提供的一种差分谐波混频器电路的示意图;

27.图2为本技术实施例中提供的一种差分谐波混频器电路的示意图;

28.图3为在缝隙巴伦中单端信号转为差分信号时的电场分布图;

29.图4为在缝隙巴伦中共模信号从差分端输入时的电场分布图;

30.图5为本技术实施例中缝隙巴伦的简化模型示意图;

31.图6为本技术实施例中采用的缝隙巴伦结构在231ghz附近的幅度和相位不平衡度仿真结果图;

32.图7为图2所示的差分谐波混频器电路变频损耗仿真结果图;

33.图8为图2所示的差分谐波混频器电路lo和rf端口反射系数仿真结果图;

34.图9为图2所示的差分谐波混频器电路端口抑制度仿真结果图;

35.图10为图2所示的差分谐波混频器电路中频输出端口平衡度仿真结果图;

36.图11为本技术实施例中提供的一种芯片的结构示意图;

37.图12为本技术实施例中提供的接收机的结构示意图。

具体实施方式

38.下面结合附图及具体实施例对本发明作进一步的详细描述。但不应将此理解为本发明上述主题的范围仅限于以下的实施例,凡基于本发明内容所实现的技术均属于本发明的范围。

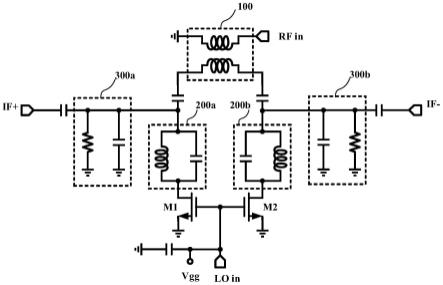

39.在本技术的一个实施例中,提供如图1所示的差分谐波混频器电路,其包括:

40.第一mos管m1,第二mos管m2;

41.第一谐振电路200a,第二谐振电路200b;

42.第一匹配电路300a,第二匹配电路300b;

43.以及,缝隙巴伦100;

44.其中,所述第一mos管m1的栅极与所述第二mos管m2的栅极共同耦接于直流偏压输入端vgg,且由本振信号输入端lo in输入的本振信号被配置为耦合至所述第一mos管m1的栅极与所述第二mos管m2的栅极;

45.所述缝隙巴伦100的第一输出端分别耦接于所述第一谐振电路200a的一端与所述第一匹配电路300a的一端,所述缝隙巴伦100的第二输出端分别耦接于所述第二谐振电路200b的一端与所述第二匹配电路300b的一端,且由射频输入端rf in输入的射频信号耦合至所述缝隙巴伦100的输入端;

46.所述第一谐振电路200a的另一端耦接于所述第一mos管m1的漏极,所述第二谐振电路200b的另一端耦接于所述第二mos管m2的漏极;所述第一匹配电路300a的另一端耦接至第一差分信号输出端if+,所述第二匹配电路300b的另一端耦接至第二差分信号输出端if-。

47.在本实施例中,由于对于mos管来说,当漏源电压较低时,其沟道可以近似为一个线性电阻,当超过某一极限值时则会表现出非线性,该极限值依赖于栅极电压的大小;因而,在标准小信号电压下,这个近似的沟道电阻可表现出良好的线性。那么,在图1中所示的差分谐波混频器电路中,本振信号lo激励和直流偏压vgg偏置共同耦合至mos差分对管m1、m2的栅极,在共模lo小信号的调制下,其沟道电阻线性变化;射频信号rf经过缝隙巴伦转换为两路差分信号由漏端分别加载到mos差分对管m1、m2上,实现本振信号与射频信号的相乘,并分别在漏端通过第一匹配电路和第二匹配电路进行高次谐波的滤波,得到差分的中频信号if+、if-。而且,在漏端分别接入第一谐振电路和第二谐振电路能够实现对本振信号lo的抑制。

48.在本技术的一个实施例中,提供如图2所示的差分谐波混频器电路,所述第一谐振

电路200a和所述第二谐振电路200b被配置为具有相同的谐振电路结构;所述第一匹配电路300a和所述第二匹配电路300b被配置为具有相同的匹配电路结构。

49.在本实施例中,所述谐振电路结构为lc并联谐振电路。而且,为了将混频器输出信号匹配至中频输出端口,在第一匹配电路300a中,其包括:一条传输线301a、一个电容和一个电阻;而且,该传输线301a的一端耦接于第一差分信号输出端if+,并分别通过电容以及电阻耦接于地,该传输线301a的另一端耦接于所述缝隙巴伦100的第一输出端rf+。同理地,在第二匹配电路300b中,其包括:一条传输线301b、一个电容和一个电阻;而且,该传输线301b的一端耦接于第二差分信号输出端if-,并分别通过电容以及电阻耦接于地,该传输线301b的另一端耦接于所述缝隙巴伦100的第二输出端rf-。

50.进一步地,由于第一匹配电路300a和第二匹配电路300b的一端分别耦合第一差分信号输出端if+与第二差分信号输出端if-;那么,在第一匹配电路300a中,传输线301a被配置为通过一电容耦接于所述第一差分信号输出端if+,同理地,在第二匹配电路300b,传输线301b被配置为通过一电容耦接于所述第二差分信号输出端if-。

51.在本实施例中,还包括:第一传输线401、第二传输线402、第三传输线403以及第四传输线404;其中,所述第一传输线401的一端耦接于所述第一mos管m1的栅极,所述第二传输线402的一端耦接于所述第二mos管m2的栅极,所述第一传输线401和所述第二传输线402的另一端共同耦接于所述第三传输线403的一端;所述直流偏压输入端vgg通过所述第四传输线404耦接于所述第三传输线403的另一端,所述本振信号输入端lo in通过一电容耦接于所述第三传输线403的另一端。

52.在本实施例中,由于缝隙巴伦在输入线上的激励下,在间隙结构边缘流动的电流在输出线下形成返回电流,即在输出端口上产生差分信号。同时,由于巴伦输出端口的完全对称,只有完全差分的准tem波才可以输出,该机制使得这种巴伦结构在宽带宽中表现出可忽略的相位和振幅的不平衡。再如图3和4所示,根据缝隙巴伦中单端信号转为差分信号时的电场分布情况以及共模信号从差分端输入时的电场分布情况,那么,在本实施例提供的差分谐波混频器电路工作时,射频信号单端输入至缝隙巴伦后,经缝隙巴伦转换为接近理想的差分信号,当差分信号加载到lo端口后会相互抵消,实现射频信号及其谐波到lo端口的高抑制度;而本振信号lo经mos差分对管的栅极共模馈入后,本振信号lo及其谐波加载至缝隙巴伦的差分信号的输出端口,由于缝隙巴伦对共模信号具有高抑制度,会阻碍共模信号的传输,即可实现本振信号lo及其谐波到rf端口的高抑制度;而且,由于中频信号由mos差分对管的漏极差分输出,可消除共模信号对中频信号的干扰,提高共模抑制度。

53.本实施例中,结合图3和图4所示,工字型的槽线结构构成缝隙巴伦,再如图5所示,在缝隙巴伦中其槽线的顶部和底部分别安装两个终端接地的1/4波长槽线,依靠阻抗转换实现高阻,并进行折叠以减小尺寸。

54.为进一步验证本实施例提供的差分谐波混频器电路的技术指标,不仅对该差分谐波混频器电路采用的缝隙巴伦结构进行仿真测试,得到如图6所示,该缝隙巴伦结构在231ghz附近的幅度和相位不平衡度仿真结果;还进一步地,对该差分谐波混频器电路分别进行相应的仿真测试,并得到变频损耗仿真结果、lo和rf端口反射系数仿真结果、端口抑制度仿真结果以及中频输出端口平衡度仿真结果。

55.其中,根据图7所示的变频损耗仿真结果,可知该谐波混频器在106ghz至126ghz工

作时其变频损耗均小于21db,在中心频点附近其变频损耗约为18.5db;根据图8所示的lo和rf端口反射系数仿真结果,可知在工作频带范围内其反射系数均在-10db以下;根据图9所示的端口抑制度仿真结果,可知在工作频带范围内,本振lo端口到中频if端口的隔离度均大于60db,本振lo端口到射频rf端口的隔离度均大于50db,射频rf端口到本振lo端口的隔离度均大于52db;根据图10所示的中频输出端口平衡度仿真结果,可知其在工作频带范围内,其幅度不平衡度在0.12db以内,即两端口的输出幅度相差0.12db以内,是几乎可以忽略的不平衡,其相位不平衡度在-179.3到-177度范围内,即两端口为近乎理想的差分信号。

56.本技术的一个实施例中,提供如图11所示的一种芯片,其包括:

57.衬底;以及,形成于所述硅衬底上的电路层,该电路层制作为本技术实施例中提供的差分谐波混频器电路,其中,该差分谐波混频器电路采用cmos工艺制作。

58.本技术的一个实施例中,还提供如图12所示的一种接收机,包括本技术实施例中提供的差分谐波混频器电路或芯片。

59.在本实施例中,差分谐波混频器电路或差分谐波混频器芯片的作用为:将输入的单端射频信号rf进行频谱线性搬移,即射频信号rf与本振信号lo相乘,输出为两路差分的中频信号if+和if-;如此,在接收机中,该混频器可以保证接收机获得较高的灵敏度、足够的放大量和适当的通频带。

60.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1