半导体结构及其形成方法与流程

本公开涉及半导体制造,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、dram(dynamic random access memory,动态随机存储器)等半导体结构中的csl(column select line,列选择线)可以控制外界从位线(bitline,bl)上读取到的具体信息。举例来说,在完成感测(sense)阶段的操作后,位线处于稳定的逻辑1电压状态,此时位线会对存储电容器进行充电。经过特定的时间后,存储电容器中的电荷就可以恢复到读取操作前的状态。最后,通过csl上的控制信号,外界就可以从位线上读取到具体的信息。在半导体结构中,csl的控制晶体管多采用”h”型结构设计。但是,由于半导体结构的尺寸不断微缩,“h”型结构的控制晶体管占用了较大的空间,这就导致相邻器件之间距离较远,而在器件区域外也没有多余的空间放置伪图形结构(dummy pattern),在半导体结构制造过程中的负载效应(loading effect)影响较大,所述位于区域交界处或边缘处的器件均匀性较差,从而降低了半导体结构的性能。

2、因此,如何降低半导体结构内部的负载效应,从而改善半导体结构的性能,是当前亟待解决的技术问题。

技术实现思路

1、本公开一些实施例提供一种半导体结构及其形成方法,用于降低半导体结构内部的负载效应,提高半导体结构内部的器件均匀性,从而改善半导体结构的性能。

2、根据一些实施例,本公开提供了一种半导体结构,包括:

3、衬底,所述衬底包括器件区域和伪器件区域;

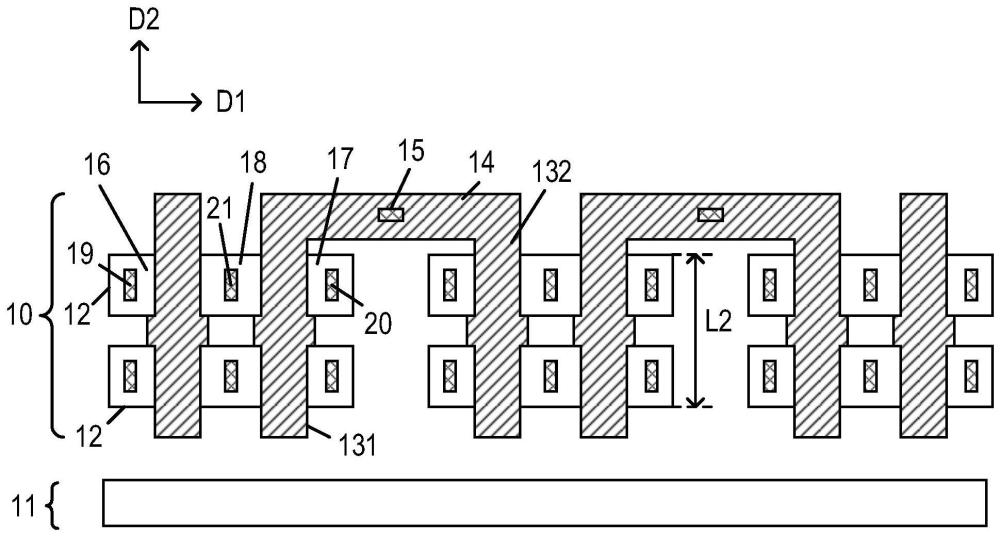

4、有源结构,位于所述器件区域,多个所述有源结构沿第一方向间隔排布,所述有源结构包括沿第二方向排布且相互连接的多个有源区,所述第一方向和所述第二方向均与所述衬底的顶面平行,且所述第一方向与所述第二方向相交;

5、栅极结构,位于所述器件区域,多个所述栅极结构沿第一方向间隔排布,所述栅极结构包括第一主体部、第二主体部以及连接部,所述第一主体部与所述第二主体部分别覆盖相邻两个所述有源结构相对靠近的部分且在所述第二方向上跨越多个所述有源区,所述第一主体部通过所述连接部与所述第二主体部相连,所述连接部位于相邻两个所述有源结构的第一侧;

6、伪有源结构,位于所述伪器件区域且位于所述有源结构的第二侧,其中,所述第一侧与所述第二侧为所述有源结构在沿所述第二方向上的同一侧或相对的两侧。

7、在一些实施例中,多个所述伪有源结构沿所述第一方向间隔排布,所述伪有源结构包括沿所述第二方向排布且相互连接的多个伪有源区。

8、在一些实施例中,所述连接部沿所述第一方向延伸,所述第一主体部和所述第二主体部均沿所述第二方向延伸,且所述第一主体部和所述第二主体部沿所述第二方向位于所述连接部的同一侧;

9、沿所述第一方向相邻的两个所述有源结构中,一个所述栅极结构中的所述第一主体部覆盖其中一个所述有源结构中的所述有源区、所述第二主体部覆盖另一个所述有源结构中的所述有源区。

10、在一些实施例中,所述有源区包括沟道区,所述有源结构包括沿所述第二方向间隔排布的两个所述有源区、以及位于两个所述有源区之间的连接区,所述连接区沿所述第二方向的相对两端分别连接两个所述有源区中的所述沟道区;

11、沿所述第一方向相邻的两个所述有源结构中,一个所述栅极结构中的所述第一主体部连续覆盖其中一个所述有源结构中两个所述有源区中的所述沟道区、所述第二主体部连续覆盖另一个所述有源结构中两个所述有源区中的所述沟道区。

12、在一些实施例中,所述第一主体部和所述第二主体部关于一条轴线对称分布,所述轴线沿所述第二方向延伸且穿过所述连接部的中心。

13、在一些实施例中,所述第一主体部包括覆盖所述有源区中的所述沟道区的第一部分、以及覆盖所述连接区且与所述第一部分连接的第二部分;

14、所述第一部分沿所述第一方向的宽度小于或者等于所述第二部分沿所述第一方向的宽度。

15、在一些实施例中,所述沟道区包括沿所述第一方向排布的第一沟道区和第二沟道区;所述有源区还包括:

16、公共源极区,位于所述第一沟道区和所述第二沟道区之间;

17、第一漏极区,沿所述第一方向位于所述第一沟道区远离所述公共源极区的一侧;

18、第二漏极区,沿所述第一方向位于所述第二沟道区远离所述公共源极区的一侧;

19、所述连接区包括第一连接区和第二连接区,所述第一连接区连接所述有源结构中的两个所述有源区中的所述第一沟道区,所述第二连接区连接所述有源结构中的两个所述有源区中的所述第二沟道区。

20、在一些实施例中,对于沿所述第一方向相邻的两个所述栅极结构,其中一个所述栅极结构中的所述第一主体部覆盖所述有源结构中的所述第一沟道区、另一个所述栅极结构中的所述第二主体部覆盖同一个所述有源结构中的所述第二沟道区。

21、在一些实施例中,还包括:

22、第一隔离结构,位于沿所述第一方向相邻的所述有源结构之间;

23、第二隔离结构,位于所述有源结构内沿所述第二方向相邻的所述有源区之间,所述第一隔离结构沿所述第一方向的宽度大于所述第二隔离结构沿所述第二方向的宽度。

24、在一些实施例中,所述有源结构中的多个所述有源区沿所述第二方向对准排布;

25、所述第二隔离结构沿所述第二方向的宽度小于0.3μm。

26、在一些实施例中,所述第一侧与所述第二侧为所述有源结构在沿所述第二方向上的相对的两侧;所述半导体结构还包括:

27、第三隔离结构,位于所述有源结构与所述伪有源结构之间。

28、在一些实施例中,还包括:

29、第一外围电路,位于所述器件区域外部;

30、栅极引线,一端与所述第一外围电路电连接、另一端与所述栅极结构中的所述连接部电连接。

31、在一些实施例中,还包括:

32、栅极引线端口,位于所述连接部上,用于与所述栅极引线电连接,在沿所述第二方向上,所述栅极引线端口与所述第一隔离结构的中心位置对齐。

33、根据另一些实施例,本公开还提供了一种半导体结构的形成方法,包括如下步骤:

34、提供衬底,所述衬底包括器件区域和伪器件区域;

35、于所述器件区域形成有源结构、并于所述伪器件区域形成伪有源结构,多个所述有源结构沿第一方向间隔排布,所述有源结构包括沿第二方向排布且相互连接的多个有源区,所述伪有源结构位于所述有源结构的第二侧,所述第一方向和所述第二方向均与所述衬底的顶面平行,且所述第一方向与所述第二方向相交;

36、于所述器件区域形成栅极结构,多个所述栅极结构沿所述第一方向间隔排布,所述栅极结构包括第一主体部、第二主体部以及与连接部,所述第一主体部与所述第二主体部分别覆盖相邻两个所述有源结构相对靠近的部分且在所述第二方向上跨越多个所述有源区,所述第一主体部通过所述连接部与所述第二主体部相连,所述连接部位于相邻两个所述有源结构的第一侧,其中,所述第一侧与所述第二侧为所述有源结构沿所述第二方向上的同一侧或相对的两侧。

37、在一些实施例中,提供衬底,于所述器件区域形成有源结构、并于所述衬底上的伪器件区域形成伪有源结构的具体步骤包括:

38、提供初始衬底;

39、图案化所述初始衬底,形成多个所述有源结构和多个所述伪有源结构,多个所述伪有源结构沿所述第一方向间隔排布的,所述伪有源结构包括沿所述第二方向排布且相互连接的多个伪有源区,残留于所述有源结构和所述伪有源结构下方的所述初始衬底作为所述衬底,所述有源结构中的所述有源区包括沟道区,所述有源结构包括沿所述第二方向间隔排布的两个所述有源区、以及位于两个所述有源区之间的连接区,所述连接区沿所述第二方向的相对两端分别连接两个所述有源区中的所述沟道区。

40、在一些实施例中,于所述器件区域形成栅极结构的具体步骤包括:

41、沉积导电材料于所述器件区域,形成所述第一主体部、所述第二主体部和所述连接部,所述连接部沿所述第一方向延伸,所述第一主体部和所述第二主体部均沿所述第二方向延伸,且所述第一主体部和所述第二主体部沿所述第二方向位于所述连接部的同一侧,沿所述第一方向相邻的两个所述有源结构中,一个所述栅极结构中的所述第一主体部覆盖其中一个所述有源结构中的所述有源区、所述第二主体部覆盖另一个所述有源结构中的所述有源区。

42、在一些实施例中,所述沟道区包括沿所述第一方向排布的第一沟道区和第二沟道区;于所述器件区域形成栅极结构的具体步骤包括:

43、于每个所述有源结构上方形成分别覆盖所述第一沟道区和所述第二沟道区的所述第一主体部和所述第二主体部、并同时形成沿所述第一方向间隔排布的多个所述连接部,形成多个所述栅极结构;

44、对于沿所述第一方向相邻的两个所述栅极结构,其中一个所述栅极结构中的所述第一主体部覆盖所述有源结构中的所述第一沟道区、另一个所述栅极结构中的所述第二主体部覆盖同一个所述有源结构中的所述第二沟道区。

45、在一些实施例中,于所述器件区域形成栅极结构之后,还包括如下步骤:

46、于所述衬底上形成栅极引线,所述栅极引线一端与第一外围电路电连接、另一端与所述栅极结构中的所述连接部电连接,所述第一外围电路位于所述器件区域外部。

47、本公开一些实施例提供的半导体结构及其形成方法,通过在有源结构中设置多个沿第二方向排布且相互连接的有源区,在确保有源区数量保持不变的前提下,缩小包括多个所述有源结构的器件区域沿第二方向的尺寸,一方面,能够提高半导体结构的集成度;另一方面,还能够为在器件区域沿第二方向的外部提供设置伪器件区域的空间,从而降低了半导体结构的负载效应,提高了器件区域内部有源结构的均匀性,改善了半导体结构的性能。

- 还没有人留言评论。精彩留言会获得点赞!