列级读出电路、列级逐次逼近型模数转换器及红外成像仪

1.本发明涉及集成电路领域,尤其涉及一种列级读出电路、列级逐次逼近型模数转换器以及红外成像仪。

背景技术:

2.在过去的几年,红外成像已经应用于非常广阔的领域,比如生物医学、航天探测、消防等等,作为红外成像系统的核心,红外焦平面电路和电路中的adc的设计越来越受到人们的关注。

3.传统的红外焦平面adc有像素级、列级、芯片级,考虑到单通道芯片级adc的严格速度限制和像素级adc的功耗限制,列级adc对于面积、采样率、功耗和信噪比之间进行很好的权衡,因此目前被广泛的采用。传统的列级adc具有单斜坡型adc、循环adc、sar adc、delta sigma型adc。

4.单斜adc被广泛使用,因为其结构简单、面积最小、并且消耗功耗较低。但是单斜adc量化n bit,需要2^n个时钟,转化速率很慢,不适合于中高帧频的使用。

5.循环adc量化n bit仅仅需要n个时钟,是一种高速adc,并且占用面积较小。但是循环adc设计需要高增益、高功耗、低失调的运放,且能量效率不高,功耗和设计的困难限制了使用。

6.delta-sgima adc,利用过采样和noise shaping的特性,可以实现高精度和高的动态范围。但由于需要过采样,转换速度较慢,为了提高速度,常使用高阶的调制器,但是这样会增加系统的复杂度,消耗更多的硬件代价和功耗,降低系统稳定性。

7.sar adc转换n bit需要n个clk,适合于中高速帧频的应用,但是传统的sar adc需要一个大的电容阵列,一个比较器和一个sar逻辑。对于一个n bit的sar adc,其需要2n个c0,其中的c0表示单位电容,因此会导致电容阵列占一个非常大的面积,同时还给信号线的布局和布置带来困难,使得这种结构的竞争力降低。

8.因此,如何在降低sar adc数模转换器(dac)占用面积的同时,提升量化转换的效率,降低功耗,是一个亟需解决的问题。

技术实现要素:

9.鉴于上述问题,提出了本发明以提供解决上述问题或者部分地解决上述问题的一种列级读出电路、列级逐次逼近型模数转换器以及红外成像仪。

10.本发明实施例第一方面提供一种列级读出电路,所述列级读出电路包括:多个adc模块、时序控制单元、并转串输出电路以及高m bit电阻电压缓冲器;

11.每个adc模块为一个n列并用的sar adc;

12.对于模数转换器的dac,若其整体为x bit,令x=m+l,其中,高m bit采用电阻dac形成所述高m bit电阻电压缓冲器,所述高m bit电阻电压缓冲器产生的基准电压为所有的adc模块所并用,低l bit采用桥接电容的电容dac;

13.每个所述adc模块包括:奇数列选择器、偶数列选择器、比较器、控制逻辑单元以及两组桥接电容dac;

14.所述两组桥接电容dac分别为奇数列用桥接电容dac和偶数列用桥接电容dac,当所述奇数列用桥接电容dac对n列中的奇数列传输的像素电压进行采样时,所述偶数列用桥接电容dac同时对n列中偶数列已采样完成的像素电压进行量化,或者,当所述偶数列用桥接电容dac对n列中的偶数列传输的像素电压进行采样时,所述奇数列用桥接电容dac同时对n列中奇数列已采样完成的像素电压进行量化;

15.所述奇数列选择器根据列级译码选通所述n列中的任一奇数列,将该奇数列的像素电压传输至所述奇数列用桥接电容dac;

16.所述偶数列选择器根据列级译码选通所述n列中的任一偶数列,将该偶数列的像素电压传输至所述偶数列用桥接电容dac;

17.对于所述奇数列用桥接电容dac和所述偶数列用桥接电容dac,均有:

18.每个桥接电容的上极板互相连接形成桥接电容dac的上极板,每个桥接电容的下极板通过各自的下极板采样开关,接收各自对应列的像素电压,每个桥接电容的下极板通过各自的电容控制开关,接收所述基准电压;

19.所述奇数列用桥接电容dac的上极板与所述偶数列用桥接电容dac的上极板之间,通过两组奇偶开关连接,并通过其中一组奇偶开关与所述比较器连接;

20.所述比较器的输出端与所述控制逻辑单元、所述并转串输出电路分别连接,所述比较器的输出信号即为其所在adc模块的量化结果;

21.所述控制逻辑单元根据所述比较器的输出信号,产生控制所述奇数列用桥接电容dac中每个桥接电容下极板采样开关和电容控制开关的奇控制信号,以及产生控制所述偶数列用桥接电容dac中每个桥接电容下极板采样开关和电容控制开关的偶控制信号;

22.所述并转串输出电路接收所述比较器的输出信号,进行多个所述adc模块量化结果的并转串,并数字输出片外。

23.可选地,两组所述奇偶开关包括:第一组奇偶开关和第二组奇偶开关;

24.所述第一组奇偶开关包括:第一奇开关和第一偶开关;

25.所述第二组奇偶开关包括:第二奇开关和第二偶开关;

26.所述第一奇开关的第一端与所述奇数列用桥接电容dac的上极板连接,所述第一奇开关的第二端与所述第一偶开关的第一端连接,并接收共模电压;

27.所述第一偶开关的第二端与所述偶数列用桥接电容dac的上极板连接;

28.所述第二偶开关的第一端与所述奇数列用桥接电容dac的上极板连接,所述第二偶开关的第二端与所述第二奇开关的第一端、所述比较器的反相端分别连接;

29.所述第二奇开关的第二端与所述偶数列用桥接电容dac的上极板连接。

30.可选地,所述比较器的同相端接收所述共模电压,所述比较器对所述第二偶开关的第二端或者所述第二奇开关的第一端输出的信号,与所述共模电压进行比较,得到所述比较器的输出信号;

31.所述控制逻辑单元根据所述比较器的输出信号,产生所述奇控制信号,和所述偶控制信号。

32.可选地,在任一时段,若所述奇数列用桥接电容dac对n列中任一奇数列传输的像

素电压进行采样,则所述偶数列用桥接电容dac在该时段对n列中任一偶数列已采样完成的像素电压进行量化;

33.在所述奇数列用桥接电容dac对n列中任一奇数列传输的像素电压进行采样时,所述第一奇开关和所述第二奇开关均闭合,所述第一偶开关和所述第二偶开关均断开,所述奇数列用桥接电容dac中每个电容的下极板采样开关,受控于所述奇控制信号而闭合,所述奇数列用桥接电容dac中每个电容的电容控制开关,受控于所述奇控制信号而断开。

34.可选地,在任一时段,若所述奇数列用桥接电容dac对n列中任一奇数列传输的像素电压进行采样,则所述偶数列用桥接电容dac在该时段对n列中任一偶数列已采样完成的像素电压进行量化;

35.在所述偶数列用桥接电容dac对n列中任一偶数列已采样完成的像素电压进行量化时,所述第一奇开关和所述第二奇开关均闭合,所述第一偶开关和所述第二偶开关均断开,所述偶数列用桥接电容dac中每个电容的下极板采样开关,受控于所述偶控制信号而断开,所述偶数列用桥接电容dac中每个电容的电容控制开关,受控于所述偶控制信号而选择性的闭合,以实现对所述基准电压的逐次逼近比较量化。

36.可选地,所述基准电压包括:v

bot

和v

top

;

37.所述偶数列用桥接电容dac中每个电容的电容控制开关,受控于所述偶控制信号而选择性的闭合,所述v

top

的电压比所述v

bot

的电压高则连接到所述v

top

的电容控制开关连接的高m bit电阻电压范围为连接到所述v

bot

的电容控制控制开关连接的高m bit电阻电压范围为以实现对所述基准电压的逐次逼近比较量化的过程包括:

38.步骤s1:将所述电容控制开关全部切换到接所述v

bot

,进行高m bit电阻电压的选择,其中,控制连接到所述v

bot

与连接到所述v

top

的电容控制开关的偶控制信号的逻辑相同;

39.步骤s2:设qs为任一偶数列采样结束时,所述偶数列用桥接电容dac中所有桥接电容上所存储的电荷,c

tot

为所述偶数列用桥接电容dac中所有桥接电容的总电容,则有下式:

40.qs=c

tot

×

(v

cm-v

col

[n]

[0041]

上式中,v

cm

表示所述共模电压,v

col

[n]表示任一偶数列采样得到的像素电压;

[0042]

当所述偶数列用桥接电容dac中所有桥接电容的下极板通过各自的电容控制开关全部选通连接所述v

bot

时,设此时所述偶数列用桥接电容dac中所有桥接电容的上极板电压为va,则有下式:

[0043]qs

=c

tot

×

(v

a-v

bot

)

[0044]va

=v

cm

+v

bot-v

col

[n]

[0045]

此时有:所述比较器的一端电压为v

cm

,一端电压为va,则所述比较器进行比较的电压v

ε

为:

[0046]vε

=v

col

[n]-v

bot

[0047]

步骤s3:进行判断时,首先,所述v

bot

通过控制开关选择的电压值为若所

述比较器的输出信号为1,则说明任一偶数列采样得到的像素电压v

col

[n]比高,需要调整连接所述v

bot

的电容控制开关,选择更高的电压值

[0048]

若所述比较器的输出信号为0,需要调整连接所述v

bot

的电容控制开关,选择更低的基准电压以对所述基准电压进行逐次逼近比较,选择一个适合于量化像素电压的电压段;

[0049]

步骤s4:根据比较器的结果,不断切换连接所述v

bot

的电容控制开关,以选择接不同的高m bit电阻电压缓冲器产生的基准电压,进行比较,以选择出适合于所量化的像素电压的v

bot

;

[0050]

步骤s5:在对所述高mbit的基准电压的比较结束后,选择出一个相应于任一偶数列采样得到的像素电压v

col

[n]的v

bot

,因控制连接到所述v

bot

与连接到所述v

top

的电容控制开关的偶控制信号的逻辑相同,此时有:相应于任一偶数列采样得到的像素电压v

col

[n]的v

top

也选择完毕;

[0051]

在确定一个相应于任一偶数列采样得到的像素电压v

col

[n]的一个v

bot

和一个v

top

后,进行低l bit的电容dac的逐次逼近比较量化,将最高位电容接v

top

,进行相应的比较,根据所述比较器的结果,进而决定最高位电容控制开关接v

top

还是v

bot

;

[0052]

步骤s6:重复步骤s5,对于低l bit的电容dac的剩余位电容进行逐步逼近的量化,进而得到相应的码值。

[0053]

可选地,所述列级读出电路还包括:时序控制单元;

[0054]

两组所述奇偶开关均受控于所述时序控制单元的时序控制信号,所述第一奇开关和所述第二奇开关的时序相同,所述第一偶开关和所述第二偶开关的时序相同;

[0055]

在所述第一奇开关和所述第二奇开关接收到的时序控制信号为高电平时,所述第一奇开关和所述第二奇开关均闭合,所述第一偶开关和所述第二偶开关均断开,且所述奇数列选择器根据列级译码选通所述n列中的任一奇数列;

[0056]

在所述第一偶开关和所述第二偶开关接收到的时序控制信号为高电平时,所述第一偶开关和所述第二偶开关均闭合,所述第一奇开关和所述第二奇开关均断开,且所述偶数列选择器根据列级译码选通所述n列中的任一偶数列。

[0057]

可选地,所述奇数列用桥接电容dac对n列中任一奇数列传输的像素电压进行采样的时间,与所述偶数列用桥接电容dac对n列中任一偶数列已采样完成的像素电压进行量化的时间相等。

[0058]

本发明实施例第二方面提供一种列级逐次逼近型模数转换器,所述列级逐次逼近型模数转换器包括如第一方面任一所述的列级读出电路。

[0059]

本发明实施例第三方面提供一种红外成像仪,所述红外成像仪包括:光电流探测器以及如第一方面任一所述的列级读出电路。

[0060]

本发明提供的列级读出电路,包括:多个adc模块、时序控制单元、并转串输出电路以及高m bit电阻电压缓冲器。每个adc模块为一个n列并用的sar adc;对于模数转换器的

dac,若其整体为x bit,令x=m+l,其中,高m bit采用电阻dac形成高m bit电阻电压缓冲器,该高m bit的电阻串电压基准缓冲器产生的基准电压为所有的adc模块所并用,而低lbit采用桥接电容的电容dac。

[0061]

每个adc模块包括:奇数列选择器、偶数列选择器、比较器、控制逻辑单元以及两组桥接电容dac;两组桥接电容dac分别为奇数列用桥接电容dac和偶数列用桥接电容dac,当奇数列用桥接电容dac对n列中的奇数列传输的像素电压进行采样时,偶数列用桥接电容dac同时对n列中偶数列已采样完成的像素电压进行量化。或者,当偶数列用桥接电容dac对n列中的偶数列传输的像素电压进行采样时,奇数列用桥接电容dac同时对n列中奇数列已采样完成的像素电压进行量化。

[0062]

奇数列选择器根据列级译码选通n列中的任一奇数列,将该奇数列的像素电压传输至奇数列用桥接电容dac;偶数列选择器根据列级译码选通n列中的任一偶数列,将该偶数列的像素电压传输至偶数列用桥接电容dac。对于奇数列用桥接电容dac和偶数列用桥接电容dac,均有:

[0063]

每个桥接电容的上极板互相连接形成桥接电容dac的上极板,每个桥接电容dac的下极板通过各自的下极板采样开关,接收各自对应列的像素电压,每个桥接电容dac的下极板通过各自的电容控制开关,接收电阻基准电压。

[0064]

奇数列用桥接电容dac的上极板与偶数列用桥接电容dac的上极板之间,通过两组奇偶开关连接,并通过其中一组奇偶开关与比较器连接。比较器的输出端与控制逻辑单元连接,比较器的输出信号即为其所在adc模块的量化结果。

[0065]

控制逻辑单元根据比较器的输出信号,产生控制奇数列用桥接电容dac中每个电容下极板采样开关和电容控制开关的奇控制信号,和控制偶数列用桥接电容dac中每个电容下极板采样开关和电容控制开关的偶控制信号。并转串输出电路接收比较器的输出信号,进行多个adc模块量化结果的并转串,并数字输出片外。

[0066]

本发明所提列级读出电路,通过上述结构,高m bit采用电阻dac形成高m bit电阻电压缓冲器,产生的基准电压为多个adc模块共用。而低l bit采用桥接电容的电容dac,每个adc模块内部仅保留低l bit的电容dac,其采用桥接电容dac。与同精度纯电容阵列sar adc相比,本发明所提列级读出电路,减小了dac阵列面积,并且由于采用了奇偶电容dac,变相的增加了对像素电压的采样时间,间接提升了量化转化的效率,减小了对于像素到列的电流需求,降低了功耗,具有较高的实用性。

附图说明

[0067]

为了更清楚地说明本发明实施例的技术方案,下面将对本发明实施例的描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

[0068]

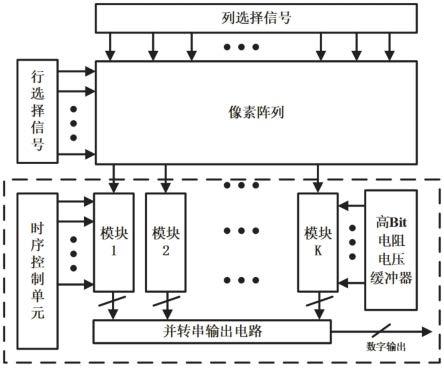

图1是本发明实施例中模数转换器的整体结构示意图;

[0069]

图2是本发明实施例中一种优选的adc模块的结构示意图;

[0070]

图3是本发明实施例中时序控制单元发送的奇偶开关的时序图。

具体实施方式

[0071]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0072]

本发明的一种列级读出电路,是在目前传统sar adc结构的基础上,全新设计而成,在像素阵列部分与传统sar adc结构相同,分别由行选择信号和列选择信号来对像素阵列进行积分、采样。

[0073]

而在列级的结构上,区别于传统sar adc的列级读出电路,本发明所提列级读出电路包括:多个adc模块、时序控制单元、并转串输出电路以及高m bit电阻电压缓冲器。

[0074]

参照图1,示出了本发明实施例中,模数转换器的整体结构示意图,其中虚框部分即为本发明所提列级读出电路结构,多个adc模块用模块1、模块2、

……

模块k表示。高m bit电阻电压缓冲器产生的基准电压为模块1、模块2、

……

模块k所并用。模块1、模块2、

……

模块k各自的量化转换结果传输至并转串输出电路,由并转串输出电路将并行数字信号转换为串行数字信号,最终进行数字输出,读出片外。

[0075]

本发明所提列级读出电路中,每个adc模块为一个n列并用的sar adc。即每个adc模块对应像素阵列的n列,所有adc模块加起来对应整个像素阵列的所有列。例如:像素阵列共有256列,n=16,则每个adc模块为一个16列并用的sar adc,一共需要16个adc模块,对应256列的像素阵列。

[0076]

对于模数转换器的dac,若模数转换器的整体为x bit,可令x=m+l,其中,高m bit采用电阻dac形成高m bit电阻电压缓冲器,该高m bit的电阻电压缓冲器产生的基准电压为所有的adc模块所并用,而低l bit采用桥接电容的电容dac。

[0077]

每个adc模块包括:奇数列选择器、偶数列选择器、比较器、控制逻辑单元以及两组桥接电容dac。两组桥接电容dac分别为奇数列用桥接电容dac和偶数列用桥接电容dac。当奇数列用桥接电容dac对n列中的奇数列传输的像素电压进行采样时,偶数列用桥接电容dac同时对n列中偶数列已采样完成的像素电压进行量化。或者,当偶数列用桥接电容dac对n列中的偶数列传输的像素电压进行采样时,奇数列用桥接电容dac同时对n列中奇数列已采样完成的像素电压进行量化。

[0078]

当奇数列选择器根据列级译码选通n列中的任一奇数列时,将该奇数列的像素电压传输至奇数列用桥接电容dac;当偶数列选择器根据列级译码选通n列中的任一偶数列,将该偶数列的像素电压传输至偶数列用桥接电容dac。

[0079]

对于奇数列用桥接电容dac和偶数列用桥接电容dac的结构上来说,均有:

[0080]

每个桥接电容的上极板互相连接形成桥接电容dac的上极板,每个桥接电容的下极板通过各自的下极板采样开关,接收各自对应列的像素电压,每个桥接电容的下极板通过各自的电容控制开关,接收基准电压。

[0081]

而奇数列用桥接电容dac的上极板与偶数列用桥接电容dac的上极板之间,通过两组奇偶开关连接,并通过其中一组奇偶开关与比较器连接。比较器的输出端与控制逻辑单元、并转串输出电路分别连接,比较器的输出信号即为其所在adc模块的量化结果。

[0082]

控制逻辑单元根据比较器的输出信号,产生控制奇数列用桥接电容dac中每个桥

接电容下极板采样开关和电容控制开关的奇控制信号,以及产生控制偶数列用桥接电容dac中每个桥接电容下极板采样开关和电容控制开关的偶控制信号。并转串输出电路接收比较器的输出信号,进行多个adc模块量化结果的并转串,并数字输出片外。即并转串输出电路进行多个adc模块量化结果的并转串,并数字输出片外。

[0083]

对于两组奇偶开关来说,一种较优的结构包括:第一组奇偶开关和第二组奇偶开关;第一组奇偶开关包括:第一奇开关和第一偶开关;第二组奇偶开关包括:第二奇开关和第二偶开关。

[0084]

第一奇开关的第一端与奇数列用桥接电容dac的上极板连接,第一奇开关的第二端与第一偶开关的第一端连接,并接收共模电压。第一偶开关的第二端与偶数列用桥接电容dac的上极板连接;第二偶开关的第一端与奇数列用桥接电容dac的上极板连接,第二偶开关的第二端与第二奇开关的第一端、比较器的反相端分别连接。第二奇开关的第二端与偶数列用桥接电容dac的上极板连接。

[0085]

本发明实施例中,比较器的同相端接收共模电压,比较器对第二偶开关的第二端或者第二奇开关的第一端输出的信号,与共模电压进行比较,得到比较器的输出信号,即得到比较器所在adc的量化结果。而控制逻辑单元根据比较器的输出信号,产生奇控制信号和偶控制信号。

[0086]

本发明实施例中,列级读出电路还包括:时序控制单元。两组奇偶开关均受控于时序控制单元的时序控制信号,第一奇开关和第二奇开关的时序相同,第一偶开关和第二偶开关的时序相同。

[0087]

在第一奇开关和第二奇开关接收到的时序控制信号为高电平时,第一奇开关和第二奇开关均闭合,第一偶开关和第二偶开关均断开,且奇数列选择器根据列级译码选通n列中的任一奇数列。

[0088]

类似的,在第一偶开关和第二偶开关接收到的时序控制信号为高电平时,第一偶开关和第二偶开关均闭合,第一奇开关和第二奇开关均断开,且偶数列选择器根据列级译码选通n列中的任一偶数列。

[0089]

在任一时段,若奇数列用桥接电容dac对n列中任一奇数列传输的像素电压进行采样,则偶数列用桥接电容dac在该时段对n列中任一偶数列已采样完成的像素电压进行量化。而在奇数列用桥接电容dac对n列中任一奇数列传输的像素电压进行采样时,第一奇开关和第二奇开关均闭合,第一偶开关和第二偶开关均断开,奇数列用桥接电容dac中每个桥接电容的下极板采样开关,受控于奇控制信号而闭合,奇数列用桥接电容dac中每个桥接电容的电容控制开关受控于奇控制信号而断开。

[0090]

在任一时段,若奇数列用桥接电容dac对n列中任一奇数列传输的像素电压进行采样,偶数列用桥接电容dac在该时段对n列中任一偶数列已采样完成的像素电压进行量化。在偶数列用桥接电容dac对n列中任一偶数列已采样完成的像素电压进行量化时,第一奇开关和第二奇开关均闭合,第一偶开关和第二偶开关均断开,偶数列用桥接电容dac中每个桥接电容的下极板采样开关,受控于偶控制信号而断开,偶数列用桥接电容dac中每个桥接电容的电容控制开关,受控于偶控制信号而选择性的闭合,以实现对基准电压的逐次逼近比较量化。

[0091]

通过上述结构也可知晓:奇数列用桥接电容dac对n列中任一奇数列传输的像素电

压进行采样的时间,与偶数列用桥接电容dac对n列中任一偶数列已采样完成的像素电压进行量化的时间相等。这样对像素电压的采样时间进行了延长,间接提升了量化转化的效率,减小了对于像素到列的电流需求,降低了功耗。

[0092]

为了更清楚的解释和说明adc模块,参照图2,示出了本发明实施例中一种优选的adc模块的结构示意图。图2中以n=16为例,即一个adc模块为16列并用的。图2中cso《3:1》表示奇数列的列级译码信号,cse《3:1》表示偶数列的列级译码信号,这两个信号分别用于选通相应列的开关。接收cso《3:1》信号的8:1mux为奇数列选择器,接收cse《3:1》信号的8:1mux为偶数列选择器。

[0093]

通过图2可以知晓,奇数列选择器接收16列中奇数列的像素电压v

col

[1]、v

col

[3]、

……vcol

[15];偶数列选择器接收16列中偶数列的像素电压v

col

[2]、v

col

[4]、

……vcol

[16]。而16列的像素电压v

col

[1]~v

col

[16]均是由像素到列级传输电路传输而来。

[0094]

图2中v

bot

和v

top

分别表示高m bit电阻电压缓冲器输出的两个基准电压。图2中上部分的电容c0~c

l

即为奇数列的桥接电容,下部分的电容c0~c

l

即为偶数列的桥接电容。靠右的一组o、e表示第一组奇偶开关,靠左的o、e表示第二组奇偶开关。第一组奇偶开关中的o表示第一奇开关,e表示第一偶开关;自然地,第二组奇偶开关中的o表示第二奇开关,e表示第二偶开关。v

cm

表示共模电压。控制逻辑表示控制逻辑单元。控制逻辑分别产生奇数dac控制信号(即奇控制信号)和偶数dac控制信号(即偶控制信号)。

[0095]

图2中无论是奇数列的桥接电容还是偶数列的桥接电容,其中的c1~c

l

电容的下极板均有三路开关,而c0电容的下极板有两路开关。其中与8:1选择器的输出端连接的开关即为每个桥接电容的下极板采样开关,而与v

bot

和v

top

分别连接的开关即为每个桥接电容的电容控制开关。奇数列的桥接电容中c0电容的电容控制开关仅与v

top

连接,偶数列的桥接电容中c0电容的电容控制开关仅与v

bot

连接。

[0096]

假设某一时段,对于像素阵列中的奇数列v

col

[3]的像素电压开始采样,自然同时对采样完成的像素阵列中的偶数列v

col

[2]的像素电压开始量化。

[0097]

对于奇数列桥接电容dac,此时对于v

col

[3]传输的像素电压进行采样,该过程中,第一奇开关o、第二奇开关o均闭合,奇数列桥接电容dac的下极板采样开关闭合,cso《3:1》列译码通过奇数列选择器8:1mux进行选通,将v

col

[3](像素阵列中的第三列)的像素电压选择后传输至奇数列桥接电容dac,此时奇数列桥接dac对于v

col

[3]的像素电压进行采样。

[0098]

在对于奇数列v

col

[3]的像素电压采样的同时,对于偶数列v

col

[2]进行量化,因此采样的时间等于整个v

col

[2]的量化时间,比起采用单一电容dac的adc,采样时间大大延长。

[0099]

对于偶数列v

col

[2]进行量化,需要第一偶开关e、第二偶开关e均断开,偶数列用桥接电容dac中每个桥接电容的下极板采样开关均断开,偶数列选择器8:1mux并不进行选择。在上述条件下,偶数列用桥接电容dac中每个桥接电容的电容控制开关,受控于偶控制信号而选择性的闭合,以实现对基准电压的逐次逼近比较量化的过程,该过程包括:

[0100]

步骤s1:将所述电容控制开关全部切换到接所述v

bot

,进行高m bit电阻电压的选择,其中,控制连接到所述v

bot

与连接到所述v

top

的电容控制开关的偶控制信号的逻辑相同;

[0101]

步骤s2:设qs为任一偶数列采样结束时,所述偶数列用桥接电容dac中所有桥接电容上所存储的电荷,c

tot

为所述偶数列用桥接电容dac中所有桥接电容的总电容,则有下式:

[0102]qs

=c

tot

×

(v

cm-v

col

[n]

[0103]

上式中,v

cm

表示所述共模电压,v

col

[n]表示任一偶数列采样得到的像素电压;

[0104]

当所述偶数列用桥接电容dac中所有桥接电容的下极板通过各自的电容控制开关全部选通连接所述v

bot

时,设此时所述偶数列用桥接电容dac中所有桥接电容的上极板电压为va,则有下式:

[0105]qs

=c

tot

×

(v

a-v

bot

)

[0106]va

=v

cm

+v

bot-v

col

[n]

[0107]

此时有:所述比较器的一端电压为v

cm

,一端电压为va,则所述比较器进行比较的电压v

ε

为:

[0108]vε

=v

col

[n]-v

bot

[0109]

步骤s3:进行判断时,首先,所述v

bot

通过控制开关选择的电压值为若所述比较器的输出信号为1,则说明任一偶数列采样得到的像素电压v

col

[n]比高,需要调整连接所述v

bot

的电容控制开关,选择更高的电压值

[0110]

若所述比较器的输出信号为0,需要调整连接所述v

bot

的电容控制开关,选择更低的基准电压以对所述基准电压进行逐次逼近比较,选择一个适合于量化像素电压的电压段;

[0111]

步骤s4:根据比较器的结果,不断切换连接所述v

bot

的电容控制开关,以选择接不同的高m bit电阻电压缓冲器产生的基准电压,进行比较,以选择出适合于所量化的像素电压的v

bot

;

[0112]

步骤s5:在对所述高mbit的基准电压的比较结束后,选择出一个相应于任一偶数列采样得到的像素电压v

col

[n]的v

bot

,因控制连接到所述v

bot

与连接到所述v

top

的电容控制开关的偶控制信号的逻辑相同,此时有:相应于任一偶数列采样得到的像素电压v

col

[n]的v

top

也选择完毕;

[0113]

在确定一个相应于任一偶数列采样得到的像素电压v

col

[n]的一个v

bot

和一个v

top

后,进行低l bit的电容dac的逐次逼近比较量化。进行低l bit的电容dac的逐次逼近比较量化的方法包括:

[0114]

首先将最高位电容接v

top

,然后进行相应的比较,再根据比较器的输出结果,进而决定最高位电容控制开关接v

top

还是v

bot

。

[0115]

步骤s6:重复步骤s5,对于低l bit的电容dac的剩余位电容进行逐步逼近的量化,进而得到相应的码值。

[0116]

对于时序控制单元发送的奇偶开关的时序,可以参照图3所示的时序图,o分别表示第一、第二奇开关、e分别表示第一、第二偶开关的时序。此时,[1]~[16]分别表示cso《3:1》和cse《3:1》列译码所对应选通的奇数列或者偶数列。从[1]开始到[16]的整个过程,即为多列并行读出(multi column paraller readout)的过程,因为其它adc模块(例如17列~32列并用的adc、33~48列并用的adc

……

)也是相同的方法和时序。

[0117]

基于上述列级读出电路,本发明实施例还提供一种列级逐次逼近型模数转换器,所述列级逐次逼近型模数转换器包括如上任一所述的列级读出电路。

[0118]

基于上述列级读出电路,本发明实施例还提供一种红外成像仪,所述红外成像仪包括:光电流探测器以及如上任一所述的列级读出电路。

[0119]

通过上述实施例,本发明的列级读出电路,高m bit采用电阻dac形成高m bit电阻电压缓冲器,产生的基准电压为多个adc模块共用。而低l bit采用桥接电容的电容dac,每个adc模块内部仅保留低l bit的电容dac,其采用桥接电容dac。与同精度纯电容阵列sar adc相比,本发明所提列级读出电路,减小了电容阵列面积,并且由于采用了奇偶电容dac,变相的增加了对像素电压的采样时间,间接提升了量化转化的效率,减小了对于像素到列的电流需求,降低了功耗,具有较高的实用性。

[0120]

需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

[0121]

上面结合附图对本发明的实施例进行了描述,但是本发明并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本发明的启示下,在不脱离本发明宗旨和权利要求所保护的范围情况下,还可做出很多形式,这些均属于本发明的保护之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1