一种栅压自举开关电路

1.本发明属于集成电路技术领域,具体涉及一种栅压自举开关电路。

背景技术:

2.模数转换器(adc)在数模混合集成电路中起着十分重要的作用,是连接模拟信号和数字信号的纽带,所有的电路系统以及终端设备同自然界进行交互时必不可少的一部分,并且现如今,所有的电子产品都在往轻薄、便携以及可穿戴的方向发展,尤其是现在十分流行的一些植入式的用于治疗、监测疾病的生物芯片,对工作时长有着很高的要求,因而整个设备对电池续航要求较高,但是受到电池体积和容量的限制,只能通过降低芯片自身的功耗,以延长设备的工作时长。

3.采样保持电路作为模数转换器(adc)电路中最重要的模块之一,位于整个模数转换器电路的最前端,将模拟信号转换为采样信号,用于后级电路进行处理,因而采样保持电路的性能对于整个模数转换器电路的性能显得尤为显著。在采样保持电路中,采样开关导通电阻的非线性因素以及沟道电荷注入等对采样精度的影响十分显著,为了降低这些影响,栅压自举开关电路孕育而生。如图1所示,是传统的栅压自举开关电路通常包括两部分,分别是采样管m0和栅压自举电路t1,采样管m0通常是nmos管居多,采样管m0的源极接入输入信号vin,采样管m0的漏极产生输出信号vop,栅压自举电路t1的输入端1接入时钟信号clk,栅压自举电路t1的输入端2和输出端3分别连接至采样管m0的源极和栅极。

4.低功耗、高线性度的采样开关是高精度、低功耗模数转换器设计的一个关键。因此,需要设计一种具有更高采用速度和精度的栅压自举电路,以满足现有的工作场景需求。

技术实现要素:

5.本发明针对现有技术中缺少一种高速度和高精度采用的开关电路的技术问题,目的在于提供一种栅压自举开关电路。

6.一种栅压自举开关电路,包括一栅压自举电路、一采样管、输入端、输出端和时钟信号clk;

7.所述采样管采用晶体管m10;

8.所述栅压自举电路包括晶体管m1、m2、m3、m4、m5、m6、m8、m9、m11和m12,电容c1;

9.m1的栅极与m2的栅极相连接并连至所述时钟信号clk,m1的漏极与m2的漏极相连接并分别连至m5的栅极、m6的漏极,m3的漏极分别与m2的源极、c1的下极板、m6的源极,m8的源极、m9的漏极相连接,m3的栅极连至时钟信号clk的反相信号clkb,m4的漏极分别与c1的上极板、m5的源极相连接,m4的栅极分别与m5的漏极、m6的栅极、m8的栅极、m10的栅极、m11的源极相连接,m8的漏极与m9的源极相连接并连至m10的源极,m10的源极作为所述输入端,m10的漏极作为所述输出端,m11的漏极与m12的源极相连接,m12的栅极与m9的栅极相连接并连至所述时钟信号clk的反相信号clkb,m3的源极与m12的源极相连接并连至地电位,m1的源极、m4的源极与m11的栅极相连接并连至电源电位。

10.作为优选方案,所述晶体管m1、m4、m5和m9优选为n沟道绝缘栅双极晶体管,所述晶体管m2、m3、m6、m8、m11和m12优选为p沟道绝缘栅双极晶体管。

11.作为优选方案,所述栅压自举电路还包括晶体管m7,m7的栅极连至时钟信号clk,m7的源极连至地电位,m7的漏极与m1的漏极相连接。

12.作为优选方案,所述晶体管m7优选为p沟道绝缘栅双极晶体管。

13.本发明的积极进步效果在于:本发明采用栅压自举开关电路,通过对栅压自举电路的改进设计,特别是在栅压自举电路中增加了晶体管m9和/或晶体管m7,加快了栅压自举电路输入端的采样速度,从而使得与传统的栅压自举开关电路相比,本发明具有更高的采样速度和精度。

附图说明

14.图1为现有技术中栅压自举开关电路的一种电路图;

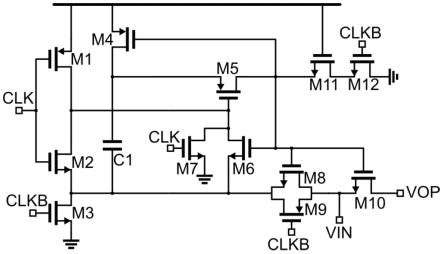

15.图2为本发明的一种电路图;

16.图3为本发明的另一种电路图;

17.图4为对比例1的一种电路图。

具体实施方式

18.为了使本发明实现的技术手段、创作特征、达成目的与功效易于明白了解,下面结合具体图示进一步阐述本发明。

19.参照图2和图3,一种栅压自举开关电路,包括一栅压自举电路、一采样用晶体管m10、输入端、输出端和时钟信号clk。其中,输入端接入输入信号vin,输出端产生输出信号vop,时钟信号clk的反相信号为clkb。

20.栅压自举电路包括晶体管m1、m2、m3、m4、m5、m6、m8、m9、m11和m12,电容c1。其中,m1的栅极与m2的栅极相连接并连至时钟信号clk,m1的漏极与m2的漏极相连接并分别连至m5的栅极、m6的漏极,m3的漏极分别与m2的源极、c1的下极板、m6的源极,m8的源极、m9的漏极相连接,m3的栅极连至时钟信号clk的反相信号clkb,m4的漏极分别与c1的上极板、m5的源极相连接,m4的栅极分别与m5的漏极、m6的栅极、m8的栅极、m10的栅极、m11的源极相连接,m8的漏极与m9的源极相连接并连至m10的源极,m10的源极作为输入端,m10的漏极作为输出端,m11的漏极与m12的源极相连接,m12的栅极与m9的栅极相连接并连至时钟信号clk的反相信号clkb,m3的源极与m12的源极相连接并连至地电位,m1的源极、m4的源极与m11的栅极相连接并连至电源电位。

21.在一些实施例中,晶体管m1、m4、m5和m9优选为n沟道绝缘栅双极晶体管,晶体管m2、m3、m6、m8、m11和m12优选为p沟道绝缘栅双极晶体管。若将上述晶体管反之设计,则需要微调整个电路即可。

22.在一些实施例中,参照图3,栅压自举电路还包括晶体管m7,m7的栅极连至时钟信号clk,m7的源极连至地电位,m7的漏极与m1的漏极相连接。

23.在一些实施例中,晶体管m7优选为p沟道绝缘栅双极晶体管。若将晶体管m7设计为n沟道绝缘栅双极晶体管,则需要微调整个电路即可。

24.本发明的栅压自举开关电路有两个工作状态,分别为保持状态和采样状态。当时

钟信号clk为低电平且clkb为高电平时,本发明的栅压自举开关电路处于保持状态。当时钟信号clk为高电平且clkb为低电平时,本发明的栅压自举开关电路处于采样状态,对输入端的输入信号vin进行采样。

25.当时钟信号clk为低电平且clkb为高电平时,本发明的栅压自举开关电路处于保持状态。晶体管m1、m3、m4、m11和m12导通,晶体管m2、m5、m6、m7、m8、m9和m10截止,导致电容c1的上极板被充电至电源电位,电容c1的下极板被复位至地电位。又由于晶体管m10截止,所以栅压自举开关电路的输出端产生的输出信号vop电压保持不变。

26.当时钟信号clk为高电平且clkb为低电平时,本发明的栅压自举开关电路处于采样状态。输入端输入的输入信号vin通过栅压自举开关电路进行采样。晶体管m1、m3、m4、m6、m11和m12截止,晶体管m2、m5、m7和m9导通,电容c1开始放电,并对m8的栅极和m9的栅极进行充电,导致m8和m9导通,因此该栅压自举开关电路的输出端产生的输出信号vop跟随输入端的输入信号vin变化,完成采样过程。

27.实施例1:

28.将本发明图2的栅压自举开关电路作为本发明例1,将本发明图3的栅压自举开关电路作为本发明例2,将图3中去除m7和m9后的图4作为对比例1。对本发明例1、本发明例2和对比例1均接入相同的输入信号vin,采用电路仿真的方法,进行采样速度和采样精度的比较。比较结果如下所示:

29.采样速度:本发明例2》本发明例1》对比例1;

30.采样精度:本发明例2》本发明例1》对比例1。

31.由上可知,本发明例1与对比例1相比,由于在栅压自举电路中增加了晶体管m9,大大加快了对输入信号vin的采样速度。

32.本发明例2与本发明例1相比,由于在栅压自举电路中增加晶体管m7,增加了电流通路,提高了信号采样速度。

33.本发明例2与对比例1相比,由于在栅压自举电路中增加晶体管m7和m9,增加了两处电流通路,大大提高了信号采样速度。

34.以上显示和描述了本发明的基本原理、主要特征和本发明的优点。本行业的技术人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中描述的只是说明本发明的原理,在不脱离本发明精神和范围的前提下,本发明还会有各种变化和改进,这些变化和改进都落入要求保护的本发明范围内。本发明要求保护范围由所附的权利要求书及其等效物界定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1