支持浮点系数的定点IIR滤波器和电子设备的制作方法

支持浮点系数的定点iir滤波器和电子设备

技术领域

1.本发明涉及数字信号处理领域,尤其涉及一种支持浮点系数的定点iir滤波器和电子设备。

背景技术:

2.在数字电路中,数字信号的滤波和反馈控制离不开滤波器,而由于iir(infinite impulse response,无限脉冲响应)滤波器既可以对信号进行低通、高通、带通、带阻滤波,还可以替代数字控制里的经典pid控制、零极点补偿控制,应用越来越广泛。但通常iir滤波器的滤波系数(分子系数和分母系数)的数据类型都是浮点型,这就要求iir滤波器能够支持浮点运算,而且对浮点运算处理能力有较高的要求;但是在实际的应用场景中会使用不支持浮点运算的iir滤波器,然而iir滤波器是不支持浮点系数。

技术实现要素:

3.本技术实施例提供了的iir滤波器和电子设备,可以解决相关技术中定点iir滤波器不支持浮点系数的问题。所述技术方案如下:

4.第一方面,本技术实施例提供了一种支持浮点系数的定点iir滤波器,包括:

5.数据输入端、分子缩放系数寄存器、分母缩放系数寄存器、反馈缩放系数寄存器、输出缩放系数寄存器、数据输出端、分子系数寄存器r0~分子系数寄存器rn、乘法器a0~乘法器an、乘法器b0~乘法器bn、加法器c0~加法器cn、延时器d0~延时器dn-1、乘法器e1~乘法器en、乘法器f1~乘法器fn、分母系数寄存器s1~分母系数寄存器sn、第一除法器m1、第二除法器m2、限幅器m2;n为大于1的整数;所述分子系数寄存器r0~分子系数寄存器rn分别用于存储浮点分子系数,所述分母系数寄存器s1~分母系数寄存器sn分别用于存储浮点分母系数;

6.其中,所述输入端分别与乘法器b0~乘法器bn的第一输入端相连;

7.所述分子缩放系数寄存器分别与乘法器a0~乘法器an的第一输入端相连;

8.所述分母缩放系数寄存器分别与乘法器f1~乘法器fn的第一输入端相连;

9.分子系数寄存器r0~分子系数寄存器rn与乘法器a0~乘法器an的第二输入端采用一对一的方式相连;

10.乘法器a0~乘法器an的输出端与乘法器b0~乘法器bn的第二输入端采用一对一的方式相连;

11.乘法器b0~乘法器bn的输出端与加法器c0~加法器cn的第一输入端采用一对一的方式相连;

12.延时器d0~延时器dn-1的输出端与加法器c0~加法器cn-1的第二输入端采用一对一的方式相连;

13.乘法器e1~乘法器en-1的输出端与加法器c1~加法器cn-1的第三输入端采用一对一的方式相连;

14.加法器c0的输出端与第一除法器m1的被除数端相连,第一除法器的除数端与反馈缩放系数寄存器相连,所述第一除法器的输出端与限幅器的输入端相连;所述限幅器的输出端与所述第二除法器的被输出端相连,且所述限幅器的输出端分别与乘法器e1~乘法器en的第一输入端相连;所述第二除法器的除数端与输出缩放系数寄存器相连,所述第二除法器的输出端与所述数据输出端相连;

15.加法器cn的第二输入端与乘法器en的输出端相连,加法器cn的输出端与延时器dn-1的输入端相连;

16.乘法器f1~乘法器fn的输出端与乘法器e1~乘法器en的第二输入端采用一对一的方式相连;

17.分母系数寄存器s1~分母系数寄存器sn与乘法器f1~乘法器fn的第一输入端采用一对一的方式相连。

18.第二方面,本技术提供了一种电子设备,包括:包括上述的iir滤波器。

19.本技术一些实施例提供的技术方案带来的有益效果至少包括:

20.在现有的定点iir滤波器的结构的基础上,增加分子缩放系数寄存器、分母缩放系数寄存器、反馈缩放系数寄存器、输出缩放系数寄存器、乘法器a0~乘法器an、乘法器f1~乘法器fn、第一除法器m1、第二除法器m2、限幅器m2,通过对浮点系数的缩放实现在定点iir滤波器中实现利用浮点系数进行iir滤波,具有运算速度快耗时短等优点,相对于浮点iir滤波器不会降低运算速度,也能利用现有的定点iir滤波器进行兼容设计,减少硬件成本和设计成本。

附图说明

21.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

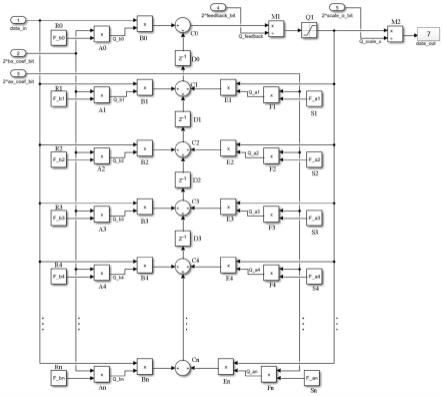

22.图1是本发明实施例提供的n阶iir滤波器的结构示意图;

23.图2是本发明实施例提供的4阶iir滤波器的结构图;

24.图3是本发明实施例提供的数值区间的分布示意图。

具体实施方式

25.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

26.请参阅图1,本发明提供实施例的一种iir滤波器的结构示意图,iir滤波器包括:。

27.数据输入端1、分子缩放系数寄存器2、分母缩放系数寄存器3、反馈缩放系数寄存器4、输出缩放系数寄存器5、数据输出端6、分子系数寄存器r0~分子系数寄存器rn、乘法器a0~乘法器an、乘法器b0~乘法器bn、加法器c0~加法器cn、延时器d0~延时器dn-1、乘法器e1~乘法器en、乘法器f1~乘法器fn、分母系数寄存器s1~分母系数寄存器sn、第一除法

器m1、第二除法器m2、限幅器m2;n为大于1的整数。

28.乘法器用于执行乘法运算,加法器用于执行加法运算,寄存器用于存储相关数据,除法器用于执行触发运算,延时器用于执行延时处理,即暂存上一次数据,限幅器用于限制输出数据的数值范围。上述的各个器件均为数字器件。

29.其中,iir滤波器可以采用数字信号处理(digital signal processing,dsp)、现场可编程门阵列(field-programmable gatearray,fpga)、可编程逻辑阵列(programmable logicarray,pla)中的至少一种硬件形式来实现。

30.iir滤波器包括的各个部件的连接关系为:

31.乘法器b0~乘法器bn共计有n+1个乘法器,每个乘法器设置有第一输入端、第二输入端和输出端。本技术的数据输入端分别与乘法器b0~乘法器bn的第一输入端相连。

32.分子缩放系数寄存器用于存放第一缩放系数,分子缩放系数寄存器分别与乘法器a0~乘法器an的第一输入端相连。

33.分母缩放系数寄存器用于存放第二缩放系数,分母缩放系数寄存器分别与乘法器f1~乘法器fn的第一输入端相连,

34.分子系数寄存器r0~分子系数寄存器rn与乘法器a0~乘法器an的第二输入端采用一对一的方式相连,分子系数寄存器r0~分子系数寄存器rn分别用于存储浮点分子系数:f_b0~f_bn,分子系数寄存器r0与乘法器a0的第二输入端相连、分子系数寄存器r1与乘法器a1的第二输入端相连、

…

、分子系数寄存器rn与乘法器an的第二输入端相连。

35.乘法器a0~乘法器an的输出端与乘法器b0~乘法器bn的第二输入端采用一对一的方式相连,即乘法器a0的输出端与乘法器b0的第二输入端相连、乘法器a1的输出端与乘法器b1的第二输入端相连、

…

、乘法器an的输出端与乘法器bn的第二输入端相连。

36.乘法器b0~乘法器bn的输出端与加法器c0~加法器cn的第一输入端采用一对一的方式相连,即乘法器b0的输出端和加法器c0的第一输入端相连、乘法器b1的输出端和加法器c1的第一输入端相连、

…

、乘法器bn的输出端和加法器bn的第一输入端相连。

37.延时器d0~延时器dn-1的输出端与加法器c0~加法器cn-1的第二输入端采用一对一的方式相连,即延时器d0的输出端与加法器c0的第二输入端相连、延时器d1的输出端与加法器c1的第二输入端相连、

…

、延时器dn-1的输出端与加法器cn-1的第二输入端相连。

38.乘法器e1~乘法器en-1的输出端与加法器c1~加法器cn-1的第三输入端采用一对一的方式相连。

39.加法器c0的输出端与第一除法器m1的被除数端相连,第一除法器的除数端与反馈缩放系数寄存器相连,第一除法器的输出端与限幅器的输入端相连;限幅器的输出端与第二除法器的被输出端相连,且限幅器的输出端分别与乘法器e1~乘法器en的第一输入端相连;第二除法器的除数端与输出缩放系数寄存器相连,第二除法器的输出端与数据输出端相连。

40.加法器cn的第二输入端与乘法器en的输出端相连,加法器cn的输出端与延时器dn-1的输入端相连。

41.乘法器f1~乘法器fn的输出端与乘法器e1~乘法器en的第二输入端采用一对一的方式相连,分母系数寄存器s1~分母系数寄存器sn与乘法器f1~乘法器fn的第一输入端采用一对一的方式相连,分母系数寄存器s1~sn分别用于存储浮点分母系数:f_a1~f_an。

42.本技术的iir滤波器的工作过程包括:

43.根据n阶iir滤波器的性能指标生成浮点分子系数f_b0~f_bn和浮点分母系数f_a1~f_an,例如:根据低通滤波、高通滤波、带通滤波或带阻滤波的性能指标,调用matlable的fdatool工具生成上述的浮点分母系数和浮点分子系数,浮点分母系数属于n阶iir滤波器的传输函数的分母,浮点分子系数属于n阶iir滤波器的传输函数的分子。浮点分子系数和浮点分母系数的数据类型为浮点型。处理器将生成的浮点分子系数f_b0~f_bn分别写入到分子系数寄存器r0~rn中,以及将生成的浮点分母系数f_a1~f_an分别写入到分母系数寄存器s1~sn中。其中,浮点分母系数f_a0=1。

44.然后,在数据输入端1输入待处理数据。利用乘法器a0~an,将分子缩放系数寄存器2中存储分子缩放系数2

bx_coef_bit

的分别与浮点分子系数f_b0~f_bn进行相乘得到定点分子系数:q_b0~q_bn。以及利用乘法器f1~fn,将分母缩放系数寄存器3中存储的2

ax_coef_bit

分别与浮点分母系数f_a1~f_an进行相乘得到定点分母系数f_a1~f_an。定点分子系数和定点分母系数的数据类型为定点型。

45.对于加法器c0的输出结果,第一除法器m1将该输出结果除以反馈缩放系数寄存器4中存放的反馈缩放系数2

feedback_bit

得到商值,然后利用限幅器q1对该商值进行限幅处理,第二除法器m2将限幅处理后的结果除以输出缩放系数寄存器5中存储的输出缩放系数2

fscale_o_bit

得到iir滤波器的输出数据,通过数据输出端7输出该输出数据。

46.举例来说,参见图2所示的iir滤波器的结构示意图,n=4,图3中的iir寄存器省略了分子系数寄存器r0~r4、乘法器a0~a4、乘法器f1~f4、分母系数寄存器s1~s4。数据输入端输入16bit的待处理数据,生成的5个定点分子系数为f_b0~f_b4,4个定点分母系数为f_a1~f_a4,上述系数均为16bit。然后再加法器c0输出60bit的输出结果,第一除法器m1将该输出结果除以反馈缩放系数寄存器4中存放的反馈缩放系数q_feedback得到商值,然后利用限幅器q1对该商值进行限幅处理,第二除法器m2将限幅处理后的结果除以输出缩放系数寄存器5中存储的输出缩放系数q_scaleo得到iir滤波器的输出数据,通过数据输出端7输出该24bit的输出数据,实现iir滤波器的定点运算。

47.进一步的,本技术实施例中,处理器还可以根据不同需求,在多个系数集中为iir滤波器选择对应的系数集,然后将系数集中的各个系数配置到iir滤波器中,以适应不同运算场景。各个系数集包括分子缩放系数、分母缩放系数、n+1浮点分子系数、n个浮点分母系数、反馈缩放系数和输出缩放系数。

48.可选的,选择的系数集与输入的待处理数据的大小有关,在iir滤波器处理该待处理数据之前,确定待处理数据所在的数值区间,然后查询该数值区间在多个系数集中对应的目标系数集,将目标系数集配置到iir滤波器中的寄存器中。

49.例如:参见图3所示的数值区间分布示意图,本技术预配置有4个系数集:g0、g1、g2、g3,当|din|>l3,选择系数集g3对iir滤波器进行配置;当|din|∈[l2,l23],选择系数集g2对iir滤波器进行配置;当|din|∈[l1,l12],选择系数集g1对iir滤波器进行配置;当|din|∈[0,l0],选择系数集g0对iir滤波器进行配置。其中,l3》l2》l1》l0。

[0050]

进一步的,l12和l23根据如下的任意一种公式来确定:

[0051]

或或其中,k和a为常数,1<k<10,0<a<k。

[0052]

本技术实施例的硬件架构,在现有的定点iir滤波器的结构的基础上,增加分子缩放系数寄存器、分母缩放系数寄存器、反馈缩放系数寄存器、输出缩放系数寄存器、乘法器a0~乘法器an、乘法器f1~乘法器fn、第一除法器m1、第二除法器m2、限幅器m2,通过对浮点系数的缩放实现在定点iir滤波器中实现利用浮点系数进行iir滤波,具有运算速度快耗时短等优点,相对于浮点iir滤波器不会降低运算速度,也能利用现有的定点iir滤波器进行兼容设计,减少硬件成本和设计成本。

[0053]

本技术实施例提供的电子设备除包括上述的控制装置之外,还可以包括:用于容纳各个部件的壳体。

[0054]

以上所述的实施方式,并不构成对该技术方案保护范围的限定。任何在上述实施方式的精神和原则之内所作的修改、等同替换和改进等,均应包含在该技术方案的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1