合路器电路及电子设备的制作方法

本申请涉及合路器电路,具体而言,涉及一种合路器电路及电子设备。

背景技术:

1、如图1所示,一个三路doherty放大器包含一个主放大器m和两个峰值放大器(第一峰值放大器p1和第二峰值放大器p2)。此外,它还包含一个双节合路器(q1和q2),一个输出匹配网络u4,一个移相网络(u2和u3)。待放大的射频输入信号分成三路后分别用于主放大器m和第一峰值放大器p1和第二峰值放大器p2。doherty合路器2用于在合路点合成被主放大器和峰值放大器分别放大的信号。合成之后的信号通过一个输出匹配网络u4传输到负载rl。移相网络(u2和u3)放在第一峰值放大器p1和第二峰值放大器p2之前,以保证在合路点(即第二峰值放大器p2、输出匹配网络u4和q2的交接点)三路放大器输出信号的相位是对齐的,其中u1为功率分配器。

2、在mmic电路设计中,尤其是硅基电路,电路通常采用集总元件来实现,即电感l/电容c/电阻r,而非传输线。5g场景下普遍使用数字预失真技术对功率放大器进行线性化。初始的信号带宽已经超过200mhz,经过数字预失真的实际信号带宽通常是初始信号的三倍,可以很轻易的超过600mhz,这对功率放大器的数字预失真友好度提出了很高的挑战。良好的数字预失真友好度需要合适的基带阻抗匹配。现有方案在射频能够实现很好的效果,但是并未着重考虑基带的阻抗匹配,不利于宽带调制信号的数字预失真校正。

技术实现思路

1、本申请的主要目的在于提供一种合路器电路及电子设备,以解决如何改善基带阻抗匹配以提升其数字预失真友好度的问题。

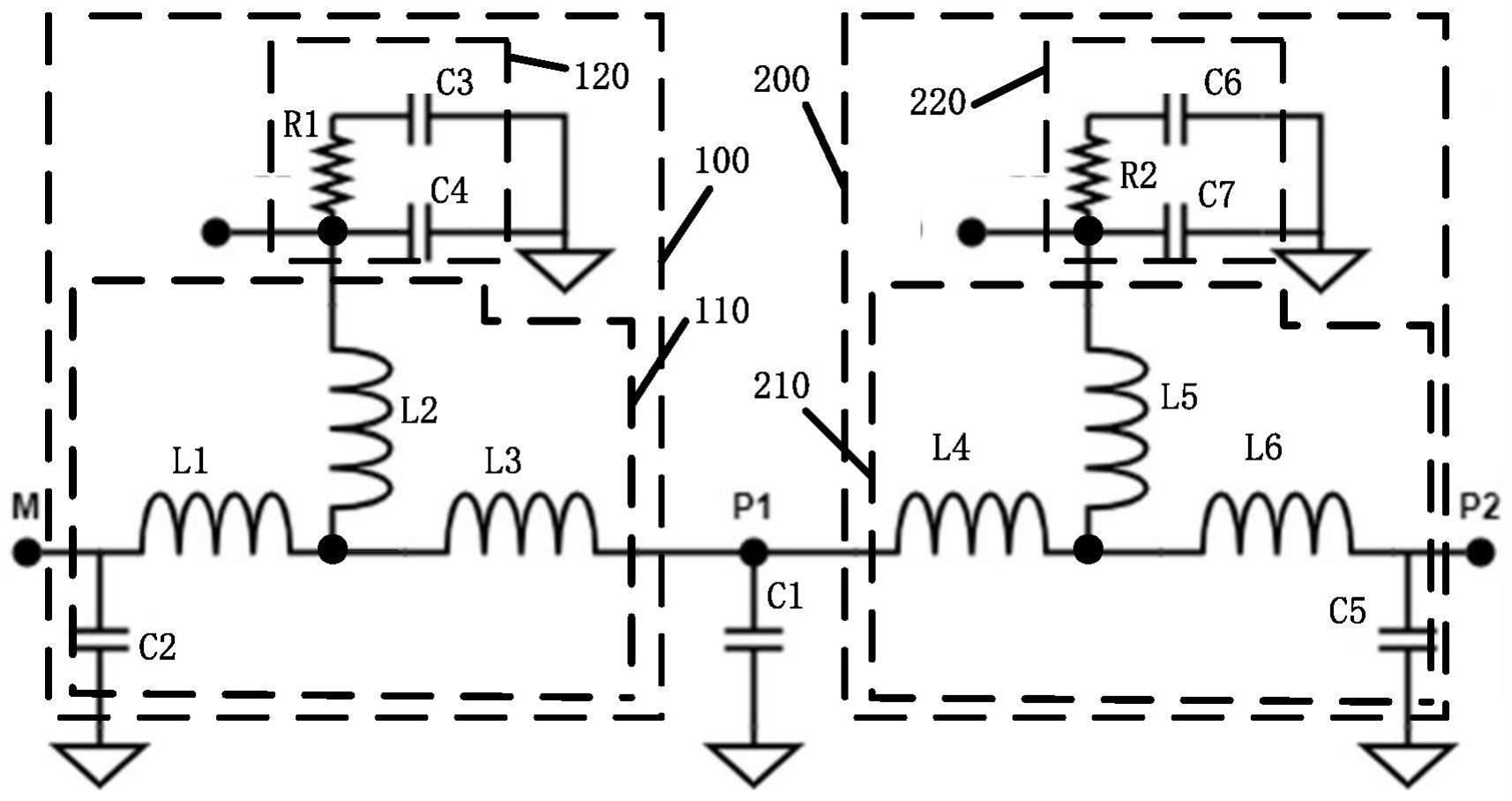

2、根据本发明实施例的一个方面,提供了一种合路器电路,合路器电路包括第一电容模块、第一合路模组和第二合路模组;第一合路模组具有第一端和第二端,所述第一合路模组的第一端用于与主放大器电连接,所述第一合路模组的第二端与所述第一电容模块电连接,所述第一合路模组的第二端还用于与第一峰值放大器电连接,所述第一合路模组用于将所述主放大器输出的信号与所述第一峰值放大器输出的信号进行合路,得到第一合路信号;第二合路模组具有第一端和第二端,所述第二合路模组的第一端与所述第一电容模块电连接,所述第二合路模组的第一端还用于与所述第一峰值放大器电连接,所述第二合路模组的第二端用于与第二峰值放大器电连接,所述第二合路模组用于将所述第一合路信号和所述第二峰值放大器输出的信号进行合路,得到第二合路信号。

3、可选地,所述第一合路模组包括第一合路电路和第一电压隔直电路,所述第一合路电路具有第一端、第二端和第三端,所述第一合路电路的第一端作为所述第一合路模组的第一端,所述第一合路电路的第二端作为所述第一合路模组的第二端,所述第一合路电路的第三端与所述第一电压隔直电路电连接。

4、可选地,所述第一合路电路包括第一电感模块、第二电感模块、第三电感模块和第二电容模块,所述第一电感模块的第一端作为所述第一合路电路的第一端,所述第一电感模块的第一端还与所述第二电容模块的第一端电连接,所述第一电感模块的第二端分别与所述第二电感模块的第一端和所述第三电感模块的第一端电连接,所述第二电感模块的第二端作为所述第一合路电路的第三端,所述第三电感模块的第二端作为所述第一合路电路的第二端,所述第二电容模块的第二端接地。

5、可选地,所述第一电压隔直电路包括第三电容模块和第四电容模块,所述第三电容模块的第一端分别与所述第四电容模块的第一端和所述第一合路电路的第三端电连接,所述第三电容模块的第一端还用于与电压源电连接,所述第三电容模块的第二端和所述第四电容模块的第二端分别接地。

6、可选地,所述第一电压隔直电路还包括第一电阻模块,所述第一电阻模块的第一端与所述第三电容模块的第一端电连接,所述第一电阻模块的第二端与所述第四电容模块的第一端电连接。

7、可选地,所述第二合路模组包括第二合路电路和第二电压隔直电路,所述第二合路电路具有第一端、第二端和第三端,所述第二合路电路的第一端作为所述第二合路模组的第一端,所述第二合路电路的第二端作为所述第二合路模组的第二端,所述第二合路电路的第三端与所述第二电压隔直电路电连接。

8、可选地,所述第二合路电路包括第四电感模块、第五电感模块、第六电感模块和第五电容模块,所述第四电感模块的第一端作为所述第二合路电路的第一端,所述第四电感模块的第二端分别与所述第五电感模块的第一端和所述第六电感模块的第一端电连接,所述第五电感模块的第二端作为所述第二合路电路的第三端,所述第六电感模块的第二端作为所述第二合路电路的第二端,所述第六电感模块的第二端与所述第五电容模块的第一端电连接,所述第五电容模块的第二端接地。

9、可选地,所述第二电压隔直电路包括第六电容模块和第七电容模块,所述第六电容模块的第一端分别与所述第七电容模块的第一端和所述第二合路电路的第三端电连接,所述第六电容模块的第一端还用于与电压源电连接,所述第六电容模块的第二端和所述第七电容模块的第二端分别接地。

10、可选地,所述第二电压隔直电路还包括第二电阻模块,所述第二电阻模块的第一端与所述第六电容模块的第一端电连接,所述第二电阻模块的第二端与所述第七电容模块的第一端电连接。

11、根据本发明实施例的另一方面,还提供了一种电子装置,电子装置包括任意一种所述的合路器电路、主放大器、第一峰值放大器和第二峰值放大器,所述合路器电路分别与所述主放大器、所述第一峰值放大器和所述第二峰值放大器电连接。

12、在本发明实施例中,优化常规三路doherty mmic放大器的拓扑结构,在不影响射频匹配的前提下,改善基带阻抗匹配,从而提升其数字预失真友好度,更好的适应5g的大带宽信号场景,进而解决了如何改善基带阻抗匹配以提升其数字预失真友好度的问题。

技术特征:

1.一种合路器电路,其特征在于,包括:

2.根据权利要求1所述的合路器电路,其特征在于,所述第一合路模组包括第一合路电路和第一电压隔直电路,所述第一合路电路具有第一端、第二端和第三端,所述第一合路电路的第一端作为所述第一合路模组的第一端,所述第一合路电路的第二端作为所述第一合路模组的第二端,所述第一合路电路的第三端与所述第一电压隔直电路电连接。

3.根据权利要求2所述的合路器电路,其特征在于,所述第一合路电路包括第一电感模块、第二电感模块、第三电感模块和第二电容模块,所述第一电感模块的第一端作为所述第一合路电路的第一端,所述第一电感模块的第一端还与所述第二电容模块的第一端电连接,所述第一电感模块的第二端分别与所述第二电感模块的第一端和所述第三电感模块的第一端电连接,所述第二电感模块的第二端作为所述第一合路电路的第三端,所述第三电感模块的第二端作为所述第一合路电路的第二端,所述第二电容模块的第二端接地。

4.根据权利要求2所述的合路器电路,其特征在于,所述第一电压隔直电路包括第三电容模块和第四电容模块,所述第三电容模块的第一端分别与所述第四电容模块的第一端和所述第一合路电路的第三端电连接,所述第三电容模块的第一端还用于与电压源电连接,所述第三电容模块的第二端和所述第四电容模块的第二端分别接地。

5.根据权利要求4所述的合路器电路,其特征在于,所述第一电压隔直电路还包括第一电阻模块,所述第一电阻模块的第一端与所述第三电容模块的第一端电连接,所述第一电阻模块的第二端与所述第四电容模块的第一端电连接。

6.根据权利要求1所述的合路器电路,其特征在于,所述第二合路模组包括第二合路电路和第二电压隔直电路,所述第二合路电路具有第一端、第二端和第三端,所述第二合路电路的第一端作为所述第二合路模组的第一端,所述第二合路电路的第二端作为所述第二合路模组的第二端,所述第二合路电路的第三端与所述第二电压隔直电路电连接。

7.根据权利要求6所述的合路器电路,其特征在于,所述第二合路电路包括第四电感模块、第五电感模块、第六电感模块和第五电容模块,所述第四电感模块的第一端作为所述第二合路电路的第一端,所述第四电感模块的第二端分别与所述第五电感模块的第一端和所述第六电感模块的第一端电连接,所述第五电感模块的第二端作为所述第二合路电路的第三端,所述第六电感模块的第二端作为所述第二合路电路的第二端,所述第六电感模块的第二端与所述第五电容模块的第一端电连接,所述第五电容模块的第二端接地。

8.根据权利要求6所述的合路器电路,其特征在于,所述第二电压隔直电路包括第六电容模块和第七电容模块,所述第六电容模块的第一端分别与所述第七电容模块的第一端和所述第二合路电路的第三端电连接,所述第六电容模块的第一端还用于与电压源电连接,所述第六电容模块的第二端和所述第七电容模块的第二端分别接地。

9.根据权利要求8所述的合路器电路,其特征在于,所述第二电压隔直电路还包括第二电阻模块,所述第二电阻模块的第一端与所述第六电容模块的第一端电连接,所述第二电阻模块的第二端与所述第七电容模块的第一端电连接。

10.一种电子装置,其特征在于,包括权利要求1至9中任一项所述的合路器电路、主放大器、第一峰值放大器和第二峰值放大器,所述合路器电路分别与所述主放大器、所述第一峰值放大器和所述第二峰值放大器电连接。

技术总结

本申请提供了一种合路器电路及电子设备,合路器电路包括第一电容模块、第一合路模组和第二合路模组;第一合路模组用于将主放大器输出的信号与第一峰值放大器输出的信号进行合路,得到第一合路信号;第二合路模组用于将第一合路信号和第二峰值放大器输出的信号进行合路,得到第二合路信号。优化常规三路Doherty MMIC放大器的拓扑结构,在不影响射频匹配的前提下,改善基带阻抗匹配,从而提升其数字预失真友好度,更好的适应5G的大带宽信号场景,进而解决了如何改善基带阻抗匹配以提升其数字预失真友好度的问题。

技术研发人员:杨梦苏,林良,刘昊宇

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!