形成半导体结构的方法与流程

本揭露内容是有关于一种形成半导体结构的方法。

背景技术:

1、电容器可以被用于各种不同的半导体电路中。举例来说,电容器可被用于动态随机存取存储器(dynamic random access memory;dram)的存储器电路或任何其他类型的存储器电路中。dram存储器电路可通过在单个半导体晶圆上复制数百万个相同的电路元件(称为dram单元)来制造。dram单元是一个可寻址的位置,其可以存储数据的位元(二进制位)。在dram单元常见的形式,可包括两个电路元件:一个存储电容器(storage capacitor)与一个访问场效应晶体管(access field effect transistor)。

技术实现思路

1、本揭露的技术态样为一种形成半导体结构的方法。

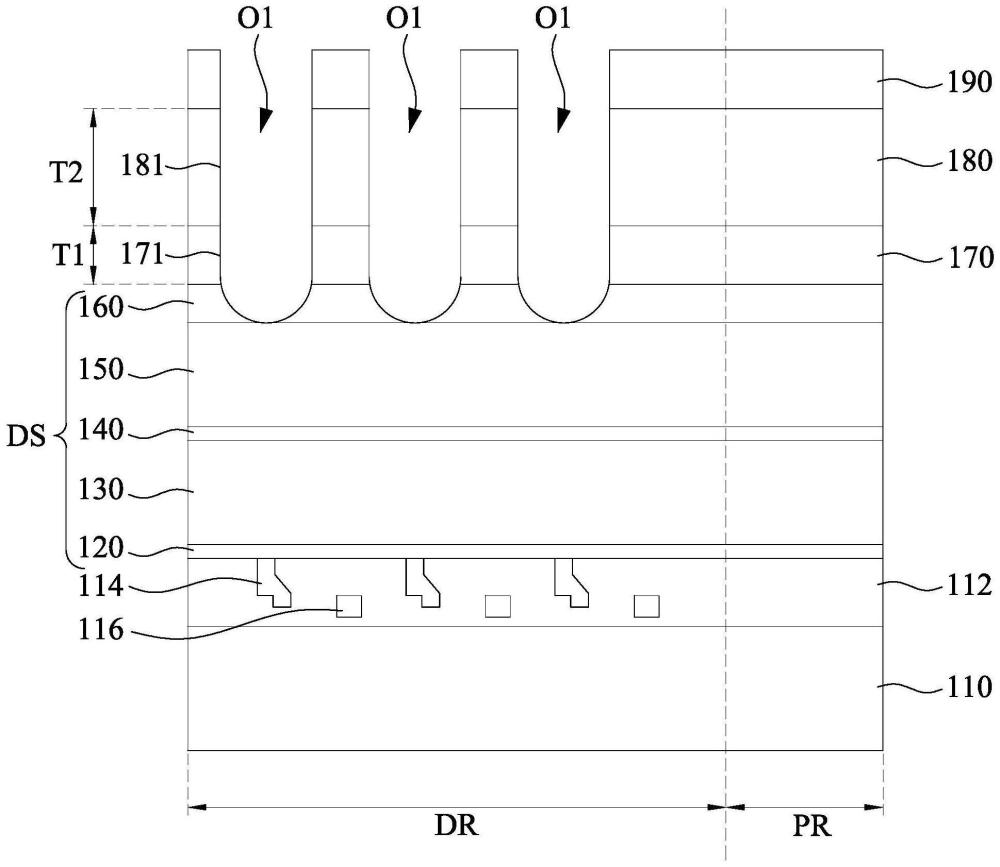

2、根据本揭露一些实施方式,一种形成半导体结构的方法,包括形成介电堆叠于基板上,其中形成介电堆叠包括依序形成的第一支撑层、第一牺牲层、第二支撑层、第二牺牲层及第三支撑层。形成第一硬遮罩层于介电堆叠上。形成第二硬遮罩层于第一硬遮罩层上。使用图案化遮罩作为蚀刻遮罩,蚀刻第一硬遮罩层与第二硬遮罩层以形成第一硬遮罩与第二硬遮罩,其中第一硬遮罩层比第二硬遮罩层更快地蚀刻。形成开口于介电堆叠中,以暴露基板。形成下电极层于介电堆叠的开口中。

3、在本揭露一些实施方式中,形成半导体结构的方法还包括在蚀刻第一硬遮罩层与第二硬遮罩层之后,蚀刻介电堆叠的第三支撑层。

4、在本揭露一些实施方式中,蚀刻介电堆叠的第三支撑层使得介电堆叠的第二牺牲层被暴露。

5、在本揭露一些实施方式中,蚀刻第一硬遮罩层与第二硬遮罩层使得第一硬遮罩具有第一暴露侧壁且第二硬遮罩具有第二暴露侧壁,第二暴露侧壁的斜率相同于第一暴露侧壁的斜率。

6、在本揭露一些实施方式中,第一硬遮罩层与第二硬遮罩层包括半导体材料。

7、在本揭露一些实施方式中,第一硬遮罩层包括具有第一导电类型的第一掺杂剂,且第二硬遮罩层包括具有不同于第一导电类型的第二导电类型的第二掺杂剂。

8、在本揭露一些实施方式中,第一硬遮罩层具有第一厚度,第二硬遮罩层具有第二厚度,且第二厚度大于第一厚度。

9、在本揭露一些实施方式中,形成半导体结构的方法还包括在形成开口之前,移除图案化遮罩。

10、在本揭露一些实施方式中,形成半导体结构的方法还包括在形成开口之前,移除第二硬遮罩。

11、在本揭露一些实施方式中,形成半导体结构的方法还包括形成高介电常数介电层沿着下电极层的侧壁。形成上电极层沿着高介电常数介电层的侧壁,以定义包括在介电堆叠中的下电极层、高介电常数介电层及上电极层的电容器。

12、本揭露的技术态样为一种形成半导体结构的方法。

13、根据本揭露一些实施方式,一种形成半导体结构的方法,包括形成介电堆叠于基板上。形成第一硬遮罩与第二硬遮罩于介电堆叠上,其中第一硬遮罩包括具有第一导电类型的第一掺杂剂,且第二硬遮罩包括具有不同于第一导电类型的第二导电类型的第二掺杂剂。使用第一硬遮罩作为蚀刻遮罩,形成介电堆叠中的开口以暴露基板。形成下电极层于介电堆叠的开口中。

14、在本揭露一些实施方式中,形成第一硬遮罩与第二硬遮罩使得第一硬遮罩接触介电堆叠,且第二硬遮罩接触第一硬遮罩。

15、在本揭露一些实施方式中,第一硬遮罩与第二硬遮罩包括多晶硅材料。

16、在本揭露一些实施方式中,第一掺杂剂的掺杂浓度在0.5%至1.5%的范围间,且第二掺杂剂的掺杂浓度在0.5%至1.5%的范围间。

17、在本揭露一些实施方式中,第一硬遮罩具有第一厚度,第二硬遮罩具有第二厚度,且第二厚度大于第一厚度。

18、在本揭露一些实施方式中,形成半导体结构的方法还包括在形成介电堆叠中的开口之前,移除第一硬遮罩。

19、在本揭露一些实施方式中,形成介电堆叠包括形成第一牺牲层于基板上。形成第二牺牲层于第一牺牲层上。

20、在本揭露一些实施方式中,形成介电堆叠还包括形成第一支撑层于基板上。形成第二支撑层于第一牺牲层上。形成第三支撑层于第二牺牲层上。

21、在本揭露一些实施方式中,形成半导体结构的方法还包括在形成下电极层之后,移除第二牺牲层。移除第一牺牲层,以暴露第一支撑层。

22、在本揭露一些实施方式中,形成半导体结构的方法还包括形成高介电常数介电层沿着下电极层的侧壁。形成上电极层沿着高介电常数介电层的侧壁,以定义包括在介电堆叠中的下电极层、高介电常数介电层及上电极层的电容器。

23、根据本揭露上述实施方式,由于第一硬遮罩层比第二硬遮罩层更快地蚀刻,可改善第一硬遮罩的轮廓。如此一来,可以改善后续蚀刻与沉积工艺中形成的电容器的轮廓,避免电容器的电容降低。

24、应当了解前面的一般说明和以下的详细说明都仅是示例,并且旨在提供对本揭露的进一步解释。

技术特征:

1.一种形成半导体结构的方法,其特征在于,包含:

2.根据权利要求1所述的方法,其中还包含:

3.根据权利要求2所述的方法,其中蚀刻该介电堆叠的该第三支撑层使得该介电堆叠的该第二牺牲层被暴露。

4.根据权利要求1所述的方法,其中蚀刻该第一硬遮罩层与该第二硬遮罩层使得该第一硬遮罩具有第一暴露侧壁且该第二硬遮罩具有第二暴露侧壁,该第二暴露侧壁的斜率相同于该第一暴露侧壁的斜率。

5.根据权利要求1所述的方法,其中该第一硬遮罩层与该第二硬遮罩层包含半导体材料。

6.根据权利要求1所述的方法,其中该第一硬遮罩层包含具有第一导电类型的第一掺杂剂,且该第二硬遮罩层包含具有不同于该第一导电类型的第二导电类型的第二掺杂剂。

7.根据权利要求1所述的方法,其中该第一硬遮罩层具有第一厚度,该第二硬遮罩层具有第二厚度,且该第二厚度大于该第一厚度。

8.根据权利要求1所述的方法,其中还包含:

9.根据权利要求1所述的方法,其中还包含:

10.根据权利要求1所述的方法,其中还包含:

11.一种形成半导体结构的方法,其特征在于,包含:

12.根据权利要求11所述的方法,其中形成该第一硬遮罩与该第二硬遮罩使得该第一硬遮罩接触该介电堆叠,且该第二硬遮罩接触该第一硬遮罩。

13.根据权利要求11所述的方法,其中该第一硬遮罩与该第二硬遮罩包含多晶硅材料。

14.根据权利要求11所述的方法,其中该些第一掺杂剂的掺杂浓度在0.5%至1.5%的范围间,且该些第二掺杂剂的掺杂浓度在0.5%至1.5%的范围间。

15.根据权利要求11所述的方法,其中该第一硬遮罩具有第一厚度,该第二硬遮罩具有第二厚度,且该第二厚度大于该第一厚度。

16.根据权利要求11所述的方法,其中还包含:

17.根据权利要求11所述的方法,其中形成该介电堆叠包含:

18.根据权利要求17所述的方法,其中形成该介电堆叠还包含:

19.根据权利要求18所述的方法,其中还包含:

20.根据权利要求11所述的方法,其中还包含:

技术总结

本揭露提供一种形成半导体结构的方法,包括形成介电堆叠于基板上,其中形成介电堆叠包括依序形成的第一支撑层、第一牺牲层、第二支撑层、第二牺牲层及第三支撑层。形成第一硬遮罩层于介电堆叠上。形成第二硬遮罩层于第一硬遮罩层上。使用图案化遮罩作为蚀刻遮罩,蚀刻第一硬遮罩层与第二硬遮罩层以形成第一硬遮罩与第二硬遮罩,其中第一硬遮罩层比第二硬遮罩层更快地蚀刻。形成开口于介电堆叠中,以暴露基板。形成下电极层于介电堆叠的开口中。借此,可改善第一硬遮罩的轮廓,且因此可以改善后续蚀刻与沉积工艺中形成的电容器的轮廓,避免电容器的电容降低。

技术研发人员:林雅琴

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!