上电复位电路、欠压锁定电路及欠压锁定方法与流程

本发明属于电源电路,特别是关于一种上电复位电路、欠压锁定电路及欠压锁定方法。

背景技术:

1、在一些应用中,要求在不同上电速度、输出随电源单调变化。输出通常受欠压锁定电路(under voltage lock out,uvlo)控制,这就要求在不同上电速度时,uvlo只拉高一次。

2、在uvlo电路中,常规的上电复位电路(power-on reset,por)一般是采用nmos管与输入电阻相连以对电源电压vdd分压,然后通过一组反相器对信号进行反转后输出上电复位信号至uvlo电路的比较器。在por电路拉高后,比较器开始正常工作,比较器的正向输入端输入基准电压vref,反向输入端输入带隙基准电路(bandgap)产生的带隙基准电压vbg,当基准电压vref高于带隙基准电压vbg时,uvlo电路输出高电平;当基准电压vref低于带隙基准电压vbg时,uvlo电路输出低电平。

3、然而,当uvlo电路翻转电压较低时,por电路的设计比较受限。por电路通常和mos管的阈值电压vth相关,vth受温度和corner影响较大,por电路在低温ss corner时翻转点很高,在高温ff corner时翻转点比较低。一方面,在低温ss corner时,por电路的翻转电压不能超过uvlo电路的翻转电压值,而常规的por电路的翻转电压大约为2vth,对于uvlo电路翻转电压较低的场景,在低温ss corner时面临较大的挑战,需要进一步降低por电路的翻转电压。另一方面,如图1a、1b所示,在高温ff corner时,由于por电路的翻转电压过低,导致uvlo电路有多次翻转的问题。

4、公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

1、本发明的目的在于提供一种上电复位电路、欠压锁定电路及欠压锁定方法,其用以解决欠压锁定电路翻转电压较低的情况下,高温ff corner时上电复位电路的翻转电压过低导致欠压锁定电路有多次翻转的问题。

2、为实现上述目的,本发明的实施例提供了一种上电复位电路,所述上电复位电路包括:

3、第一分压单元,电性连接于电源电压vdd和地电位之间,所述第一分压单元于第一分压节点上输出分压电压va;

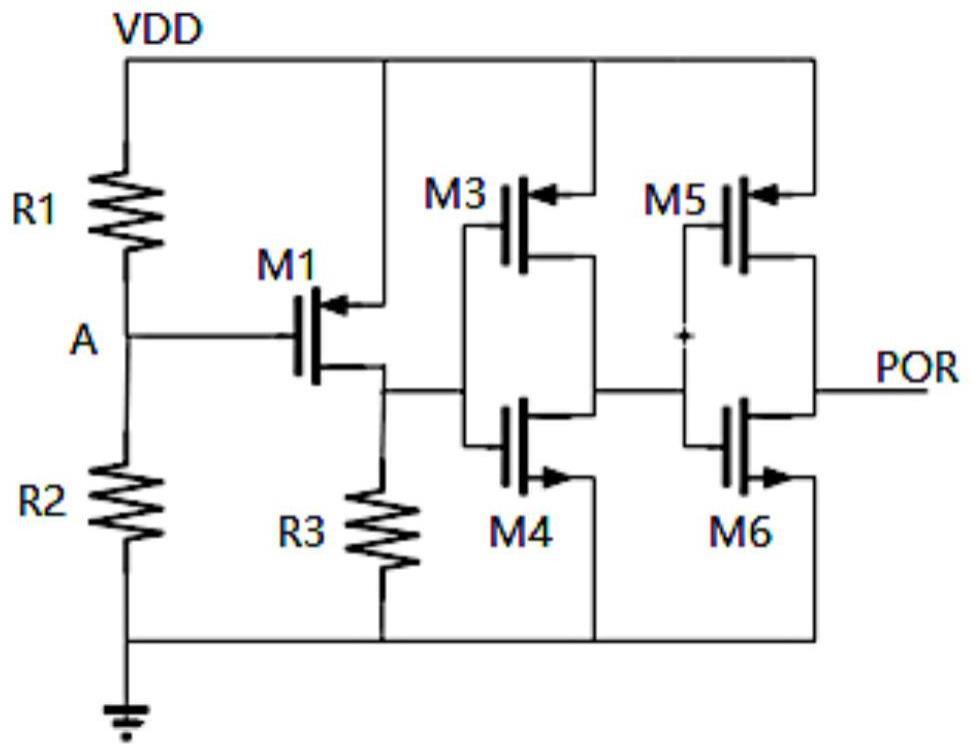

4、第一mos管,所述第一mos管的栅极与第一分压节点相连,源极与电源电压vdd相连,漏极间接与地电位相连,所述上电复位电路的输出端与第一mos管的漏极直接或间接相连,以输出上电复位信号;

5、其中,所述上电复位信号的翻转点电压vl2h为vl2h=k*vth,k>1,vth为第一mos管的阈值电压。

6、在本发明的一个或多个实施方式中,所述第一分压单元包括电性连接于电源电压vdd与第一分压节点之间的第一电阻、及电性连接于第一分压节点和地电位之间的第二电阻。

7、在本发明的一个或多个实施方式中,所述上电复位信号的翻转点电压vl2h<2vgs,vgs为第一mos管的栅源电压。

8、在本发明的一个或多个实施方式中,所述第一mos管为pmos管。

9、在本发明的一个或多个实施方式中,所述第一mos管的漏极与地电位之间连接有第三电阻或电流源。

10、在本发明的一个或多个实施方式中,所述上电复位电路的输出端与第一mos管的漏极之间串联有2n组反相器,n为正整数。

11、在本发明的一个或多个实施方式中,所述反相器包括第一反相器和第二反相器,所述第一反相器包括第三mos管和第四mos管,且第三mos管为pmos管,第四mos管为nmos管,所述第三mos管的栅极和第四mos管的栅极相连后连接于第一mos管的漏极,第三mos管的漏极和第四mos管的漏极相连,第三mos管的源极与电源电压vdd相连,第四mos管的源极与地电位相连;

12、所述第二反相器包括第五mos管和第六mos管,且第五mos管为pmos管,第六mos管为nmos管,所述第五mos管的栅极和第六mos管的栅极相连后连接于第三mos管的漏极和第四mos管的漏极,第五mos管的漏极和第六mos管的漏极相连后连接于上电复位电路的输出端,第五mos管的源极与电源电压vdd相连,第六mos管的源极与地电位相连。

13、在本发明的另一个方面当中,提供了一种欠压锁定电路,所述欠压锁定电路包括:

14、如上所述的上电复位电路,用于提供上电复位信号;

15、基准电压产生电路,用于产生基准电压vref;

16、带隙基准电路,用于产生带隙基准电压vbg;

17、比较器,所述比较器电性连接于上电复位电路与地电位之间,第一输入端与基准电压产生电路相连,第二输入端与带隙基准电路相连,输出端用于输出欠压锁定信号。

18、在本发明的一个或多个实施方式中,所述带隙基准电路包括:

19、双极型晶体管单元,包括第一双极型晶体管及第二双极型晶体管;

20、匹配电阻单元,包括与第一双极型晶体管相连的第一匹配电阻、与第二双极型晶体管相连的第二匹配电阻、与第二匹配电阻相连的第三匹配电阻;

21、运算放大器,具有第一输入端和第二输入端,所述第一输入端连接于第一匹配电阻和第一双极型晶体管之间,所述第二输入端连接于第二匹配电阻和第三匹配电阻之间;

22、第二mos管,所述第二mos管为pmos管,其栅极与运算放大器的输出端相连,源极与电源电压vdd相连,漏极与第一匹配电阻和第二匹配电阻相连,第二mos管的漏极产生带隙基准电压vbg。

23、在本发明的一个或多个实施方式中,所述基准电压产生电路包括第二分压单元,所述第二分压单元包括电性连接于电源电压vdd与第二分压节点之间的第四电阻、及电性连接于第二分压节点和地电位之间的第五电阻,所述第二分压单元于第二分压节点上输出基准电压vref。

24、在本发明的一个或多个实施方式中,所述欠压锁定电路还包括第七mos管和反相器inv,所述第七mos管为nmos管,所述反相器inv的输入端与上电复位电路的输出端相连,所述反相器的输出端与第七mos管的栅极相连,第七mos管的源极与地电位相连,漏极与基准电压产生电路的输出端相连。

25、在本发明的另一个方面当中,还提供了一种欠压锁定方法,所述方法包括:

26、在上电过程中,电源电压vdd逐渐增大,基准电压vref随电源电压vdd逐渐增大,带隙基准电压vbg随电源电压vdd逐渐增大后保持稳定,于电源电压vdd为第一电压v1和第二电压v2时,基准电压vref与带隙基准电压vbg相等;

27、当电源电压vdd为上电复位信号的翻转点电压vl2h时,上电复位信号翻转,上电复位信号的翻转点电压vl2h满足v1<vl2h<v2。

28、与现有技术相比,根据本发明实施方式的上电复位电路、欠压锁定电路及欠压锁定方法,通过设置第一分压单元,一方面可调整上电复位电路的翻转点电压,避免在欠压锁定电路翻转电压较低时,高温ff corner时上电复位电路的翻转电压过低导致欠压锁定电路有多次翻转的问题;另一方面,可以使上电复位电路的翻转点电压满足vl2h<2vgs,实现在低温ss corner状态下进一步降低上电复位电路的翻转电压,满足欠压锁定电路翻转电压较低时的应用场景。

- 还没有人留言评论。精彩留言会获得点赞!