自唤醒电路及电子设备的制作方法

本发明涉及电路,尤其涉及一种自唤醒电路及电子设备。

背景技术:

1、在物联网技术领域,极低的功耗可以有效延长电子设备的使用时间,进而提高电子设备的产品竞争力。

2、为降低电子设备的功耗,通常通过控制电子设备在较长时间内处于休眠状态来实现。在使用电子设备时,将电子设备唤醒。

3、然而,现有技术中,多数采用定时器溢出方式实现自唤醒,需要时钟电路的支持。然而,依赖内/外部的时钟电路才能触发类似中断等情况下,实现连续的自唤醒,无法满足极低功耗的应用场景。

技术实现思路

1、本发明实施例解决的是无时钟电路的情况下,难以实现电子设备连续的自唤醒的技术问题。

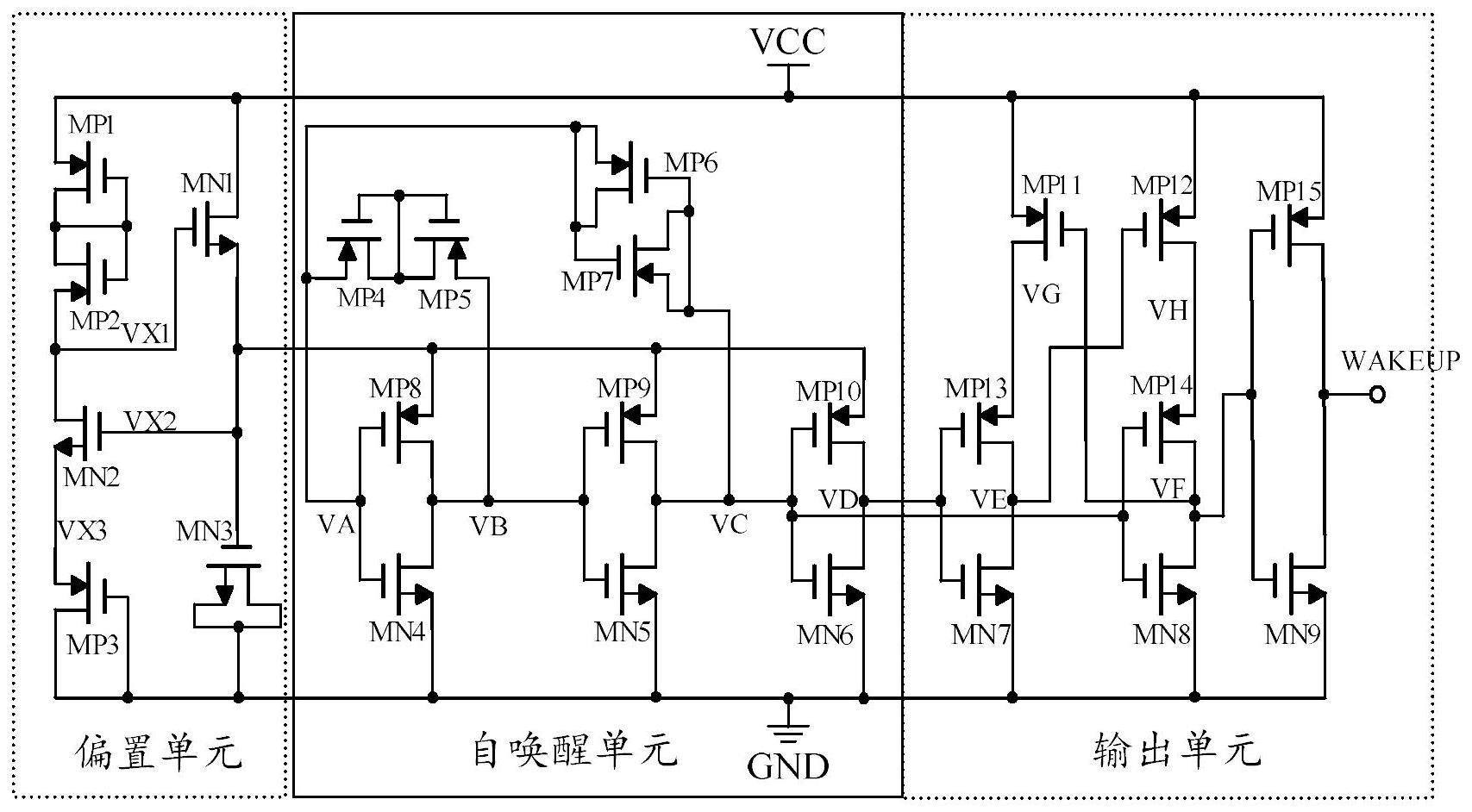

2、为解决上述技术问题,本发明实施例提供一种自唤醒电路,包括:偏置单元、自唤醒单元、输出单元,其中:所述偏置单元,其输出端与所述自唤醒单元的输入端耦接,适于生成偏置电压并输出至所述自唤醒单元;所述自唤醒单元,其第一输出端与所述输出单元的第一输入端耦接,输出第一自唤醒信号;其第二输出端与所述输出单元的第二输入端耦接,输出第二自唤醒信号;所述第一自唤醒信号与所述第二自唤醒信号互补;所述输出单元,适于根据所述第一自唤醒信号以及所述第二自唤醒信号,输出唤醒信号。

3、可选的,所述偏置单元,包括:第一阻抗单元、二极管、功率管、第一电容、放大管,其中:所述第一阻抗单元,其第一端输入电源电压,其第二端与所述功率管的控制端、放大管的第一端耦接;所述功率管,其控制端输入所述电源电压,其第二端与所述放大管的第一端耦接;所述放大管,其控制端与所述偏置单元的输出端耦接,其第二端与所述二极管的第一端耦接;所述二极管,其第二端与所述偏置单元的接地端耦接;所述第一电容,其第一端与所述偏置单元的输出端耦接,其第二端与所述偏置单元的接地端耦接。

4、可选的,所述第一阻抗单元包括:第一pmos管以及第二pmos管,其中:所述第一pmos管,其源极与所述第一阻抗单元的第一端耦接,其栅极与其漏极耦接,其漏极与所述第二pmos管的栅极以及所述第二pmos管的漏极耦接;所述第二pmos管,其源极与所述第一阻抗单元的第二端耦接。

5、可选的,所述功率管包括第一nmos管,所述放大管包括第二nmos管,所述二极管包括第三pmos管,所述电容包括第三nmos管,其中:所述第一nmos管,其漏极为所述功率管的第一端,其栅极为所述功率管的控制端,其源极为所述功率管的第二端;所述第二nmos管,其漏极为所述放大管的第一端,其栅极为所述放大管的控制端,其源极为所述放大管的第二端;所述第三pmos管,其源极为所述二极管的第一端;其栅极与其漏极耦接,为所述二极管的第二端;所述第三nmos管,其栅极为所述第一电容的第一端;其源极与其漏极耦接,为所述第一电容的第二端。

6、可选的,所述自唤醒单元,包括三级反相模块、第二阻抗单元以及第二电容,其中:第一反相模块,其电源端与所述自唤醒单元的输入端耦接,其输入端与所述第二电容的第一端耦接,其输出端与所述第二反相模块的输入端耦接;所述第二反相模块,其电源端与所述自唤醒单元的输入端耦接,其输出端与所述第三反相模块的输入端耦接;所述第三反相模块,其电源端与所述自唤醒单元的输入端耦接,其输入端与所述自唤醒单元的第一输出端耦接,其输出端与所述自唤醒单元的第二输出端耦接;所述第二阻抗单元,其第一端与所述第一反相模块的输入端耦接,其第二端与所述第一反相模块的输出端耦接;所述第二电容,其第二端与所述第二反相模块的输出端耦接。

7、可选的,所述第二阻抗单元包括第四pmos管以及第五pmos管,其中:所述第四pmos管,其源极与所述第二阻抗单元的第一端耦接,其栅极与其漏极耦接,其漏极与所述第五pmos管的栅极以及所述第五pmos管的漏极耦接;所述第五pmos管,其源极与所述第二阻抗单元的第二端耦接。

8、可选的,所述第二电容为mos电容,包括第六pmos管以及第七pmos管,其中:所述第六pmos管,其源极与其漏极耦接,且与所述第二电容的第一端耦接;其栅极与第七pmos管的漏极耦接,其漏极与所述第七pmos管的栅极耦接;所述第七pmos管,其源极与其漏极耦接,且其源极与所述第二电容的第二端耦接。

9、可选的,所述第一反相模块包括第八pmos管以及第四nmos管,所述第二反相模块包括第九pmos管以及第五nmos管,所述第三反相模块包括第十pmos管以及第六nmos管,其中:所述第八pmos管,其源极与所述第一反相模块的电源端耦接,其栅极与所述第一反相模块的输入端耦接,其漏极与所述第一反相模块的输出端耦接;所述第四nmos管,其栅极与所述第八pmos管的栅极耦接,其漏极与所述第八pmos管的漏极耦接,其源极接地;所述第九pmos管,其源极与所述第二反相模块的电源端耦接,其栅极与所述第二反相模块的输入端耦接,其漏极与所述第二反相模块的输出端耦接;所述第五nmos管,其栅极与所述第九pmos管的栅极耦接,其漏极与所述第九pmos管的漏极耦接,其源极接地;所述第十pmos管,其源极与所述第三反相模块的电源端耦接,其栅极与所述第三反相模块的输入端耦接,其漏极与所述第三反相模块的输出端耦接;所述第六nmos管,其栅极与所述第十pmos管的栅极耦接,其漏极与所述第十pmos管的漏极耦接,其源极接地。

10、可选的,所述输出单元,包括电平移位模块以及第四反相模块,其中:所述电平移位模块,其第一输入端与所述自唤醒单元的第一输出端耦接,其第二输入端与所述自唤醒单元的第二输出端耦接,其输出端与所述第四反相模块的输入端耦接;所述第四反相模块,其输出端与所述输出单元的输出端耦接。

11、可选的,所述电平移位模块,包括:第十一pmos管、第十二pmos管、第十三pmos管、第十四pmos管、第七nmos管以及第八nmos管,其中:所述第十一pmos管,其源极与所述电平移位模块的电源端耦接,其栅极与所述第十四pmos管的漏极耦接,其漏极与所述第十三pmos管的源极耦接;所述第十二pmos管,其源极与所述电平移位模块的电源端耦接,其栅极与所述第十三pmos管的漏极耦接,其漏极与所述第十四pmos管的源极耦接;所述第十三pmos管,其栅极与所述电平移位模块的第一输入端耦接,其漏极与所述第七nmos管的漏极耦接;所述第十四pmos管,其栅极与所述电平移位模块的第二输入端耦接,其漏极与所述电平移位模块的输出端耦接;所述第七nmos管,其栅极与所述第十三pmos管的栅极耦接,其漏极与所述第十三pmos管的漏极耦接,其源极与所述电平移位模块的接地端耦接;所述第八nmos管,其栅极与所述第十四pmos管的栅极耦接,其漏极与所述第十四pmos管的漏极耦接,其源极与所述电平移位模块的接地端耦接。

12、可选的,所述第四反相模块,包括第十五pmos管以及第九nmos管,其中:所述第十五pmos管,其源极与所述第四反相模块的电源端耦接,其栅极与所述第四反相模块的输入端耦接,其漏极与所述第四反相模块的输出端耦接;所述第九nmos管,其栅极与所述第十五pmos管的栅极耦接,其漏极与所述第十五pmos管的漏极耦接,其源极与所述第四反相模块的接地端耦接。

13、本发明实施例还提供了一种电子设备,包括上述任一种所述的自唤醒电路。

14、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

15、由偏置单元生成偏置电压并输出至自唤醒单元,自唤醒单元生成第一自唤醒信号以及第二自唤醒信号。输出单元根据第一自唤醒信号以及第二自唤醒信号,输出唤醒信号。上述方案,无需依赖时钟电路,能够实现电子设备连续的自唤醒。

- 还没有人留言评论。精彩留言会获得点赞!