一种高码速率窄相关器产生方法及装置与流程

本发明涉及高精度微波双向时间同步领域,尤其涉及一种高码速率窄相关器产生方法及装置。

背景技术:

1、双向法时间比对是目前国际公认的最高精度的时间比对方法,广泛应用于国际高精度时间频率量值远程比对,在时间频率量传和溯源方法中的地位无可替代。双向时间比对利用信号扩频调制技术对定时信号的相关信息进行高精度的扩频调制发射,通过卫星、微波或光纤链路对信号进行传输,远程比对站对比对信号进行快速捕获、精密跟踪和精确解算,得到信号传播时延,通过交换传播时延数据便可以精确的获得比对站间的时间差信息,可以获得纳秒量级时间同步水平。双向法广泛应用于卫星导航、深空探测和无人机编队等等多个领域。

2、当前,动平台间微波组网对时间比对指标越来越高,有些特定场景下要求达到皮秒(ps)量级,即1×10-12秒。而动平台往往工作在城市建筑和楼宇间等等密集场所,多径信号是微波双向时间比对其中一个很大的误差项,往往达到纳秒(ns)量级,即1×10-9秒,这就对微波信号的跟踪环路提出非常苛刻的要求。为保证系统指标,一般在两个方面进行系统设计和优化。一方面为克服多径效应影响,采用窄相关器跟踪方法,即超前滞后相关间距远小于一个码片持续时长,有些甚至可以小到0.01个码片;另一方面为了提升双向时间比对性能,一般都采用100mhz甚至几百mhz高码速率信号进行双向时间比对。后端处理设备为了降低功耗和提升处理能力都采用零中频接收方法,该种方法系统采样率一般都略高于码速率的2倍,即200mhz以上,但受后端逻辑器件处理速率影响,该采样率不能无限增加。可以看出以上两方面是相互矛盾的,即在采样率不够高的情况下,传统方法通过移动整数个时钟周期进行码的超前滞后控制无法达到0.1甚至0.01个码片延时精度,需要寻找新方法进行延时处理。

技术实现思路

1、本发明的目的在于提供一种高码速率窄相关器产生方法及装置,通过分数延迟滤波器对产生的本地码序列进行非整数时钟的精确延时,实现超前和滞后码的精确产生,解决高码速率和低系统采样率窄相关器产生问题。

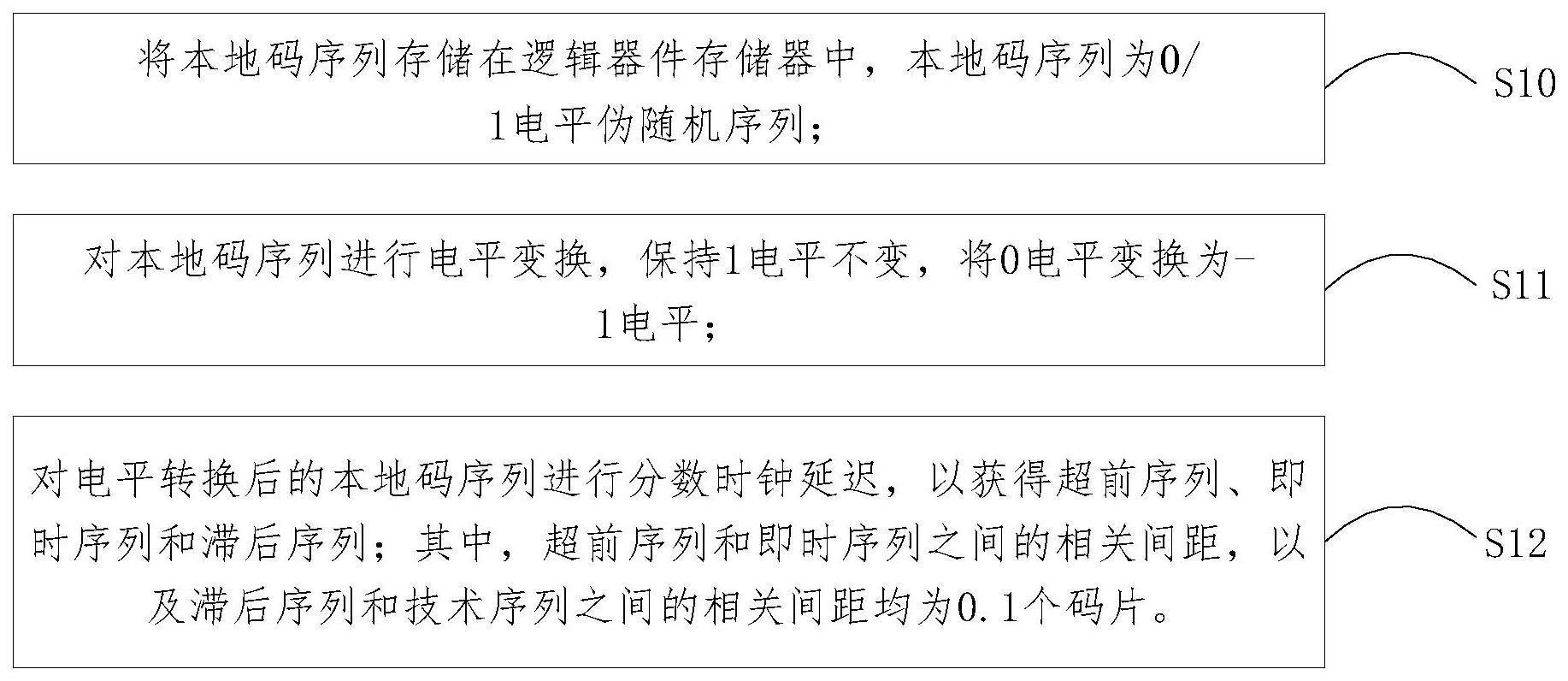

2、第一方面,本发明提供一种高码速率窄相关器产生方法,包括以下步骤:

3、将本地码序列存储在逻辑器件存储器中,本地码序列为0/1电平伪随机序列;

4、对本地码序列进行电平变换,保持1电平不变,将0电平变换为-1电平;

5、对电平转换后的本地码序列进行分数时钟延迟,以获得超前序列、即时序列和滞后序列;其中,超前序列和即时序列之间的相关间距,以及滞后序列和技术序列之间的相关间距均为0.1个码片。

6、与现有技术相比,通过分数延迟滤波器对产生的本地码序列进行非整数时钟的精确延时,实现超前和滞后码的精确产生,解决高码速率和低系统采样率窄相关器产生问题。

7、作为一种可能的实现方式,确定系统时钟为250mhz,码速率为100mhz,超前/滞后相关间距为0.1个码片,此时,拟产生三个码序列,分别为滞后0.1个码片超前序列、滞后0.2个码片即时序列和滞后0.3个码片滞后序列;基于此,确定需要对电平转换后的本地码序列延迟的时钟周期分别为0.04、0.08和0.12;通过0.04、0.08和0.12设计分数延迟滤波器,计算得到3个分数延迟滤波器的参数;利用上述三个分数延迟滤波器对电平转换后的本地码序列分别进行分数延迟滤波,以获得超前序列、即时序列和滞后序列。

8、作为一种可能的实现方式,分数延迟滤波器为低阶分数延迟滤波器。

9、作为一种可能的实现方式,在系统时钟的驱动下,利用数控振荡器方法不断更改递增查询地址,实时读取产生本地码序列。

10、作为一种可能的实现方式,时钟周期通过以下方式确定:

11、滞后的码片数*(码速率/系统时钟)。

12、第二方面,高码速率窄相关器产生装置,其特征在于,包括:

13、逻辑器件存储器,用于将本地码序列存储在逻辑器件存储器中,所述本地码序列为0/1电平伪随机序列;

14、电平变换器,用于对所述本地码序列进行电平变换,保持1电平不变,将0电平变换为-1电平;

15、分数时钟延迟器,用于对电平转换后的所述本地码序列进行分数时钟延迟,以获得超前序列、即时序列和滞后序列;其中,所述超前序列和即时序列之间的相关间距,以及所述滞后序列和技术序列之间的相关间距均为0.1个码片。

16、作为一种可能的实现方式,确定系统时钟为250mhz,码速率为100mhz,超前/滞后相关间距为0.1个码片,此时,拟产生三个码序列,分别为滞后0.1个码片超前序列、滞后0.2个码片即时序列和滞后0.3个码片滞后序列;基于此,确定需要对电平转换后的所述本地码序列延迟的时钟周期分别为0.04、0.08和0.12;通过0.04、0.08和0.12设计分数延迟滤波器,计算得到3个分数延迟滤波器的参数;利用上述三个分数延迟滤波器对电平转换后的所述本地码序列分别进行分数延迟滤波,以获得超前序列、即时序列和滞后序列。

17、作为一种可能的实现方式,所述分数延迟滤波器为低阶分数延迟滤波器。

18、作为一种可能的实现方式,在系统时钟的驱动下,利用数控振荡器方法不断更改递增查询地址,实时读取产生本地码序列。

19、作为一种可能的实现方式,时钟周期通过以下方式确定:

20、滞后的码片数*(码速率/系统时钟)。

21、与现有技术相比,本发明提供的高码速率窄相关器产生装置的有益效果与上述技术方案提供的高码速率窄相关器产生方法的有益效果相同,此处不做赘述。

技术特征:

1.一种高码速率窄相关器产生方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的高码速率窄相关器产生方法,其特征在于,确定系统时钟为250mhz,码速率为100mhz,超前/滞后相关间距为0.1个码片,此时,拟产生三个码序列,分别为滞后0.1个码片超前序列、滞后0.2个码片即时序列和滞后0.3个码片滞后序列;基于此,确定需要对电平转换后的所述本地码序列延迟的时钟周期分别为0.04、0.08和0.12;通过0.04、0.08和0.12设计分数延迟滤波器,计算得到3个分数延迟滤波器的参数;利用上述三个分数延迟滤波器对电平转换后的所述本地码序列分别进行分数延迟滤波,以获得超前序列、即时序列和滞后序列。

3.根据权利要求2所述的高码速率窄相关器产生方法,其特征在于,所述分数延迟滤波器为低阶分数延迟滤波器。

4.根据权利要求1所述的高码速率窄相关器产生方法,其特征在于,在系统时钟的驱动下,利用数控振荡器方法不断更改递增查询地址,实时读取产生本地码序列。

5.根据权利要求2所述的高码速率窄相关器产生方法,其特征在于,时钟周期通过以下方式确定:

6.一种高码速率窄相关器产生装置,其特征在于,包括:

7.根据权利要求6所述的高码速率窄相关器产生装置,其特征在于,确定系统时钟为250mhz,码速率为100mhz,超前/滞后相关间距为0.1个码片,此时,拟产生三个码序列,分别为滞后0.1个码片超前序列、滞后0.2个码片即时序列和滞后0.3个码片滞后序列;基于此,确定需要对电平转换后的所述本地码序列延迟的时钟周期分别为0.04、0.08和0.12;通过0.04、0.08和0.12设计分数延迟滤波器,计算得到3个分数延迟滤波器的参数;利用上述三个分数延迟滤波器对电平转换后的所述本地码序列分别进行分数延迟滤波,以获得超前序列、即时序列和滞后序列。

8.根据权利要求6所述的高码速率窄相关器产生装置,其特征在于,所述分数延迟滤波器为低阶分数延迟滤波器。

9.根据权利要求6所述的高码速率窄相关器产生装置,其特征在于,在系统时钟的驱动下,利用数控振荡器方法不断更改递增查询地址,实时读取产生本地码序列。

10.根据权利要求7所述的高码速率窄相关器产生装置,其特征在于,时钟周期通过以下方式确定:

技术总结

本发明公开高码速率窄相关器产生方法及装置。涉及高精度微波双向时间同步领域。通过分数延迟滤波器对产生的本地码序列进行非整数时钟的精确延时,实现超前和滞后码的精确产生,解决高码速率和低系统采样率窄相关器产生问题。包括以下步骤:将本地码序列存储在逻辑器件存储器中,本地码序列为0/1电平伪随机序列。对本地码序列进行电平变换,保持1电平不变,将0电平变换为‑1电平。对电平转换后的本地码序列进行分数时钟延迟,以获得超前序列、即时序列和滞后序列;其中,超前序列和即时序列之间的相关间距,以及滞后序列和技术序列之间的相关间距均为0.1个码片。

技术研发人员:王海峰,王学运,程燕,易航,郭梁,杨文哲,王宏博,张升康

受保护的技术使用者:北京无线电计量测试研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!