自举开关采样电路及采样控制方法、自举开关及数据转换系统与流程

本发明属于电子电路,涉及一种采样电路,尤其涉及一种自举开关采样电路及采样控制方法、自举开关及数据转换系统。

背景技术:

1、在数据转换系统(ad/da)中的模拟信号采样部分的速度和精度决定了系统整体速度和精度,然而用mos管实现的采样开关的导通电阻会随着输入信号幅度的变化而变化,为了实现恒定的导通电阻,一种名为自举开关的采样电路应运而生,其基本原理就是在采样的时候,在开关mos管的栅极和源极之间施加一个恒定的压降。

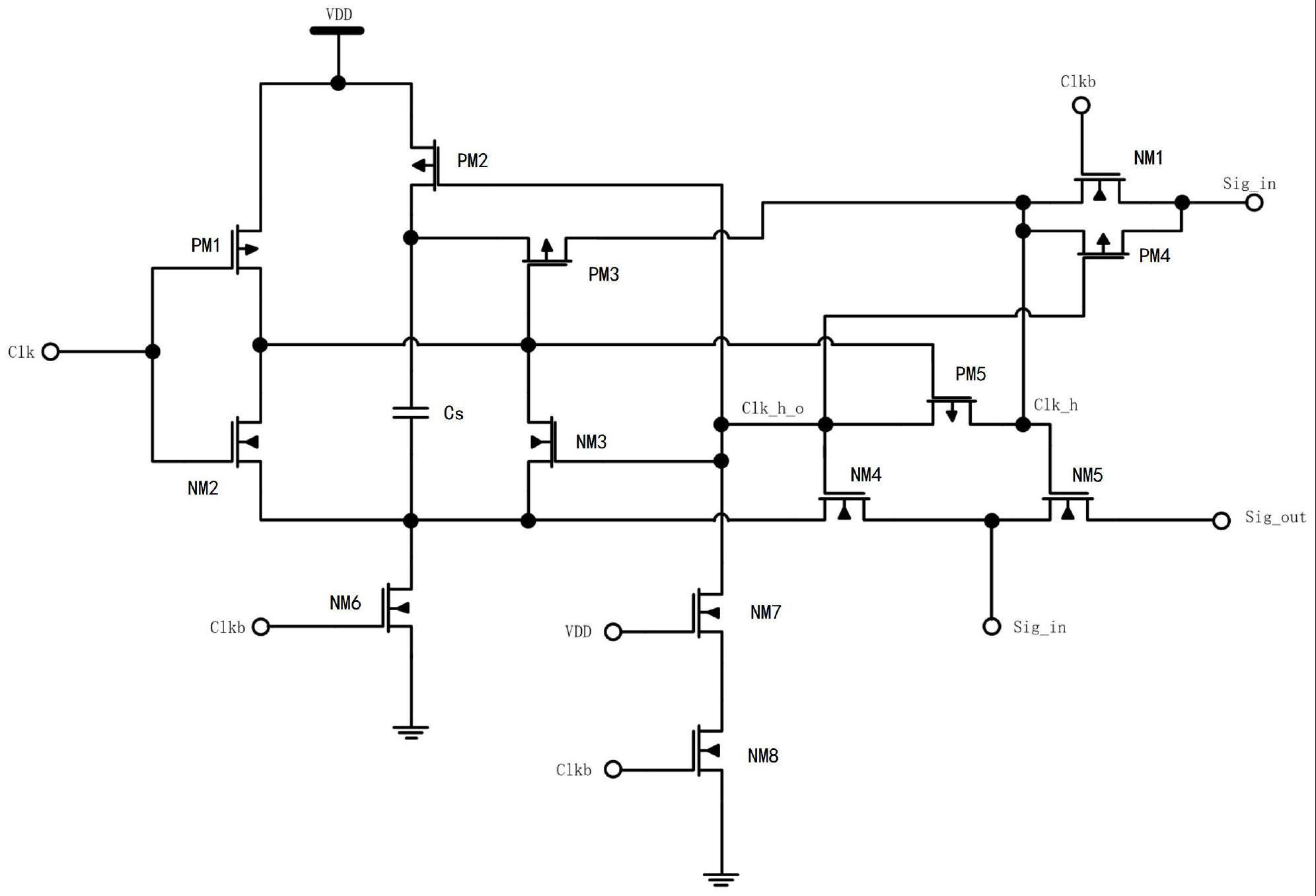

2、常规的自举开关采样电路如图1所示;请参阅图1,常规自举开关采样电路的工作原理如下:在clk为低电平、clkb为高电平时,第二p型mos管pm2和第六n型mos管nm6导通,第三p型mos管pm3和第四n型mos管nm4关断,vdd对电容cs充电,充到vdd;同时,第一n型mos管nm1和第四p型mos管pm4导通,clk_h电平拉到地。

3、当clk为高电平、clkb为低电平时,第二p型mos管pm2和第六n型mos管nm6关断,第三p型mos管pm3和第四n型mos管nm4导通,输入信号通过第四n型mos管nm4叠加到电容cs上,使得电容cs上正端的电压值达到vdd+vsig(vsig是信号幅值);再通过第三p型mos管pm3,把clk_h拉高到vdd+vsig。因此,信号在通过采样开关第五n型mos管nm5时,该采样管的栅源电压始终保持在vdd,从而实现了采样电阻的恒定值。

4、然而,这种电路结构实现的自举采样时钟,因为施加在采样开关mos管上的时钟峰峰值是随输入信号的幅值发生变化的,这导致馈通到采样电容上的电荷也是随信号幅值改变的。在差分应用中,因为馈通到正反端采样电容上的电荷差值不是固定值,而是一个随信号变化的值;因此会在采样电容上叠加信号谐波,导致数据转换的精度下降。

5、有鉴于此,如今迫切需要设计一种新的自举开关采样电路,以便克服现有自举开关采样电路存在的上述至少部分缺陷。

技术实现思路

1、本发明提供一种自举开关采样电路及采样控制方法、自举开关及数据转换系统,可实现采样电阻在设定恒定值,同时保证正负端馈通到采样电容上的电荷相当,可提高数据转换的精确度。

2、为解决上述技术问题,根据本发明的一个方面,采用如下技术方案:

3、一种自举开关采样电路,所述自举开关采样电路包括:第一p型mos管pm1、第二p型mos管pm2、第三p型mos管pm3、第四p型mos管pm4、第五p型mos管pm5、第一n型mos管nm1、第二n型mos管nm2、第三n型mos管nm3、第四n型mos管nm4、第五n型mos管nm5、第六n型mos管nm6、第七n型mos管nm7、第八n型mos管nm8及电容cs;

4、所述第一p型mos管pm1的栅极分别连接clk信号、第二n型mos管nm2的栅极,所述第一p型mos管pm1的源极分别连接vdd信号、第二p型mos管pm2的源极;所述第一p型mos管pm1的漏极分别连接第二n型mos管nm2的漏极、第三p型mos管pm3的栅极、第三n型mos管nm3的漏极、第五p型mos管pm5的栅极;

5、所述第二p型mos管pm2的漏极分别连接第三p型mos管pm3的漏极、电容cs的第一端;所述第二p型mos管pm2的栅极分别连接第三n型mos管nm3的栅极、第四p型mos管pm4的栅极、第五p型mos管pm5的漏极、第四n型mos管nm4的栅极、第七n型mos管nm7的漏极;

6、所述第三p型mos管pm3的源极分别连接第一n型mos管nm1的源极、第四p型mos管pm4的漏极、第五p型mos管pm5的源极、第五n型mos管nm5的栅极;

7、所述第四p型mos管pm4的源极分别连接sig_in信号、所述第一n型mos管nm1的漏极;第一n型mos管nm1的栅极连接clkb信号;

8、所述第二n型mos管nm2的源极分别连接电容cs的第二端、第三n型mos管nm3的源极、第四n型mos管nm4的源极、第六n型mos管nm6的漏极;

9、所述第四n型mos管nm4的漏极分别连接sig_in信号、所述第五n型mos管nm5的源极;所述第五n型mos管nm5的漏极连接sig_out信号;

10、所述第六n型mos管nm6的栅极连接clkb信号,所述第六n型mos管nm6的发射极接地;

11、所述第七n型mos管nm7的栅极连接vdd信号,所述第七n型mos管nm7的发射极连接第八n型mos管nm8的漏极;所述第八n型mos管nm8的栅极连接clkb信号,第八n型mos管nm8的发射极接地。

12、作为本发明的一种实施方式,vdd是高电压信号,clk是普通时钟信号,clkb是clk的反相信号,clk_h和clk_h_o是升压后的时钟信号,sig_in是输入信号,sig_out是经过自举开关采样电路采样后的输出信号。

13、根据本发明的另一个方面,采用如下技术方案:一种自举开关,所述自举开关包括上述的自举开关采样电路。

14、根据本发明的另一个方面,采用如下技术方案:一种数据转换系统,所述数据转换系统包括上述的自举开关采样电路。

15、根据本发明的又一个方面,采用如下技术方案:一种上述自举开关采样电路的采样控制方法,所述采样控制方法包括:

16、在clk信号为低电平、clkb信号为高电平的状态下,第二p型mos管pm2、第六n型mos管nm6导通,第三p型mos管pm3、第四n型mos管nm4关断,电源电压vdd对电容cs充电,充至电源电压vdd的对应值;同时,第一n型mos管nm1、第四p型mos管pm4导通,clk_h信号的电平拉到sig_in信号的输入电平,第七n型mos管nm7、第八n型mos管nm8导通,clk_h_o信号被拉低至地,此时第五p型mos管pm5关断,隔离clk_h信号和clk_h_o信号;

17、在clk信号为高电平、clkb信号为低电平的状态下,第二p型mos管pm2、第六n型mos管nm6关断,第三p型mos管pm3、第四n型mos管nm4导通;输入信号sig_in信号通过第四n型mos管nm4叠加到电容cs上,使得电容cs上正端的电压值达到电源电压vdd的电压值与输入信号sig_in的信号幅值之和;再通过第三p型mos管pm3把clk_h信号拉高到电源电压vdd的电压值与输入信号sig_in的信号幅值之和;同时第五p型mos管pm5导通,clk_h_o信号也被拉到电源电压vdd的电压值与输入信号sig_in的信号幅值之和对应电平;

18、信号在通过采样开关第五n型mos管nm5时,第五n型mos管nm5的栅源电压始终保持在电源电压vdd对应的电压值,同时控制时钟的幅值变化也一直维持在电源电压vdd对应的电压值;实现采样电阻的恒定值,保证正负端馈通到采样电容上的电荷相当。

19、本发明的有益效果在于:本发明提出的自举开关采样电路及采样控制方法、自举开关及数据转换系统,可实现采样电阻在设定恒定值,同时保证正负端馈通到采样电容上的电荷相当;本发明可提高数据转换的精确度。

- 还没有人留言评论。精彩留言会获得点赞!