基于标准单元库的全数字锁相环电路、芯片及锁相方法与流程

本发明属于芯片电路,尤其涉及一种基于标准单元库的全数字锁相环电路、芯片、锁相方法及可读存储介质。

背景技术:

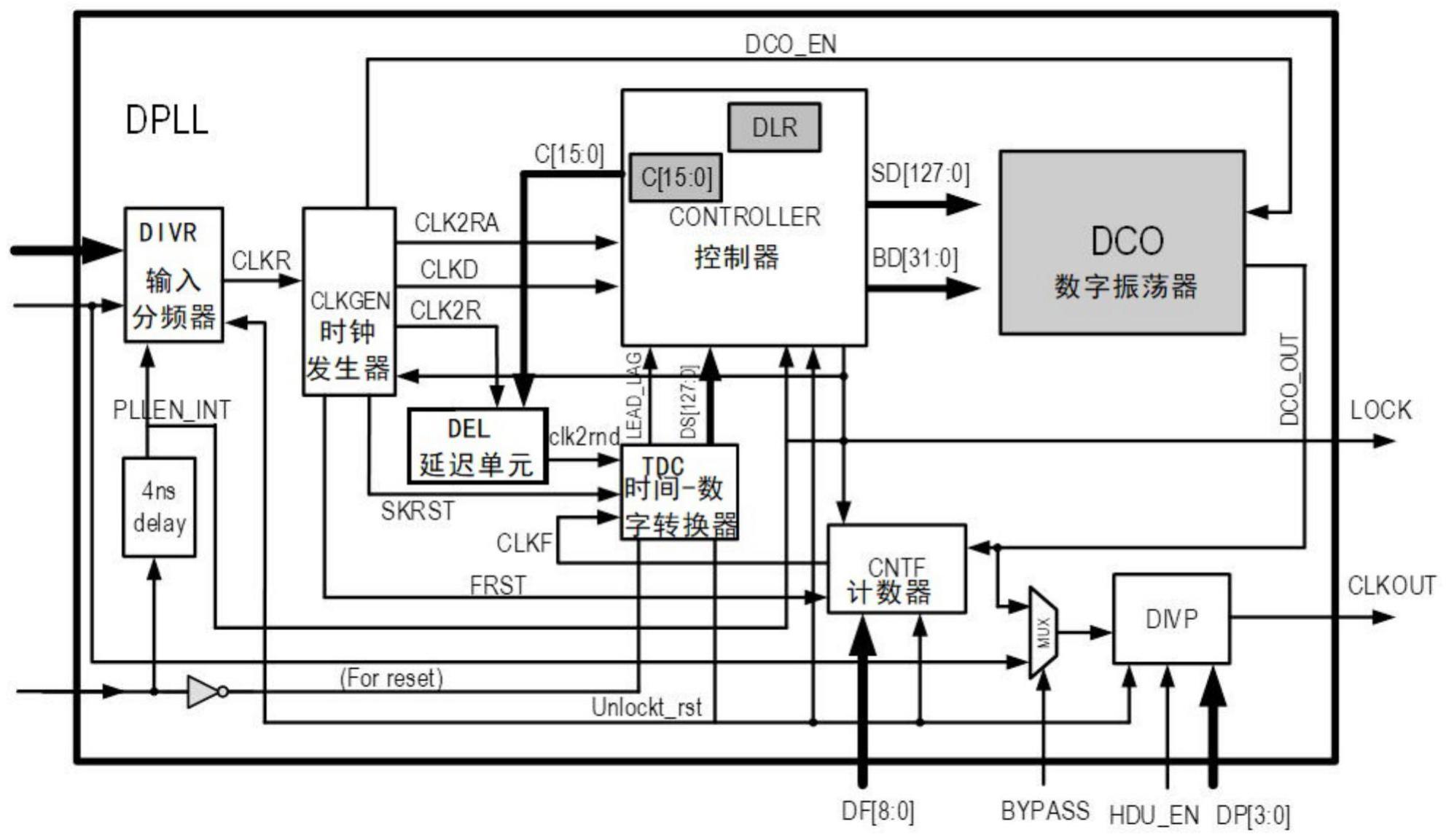

1、数字pll(phase-locked loops,锁相环)以其低功耗,抗干扰能力强,面积小等优点在很多应用领域已经逐步取代模拟pll。如图1所示,为现有技术中数字锁相环的电路示意图。数字锁相环由输入分频divr、时钟发生器clkgen、时间-数字转换器tdc、数字振荡器dco、计数器cntf、和控制器controller组成。

2、锁定前,在参考时钟clk2r的半个周期内,对数字振荡器dco的周期计数。当计数器cntf计数到预定值df时,计数器cntf产生一个clkf上升沿信号。通过时间-数字转换器tdc来测量clkf的上升沿和clk2r的下降沿的相位差值来调节数字振荡器dco的频率,使clkf的上升沿和clk2r的下降沿保持一致来完成pll的锁定。

3、锁定后,通过时间-数字转换器tdc实时测量clkf的上升沿和clk2r的下降沿的相位差值来调节数字振荡器dco的频率,使clkf的上升沿和clk2r的下降沿保持一致;如外界条件变化使clkf的上升沿和clk2r的下降沿的相位差值超过的时间-数字转换器tdc的测试范围,将进入失锁状态。

4、进入失锁状态后,pll将自动重新开始锁定。

5、图1的现有技术,各个内部信号的时序要精确控制,从而保证时间-数字转换器tdc测量的是准确的参考时钟clk2r的半个周期的振荡器输出的计数结果;同时对于数字振荡器dco和时间-数字转换器tdc的单位延迟也需要精确调制来满足固定的逻辑控制算法。由于对精度的要求,需要全定制的方式实现,通过手工电路和版图优化来实现;为了提高精度,电路和版图设计要反复迭代,开发周期比较长。

技术实现思路

1、为解决上述问题,本发明的目的是提供一种基于标准单元库的全数字锁相环电路、芯片及锁相方法,该基于标准单元库的全数字锁相环电路、芯片及锁相方法通过可配的参数完成时延补偿及调频,缩短了全数字锁相环开发时间。

2、为实现上述目的,本发明的技术方案为:一种基于标准单元库的全数字锁相环电路,包括:时钟发生器,通过输入分频器获取参考时钟信号并按照预设算法生成第一时钟信号、第二时钟信号和第三时钟信号;控制器,接收所述时钟发生器输出的第一时钟信号和第二时钟信号并进行预设处理以获取针对数字振荡器的控制信号和针对第三时钟信号的补偿参数;延迟单元,基于所述补偿参数对所述时钟发生器输出的第三时钟信号进行相应补偿处理后发送给时间-数字转换器;数字振荡器,响应于时钟发生器输入的使能信号获取控制器输出的控制信号进行预设频率的震荡;计数器,响应于输入的倍频参数将震荡信号的上升沿发送给时间-数字转换器;时间-数字转换器,基于补偿处理后的第三时钟信号的下降沿和震荡信号的上升沿进行相位差数字转换处理,并将转换处理获取的数值发送给所述控制器,所述控制器基于所述数值进行预设的参数的调节。

3、在本发明的一个实施例中,所述延迟单元包括复数个标准延迟结构,基于所述补偿参数使得预设数量的所述标准延迟结构工作以实现所述第三时钟信号与所述震荡信号补偿至同一起振点。

4、在本发明的一个实施例中,所述数字振荡器包括复数个第一标准调频结构、复数个第二标准调频结构和调频电路,所述复数个第一标准调频结构和所述复数个第二标准调频结构均与所述调频电路连接并分别用于粗调频和细调频。

5、在本发明的一个实施例中,所述时间-数字转换器包括复数个标准相位比较结构,基于所述复数个标准相位比较结构计算补偿处理后的第三时钟信号的下降沿和震荡信号的上升沿的相位差数值,将所述数值发送给所述控制器。

6、在本发明的一个实施例中,所述计数器和所述时间-数字转换器分别具有使能端,所述使能端受控于所述时钟发生器。

7、在本发明的一个实施例中,所述计数器接受的倍频参数可调。

8、基于相同的构思,本发明还提供一种芯片,所述芯片包括上述任意所述的基于标准单元库的全数字锁相环电路。

9、基于相同的构思,本发明还提供一种基于标准单元库的全数字锁相环电路锁相方法,应用于上述任意一项所述的基于标准单元库的全数字锁相环电路,包括以下步骤以实现相位追踪:获取第一时钟信号和第二时钟信号并基于预设算法计算获得针对数字振荡器的控制信号,控制所述数字振荡器进行预设频率的震荡;通过延迟单元基于预设方法对第三时钟信号进行补偿处理后发送给时间-数字转换器;通过所述时间-数字转换器对所述补偿处理后的第三时钟信号和震荡信号进行相位差数字转换处理,获取转换处理后的数值,基于所述数值进行预设的参数的调节;其中,所述第一时钟信号、所述第二时钟信号、所述第三时钟信息为时钟发生器基于参考时钟信号产生。

10、在本发明的一个实施例中,所述方法还包括以下步骤:在所述数值大于预设值的情况下,向第一方向调节控制器输出的控制信号;在所述数值等于预设值的情况下,保持控制器输出的控制信号;在所述数值小于预设值的情况下,向第二方向调节控制器输出的控制信号。

11、基于相同的构思,本发明还提供一种可读存储介质,所述可读存储介质上存储有处理程序,所述处理程序被处理器执行时实现上述所述的基于标准单元库的全数字锁相环电路锁相方法。

12、本发明由于采用以上技术方案,使其与现有技术相比具有以下的优点和积极效果:

13、1、本发明通过增加可配置的延时单元,从而能够实现基于控制器输出的补偿参数使得第三时钟信号进行相应时间的补偿,使得dco_out和clk2r的起始相位一致,克服相位误差,从而使得在开发过程中无需精确调制来满足固定的逻辑控制算法,从而能够提高开发效率。

14、2、本发明通过在延时单元、数字振荡器和时间-数字转换器内部都设置标准单元,从而使得相应的参数或者控制信号能够灵活的基于实际延迟进行调整,并且在锁相跟踪的过程中实时进行调整,从而提高开发效率。

技术特征:

1.一种基于标准单元库的全数字锁相环电路,其特征在于,包括:

2.根据权利要求1所述的基于标准单元库的全数字锁相环电路,其特征在于,所述延迟单元包括复数个标准延迟结构,基于所述补偿参数使得预设数量的所述标准延迟结构工作以实现所述第三时钟信号与所述震荡信号补偿至同一起振点。

3.根据权利要求1所述的基于标准单元库的全数字锁相环电路,其特征在于,所述数字振荡器包括复数个第一标准调频结构、复数个第二标准调频结构和调频电路,所述复数个第一标准调频结构和所述复数个第二标准调频结构均与所述调频电路连接并分别用于粗调频和细调频。

4.根据权利要求1所述的基于标准单元库的全数字锁相环电路,其特征在于,所述时间-数字转换器包括复数个标准相位比较结构,基于所述复数个标准相位比较结构计算补偿处理后的第三时钟信号的下降沿和震荡信号的上升沿的相位差数值,将所述数值发送给所述控制器。

5.根据权利要求1所述的基于标准单元库的全数字锁相环电路,其特征在于,所述计数器和所述时间-数字转换器分别具有使能端,所述使能端受控于所述时钟发生器。

6.根据权利要求1所述的基于标准单元库的全数字锁相环电路,其特征在于,所述计数器接受的倍频参数可调。

7.一种芯片,其特征在于,所述芯片包括权利要求1至权利要求6任意一项所述的基于标准单元库的全数字锁相环电路。

8.一种基于标准单元库的全数字锁相环电路锁相方法,应用于权利要求1至权利要求6任意一项所述的基于标准单元库的全数字锁相环电路,其特征在于,包括以下步骤以实现相位追踪:

9.根据权利要求8所述的基于标准单元库的全数字锁相环电路锁相方法,其特征在于,还包括以下步骤:

10.一种可读存储介质,其特征在于,所述可读存储介质上存储有处理程序,所述处理程序被处理器执行时实现如权利要求8或权利要求9所述的基于标准单元库的全数字锁相环电路锁相方法。

技术总结

本发明公开一种基于标准单元库的全数字锁相环电路,包括:时钟发生器,用于生成第一时钟信号、第二时钟信号和第三时钟信号;控制器,获取第一时钟信号和第二时钟信号进行处理以获取控制信号和补偿参数;延迟单元,基于补偿参数对第三时钟信号进行相应补偿处理并发送给时间‑数字转换器;数字振荡器,获取控制信号进行预设频率的震荡;计数器,响应于输入的倍频参数将震荡信号的上升沿发送给时间‑数字转换器;时间‑数字转换器,基于补偿处理后的第三时钟信号的下降沿和震荡信号的上升沿进行相位差数字转换处理,并获取数值发送给控制器,控制器基于所述数值进行预设的参数的调节。通过可配的参数完成时延补偿及调频,缩短了全数字锁相环开发时间。

技术研发人员:梁毅,鲁广龙,欧泽涛,罗志宏,刘文超

受保护的技术使用者:广州概伦电子技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!