一种串联谐振感应加热锁相驱动电路的制作方法

1.本实用新型涉及感应加热领域,特别是一种串联谐振感应加热锁相驱动电路。

背景技术:

2.感应加热作为一种加热手段,相比传统的加热方式,有着许多的优点。随着 工业技术的发展,感应加热技术被越来越多的应用到各种工业加热场合,感应加 热电源在加热过程中,被加热工件的物理性质(电阻率、导磁率等)受到材料、形状、温度的不同而不断变化,从而引起负载电路固有谐振频率随之变化。故逆变控制电路要使逆变器的工作频率可以对负载谐振频率自动跟踪。如果无法自动跟踪,会使逆变器功率因数降低,加热效率降低,对设备容量造成浪费。如何实现对负载谐振频率的自动跟踪以及逆变器始终工作在安全状态,是感应加热控制技术的重要研究内容。

3.锁相目的是自动跟踪谐振回路的谐振频率,保持谐振回路的电压和电流相位同步,从而让其工作在纯电阻模式,提高逆变装置的功率因素及工作效率。故锁相的输入端一般都是谐振回路的电压及电流信号。而电压、电流的信号都需要通过隔离采样、传输、移相补偿等操作。不但给电路设计造成较大的复杂程度,而且因电压电流传感器的差异较大,导致鉴相误差较大,给锁相调节大大增加了复杂程度和设计成本。另外为简化电路设计,信号的鉴相、滤波、相位调节、压控振荡输入、逆变输出控制的部分或全部功能由dsp数字处理芯片参与闭环控制。而数字处理芯片存在误判、死机等现象,使系统的稳定性和可靠性降低。

技术实现要素:

4.(一)解决的技术问题

5.本实用新型所要解决的技术问题在于克服上述技术不足,回避电压电流信号鉴相不足,直接采用谐振回路电压和电容电压为鉴相输入信号,简化了采样输入电路,并通过模数电路完成信号的鉴相、滤波、相位调节、压控振荡输出等闭环控制,提高了锁相的稳定性和可靠性。

6.(二)技术方案

7.为实现以上目的,本实用新型通过以下技术方案予以实现:一种串联谐振感应加热锁相驱动电路,包括位于串联谐振感应加热回路中的谐振回路电压ulc、谐振电容电压uc、驱动器d1和驱动器d2、采样比较电路ph1、锁相控制电路pll1、环路滤波调节电路pf1和驱动控制电路ofd1,所述谐振回路电压ulc的输出端和谐振电容电压uc的输出端分别与采样比较电路ph1的输入端电性连接,所述采样比较电路ph1输出端与锁相控制电路pll1中的其中一个输入端电性连接,所述锁相控制电路pll1中的其中一个输出端与环路滤波调节电路pf1的输入端电性连接,所述环路滤波调节电路pf1的输出端与锁相控制电路pll1中的另一个输入端电性连接,所述锁相控制电路pll1的另一个输出端与驱动控制电路ofd1的输入端电性连接,所述驱动控制电路ofd1的输出端分别与驱动器d1与和驱动器d2的输入端电性连接。其中所述的采样比较电路ph1完成对lc谐振回路和电容两端的电压采样、整形,为鉴

相环节提供鉴相输入信号;通过锁相环电路pll1内置的异或鉴相模块完成相位鉴别,输出占空比随相位变化的方波信号;再将鉴相输出的方波信号通过环路滤波调节电路pf1的低通滤波电路整形成直流电压信号up,并通过pi调节器自动跟踪调节,使输出电压udp趋于设定电压(up_ref)。并通过锁相环电路pll1内置的压控振荡输入vco模块将输入的直流电压信号udp按一定线性比例关系转换成对应频率的pwm信号;并通过驱动控制电路ofd1输出两路互补的控制信号驱动电子开关g1~g4,从而形成环路的闭环锁相谐振控制。上述所述的采样比较电路ph1,通过两路非隔离全差分放大电路,分别将谐振回路电压ulc和谐振电容电压uc线性缩小,并通过比较电路整形成方波,由于未对谐振回路电流进行采样,且两路采样比较电路参数一致,大大减少了因采样整形引入的移相偏差,保证了鉴相的精度。上述所述的锁相控制电路pll1,主要包含鉴相和压控振荡两部分功能,其中鉴相是将整形后的方波进行异或运算,输出占空比随相位差变化的方波信号;压控振荡器负责电压—频率线性变换,即将环路滤波调节电路pf1输出电压转换为对应频率的pwm信号,为驱动控制电路提供基准信号。环路滤波调节电路pf1,首先将鉴相输出的占空比方波通过低通滤波器转换为直流电压信号,再通过pi调节自动跟踪闭环调节,使输出电压udp趋于设定电压up_ref(即恒定相位),为压控振荡器提供输入电压。驱动控制电路ofd1将压控振荡器输出的振荡信号作为基准,形成两路互补带死区的驱动信号驱动电子开关,使得lc串联回路产生交变电流。

8.优选的,所述采样比较电路ph1包括谐振电容电压采样模块、谐振回路电压采样模块以及多个波形整形比较电路模块,所述谐振电容电压uc与谐振电容电压采样模块的输入端电性连接,所述谐振电容电压采样模块的输出端与其中一个波形整形比较电路模块的输入端电性连接,所述谐振回路电压ulc与谐振回路电压采样模块的输入端电性连接,所述谐振回路电压采样模块的输出端与另一个波形整形比较电路模块的输入端电性连接,两个所述波形整形比较电路模块的输出端分别得到方波输出square_lc信号和方波输出square_c信号。

9.优选的,所述谐振电容电压采样模块包括位于谐振回路电压ulc中的排插j2,所述谐振回路电压采样模块包括位于谐振电容电压uc中的排插j3,所述采样比较电路ph1的电路结构还包括电阻r21、电阻r27、电阻r41、电阻r47、电阻r18、电阻r28、电阻r38、电阻r49、电阻r24、电阻r26、电阻r45、电阻r48、电阻r34、电阻r51、电阻r30、电阻r50、电阻r35、电阻r52、运放芯片u4c、运放芯片u4d、运放芯片u5a、运放芯片u5b,所述排插j2的1引脚与电阻r21的一端电性连接,所述电阻r21的另一端分别与运放芯片u4c的9引脚和电阻r18的一端电性连接,所述电阻r18的另一端与运放芯片u4c的8引脚电性连接,所述排插j2的2引脚与电阻r27的一端电性连接,所述r27的另一端分别与运放芯片u4c的10引脚和电阻r28的一端电性连接,所述电阻r28的另一端接有参考数值电压vref-2500,所述运放芯片u4c的8引脚与电阻24的一端电性连接,所述电阻r24的另一端与运放芯片u5a的2引脚电性连接,所述运放芯片u5a的3引脚分别与电阻r26的一端和电阻r34的一端电性连接,所述r26的另一端接有参考数值电压vref-2500,所述电阻r34的另一端分别与电阻r30的一端和电阻r35的一端电性连接,所述电阻r30的另一端连接有+15v电压,所述运放芯片u5a的4引脚连接有地线,所述运放芯片u5a的8引脚分别连接有+15v电压和电容c24,所述电容c24的一端连接有电容c25,所述电容c25的一端与另一端电性连接且接有地线;所述排插j3的1引脚与电阻r41的一端电性连接,所述电阻r41的另一端分别与运放芯片u4d的13引脚和电阻r38的一端电性

连接,所述电阻r38的另一端与运放芯片u4d的14引脚电性连接,所述排插j3的2引脚与电阻r47的一端电性连接,所述电阻r47的另一端分别与电阻r49的一端和运放芯片u4d的12引脚电性连接,所述电阻r49的另一端接有参考数值电压vref-2500,所述运放芯片u4d的14引脚与电阻r45的一端电性连接,所述电阻r45的另一端与运放芯片u5b的6引脚电性连接,所述运放芯片u5b的5引脚分别与电阻r48的一端和电阻r51的一端电性连接,所述电阻r48的另一端接有参考数值电压vref-2500,所述运放芯片u5b的7引脚与电阻r51的另一端电性连接,所述电阻r51的另一端分别与电阻r50的一端和电阻r52的一端电性连接,所述电阻r50的另一端接有+15v电压。

10.优选的,所述锁相控制电路pll1包括鉴相模块和压控振荡输入vco模块,两个所述波形整形比较电路模块的输出端与鉴相模块的输入端电性连接,所述鉴相模块的输出端与环路滤波调节电路pf1的输入端电性连接,所述路滤波调节电路pf1的输出端与压控振荡输入vco模块的输入端电性连接,所述压控振荡输入vco模块的输出端调频输出得到pwm_ref信号。

11.优选的,所述鉴相模块的电路结构包括用于接收方波输出square_lc信号和方波输出square_c信号的鉴相输入、运算芯片、占空比输出、压控振荡电压输入、电容c28、电容c29、电阻r37、电阻r42、电阻r33和调频输出模块,所述鉴相输入与运算芯片一侧的输入端电性连接,所述运算芯片另一侧的输出端与占空比输出的输入端电性连接,所述运算芯片另一侧的输入端与压控振荡电压输入的输出端电性连接,所述运算芯片一侧的输出端与电阻r33的一端电性连接,所述电阻r33的另一端与调频输出模块的输入端电性连接,所述运算芯片一侧的输出端与电容c33的一端电性连接,所述电容c33的另一端与运算芯片一侧的输入端电性连接,所述运算芯片一侧的输出端与电阻r37的一端电性连接,所述运算芯片一侧的输出端与电阻r42的一端电性连接,所述电阻r42的另一端与电阻r37的另一端电性连接,所述电阻r37的另一端与运算芯片底部的输入端电性连接,所述电阻r37的另一端还连接有地线,所述运算芯片顶部的输出端接有+15v电压且和电容c28的一端电性连接,所述电容c28的另一端与电容c29的一端电性连接,所述电容c29的一端与另一端电性连接且接有地线。

12.优选的,所述环路滤波调节电路pf1包括低通滤波lpf和pi调节器,所述低通滤波lpf的输入端与占空比输出的输出端电性连接,所述低通滤波lpf的输出端与pi调节器的输入端电性连接,所述pi调节器的输出端与压控振荡输入vco模块的输入端电性连接。

13.优选的,所述低通滤波lpf的电路结构包括电阻r31和电容c32,所述pi调节器的电路结构包括电阻r32、电容c26、电阻r19、运放芯片u7a和可调电阻r40,所述电阻r31的一端与占空比输出的输出端电性连接,所述电阻r31的另一端分别与电容c32的一端和电阻r32的一端电性连接,所述电容c32的另一端接有地线,所述电阻r32的另一端与运放芯片u7a的2引脚电性连接,所述电阻r32的另一端与电容c26的一端电性连接,所述电容c26的另一端与电阻r19的一端电性连接,所述电阻r19的另一端与运放芯片u7a的1引脚电性连接,所述运放芯片u7a的1引脚与压控振荡输入vco模块的输入端电性连接,所述运放芯片u7a的3引脚与可调电阻r40的一端电性连接,所述可调电阻r40的另一端分别接有+15v电压和地线,所述运放芯片u7a的4引脚接有地线,所述运放芯片u7a的8引脚接有+15v电压且所述运放芯片u7a的8引脚和电容c30的一端电性连接,所述电容c30的一端与另一端分别和电容c31的

一端与另一端连接且电容c31的另一端接有地线。

14.优选的,所述驱动控制电路ofd1包括互补信号输出模块,所述互补信号输出模块的输入端与调频输出模块的输出端电性连接,所述互补信号输出模块的输出端分别与驱动器d1的输入端和驱动器d2的输入端电性连接,所述驱动器d1包括驱动g1和驱动g2,所述驱动器d2包括驱动g3和驱动g4,所述驱动g1的输入端与驱动g2的输入端电性连接,所述g1的输出端和g2的输出端均与谐振回路电压ulc的输入端电性连接,所述驱动g3的输入端与驱动g4的输入端电性连接,所述驱动g3的输出端和驱动g4的输出端均与谐振电容电压uc2的输入端电性连接。

15.优选的,所述互补信号输出模块的电路结构包括与非门u10a、与非门u10b、与非门u10c,所述驱动g1、驱动g2、驱动g3和驱动g4的电路结构分别包括光纤连接h1、光纤连接h2、光纤连接h3、光纤连接h4、电阻r73、电阻r70、电容c57、电容c55、电阻r76、电阻r75、电容c63、电容c62、电阻r78、电阻r77、电容c65、电容c64、电阻r81、电阻r80、电容c67、电容c66,所述与非门u10a的3引脚与与非门u10b的5引脚电性连接,所述与非门u10a的3引脚与与非门u10b的6引脚之间连接有死区时间控制模块a,所述与非门u10a的1引脚与与非门u10c的9引脚之间连接有死区时间控制模块b,所述与非门u10a的2引脚和与非门u10c的8引脚分别与死区时间控制模块b的输入端电性连接,所述与非门u10b的7引脚与光纤连接h1的2引脚电性连接,所述光纤连接h1的1引脚与电阻r70的一端电性连接,所述电阻r70的另一端分别与电容c57的一端和电容c55的一端电性连接,所述电容c55的另一端与电容c57的另一端电性连接且电容c57的另一端连接有地线,所述电阻r70的另一端还接有+5v电压,所述电阻r73的一端与电阻r70的一端电性连接,所述电阻r73的另一端与电阻r70的另一端电性连接,所述与非门u10b的7引脚还与光纤连接h2的2引脚电性连接,所述光纤连接h2的1引脚与电阻r76的一端电性连接,所述电阻r76的另一端连接有+5v电压,所述电阻r75的一端与电阻r76的一端电性连接,所述电阻r75的另一端与电阻r76的另一端电性连接,所述电容c63的一端与电阻r76的另一端电性连接,所述电容c63的另一端接有地线,所述电容c62的一端与电容c63的一端电性连接,所述电容c62的另一端与电容c63的另一端电性连接;所述与非门u10c的10引脚与光纤连接h3的2引脚电性连接,所述光纤连接h3的1引脚与电阻r77的一端电性连接,所述电阻r77的另一端接有+5v电压,所述电阻r78的一端与电阻r77的一端电性连接,所述电阻r78的另一端与电阻r77的一端电性连接,所述电阻r77的另一端分别与电容c65的一端和电容c64的一端电性连接,所述电容c64的另一端与电容c65的另一端电性连接且电容c65的另一端接有地线,所述与非门u10c的10引脚还与光纤连接h4的2引脚电性连接,所述光纤连接h4的1引脚与电阻r81的一端电性连接,所述电阻r81的另一端接有+5v电压,所述电阻r81的另一端分部与电容c67的一端和电容c66的一端电性连接,所述电容c66的一端与电容c67的一端电性连接,所述电容c66的另一端与电容c67的另一端电性连接且电容c67的另一端接有地线。

16.优选的,所述死区时间控制模块a的电路结构包括电阻r50、电容c80和电容c81,所述电阻r50的一端与与非门u10a的3引脚电性连接,所述电阻r50的另一端分别与电容c80的一端和电容c81的一端电性连接,所述电容c80的另一端与电容c81的另一端电性连接且所述电容c81的另一端接有地线,所述电容r50的另一端与与非门u10b的6引脚电性连接,所述死区时间控制模块b的电路结构包括电阻r50、电容c82和电容c83,所述电阻r50的一端与与

非门u10a的1引脚电性连接,所述电阻r50的另一端分别与电容c82的一端和电容c83的一端电性连接,所述电容c82的另一端与电容c83的另一端电性连接且电容c83的另一端接有地线,所述电阻r50的另一端与与非门u10c的9引脚电性连接。

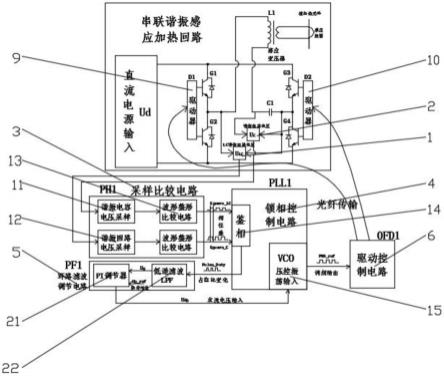

17.如图1所示,采样比较电路ph1,通过两路非隔离全差分放大电路将谐振回路电压ulc和谐振电容电压uc线性缩小,并通过比较电路整形成方波square_lc、square_c,然后将两路方波信号输入锁相控制电路pll1的鉴相模块,经过电路的异或运算,输出占空比随相位变化的方波信号pulse_duty;将此占空比方波信号通过环路滤波调节电路pf1的低通滤波电路lpf整形成直流电压信号up,用于表示当前的相位差值,再将up作为pi调节器的输入信号,与参考电压up_ref(参考相位)进行闭环控制调节后,使输出电压udp趋向up_ref值。然后将udp电压值输入压控振荡器vco,经电路运算后形成对应频率的pwm信号,为驱动控制电路提供参考频率,最后通过驱动控制电路调制成两路带死区的互补驱动信号,通过光纤传输驱动四个电子开关g1~g4,使lc串联回路产生交变电流。从而形成闭环锁相控制。

18.本实用新型提供了一种串联谐振感应加热锁相驱动电路,具备以下有益效果:

19.该一种串联谐振感应加热锁相驱动电路,同现有技术相比,可直接回避电压电流信号的鉴相不足,直接采用谐振回路电压和电容电压为鉴相输入信号,简化了采样输入电路,并通过模数电路完成信号的鉴相、滤波、相位调节、压控振荡输出等闭环控制,提高了锁相的稳定性和可靠性。

附图说明

20.图1串联谐振感应加热锁相驱动电路结构框图;

21.图2为采样比较电路原理图;

22.图3 为锁相控制电路原理图;

23.图4环路滤波调节电路原理图;

24.图5驱动控制电路原理图。

具体实施方式

25.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。

26.请参阅图1至图5,本实用新型提供一种技术方案:一种串联谐振感应加热锁相驱动电路,包括位于串联谐振感应加热回路中的谐振回路电压ulc1、谐振电容电压uc2、驱动器d19和驱动器d210、采样比较电路ph13、锁相控制电路pll14、环路滤波调节电路pf15和驱动控制电路ofd16,采样比较电路ph13包括谐振电容电压采样模块11、谐振回路电压采样模块12以及多个波形整形比较电路模块13,谐振电容电压uc2与谐振电容电压采样模块11的输入端电性连接,谐振电容电压采样模块11的输出端与其中一个波形整形比较电路模块13的输入端电性连接,谐振回路电压ulc1与谐振回路电压采样模块12的输入端电性连接,谐振回路电压采样模块12的输出端与另一个波形整形比较电路模块13的输入端电性连接,两个波形整形比较电路模块13的输出端分别得到方波输出square_lc信号和方波输出square_c信号,谐振电容电压采样模块11包括位于谐振回路电压ulc1中的排插j2,谐振回

路电压采样模块12包括位于谐振电容电压uc2中的排插j3,采样比较电路ph13的电路结构还包括电阻r21、电阻r27、电阻r41、电阻r47、电阻r18、电阻r28、电阻r38、电阻r49、电阻r24、电阻r26、电阻r45、电阻r48、电阻r34、电阻r51、电阻r30、电阻r50、电阻r35、电阻r52、运放芯片u4c、运放芯片u4d、运放芯片u5a、运放芯片u5b,排插j2的1引脚与电阻r21的一端电性连接,电阻r21的另一端分别与运放芯片u4c的9引脚和电阻r18的一端电性连接,电阻r18的另一端与运放芯片u4c的8引脚电性连接,排插j2的2引脚与电阻r27的一端电性连接,r27的另一端分别与运放芯片u4c的10引脚和电阻r28的一端电性连接,电阻r28的另一端接有参考数值电压vref-2500,运放芯片u4c的8引脚与电阻24的一端电性连接,电阻r24的另一端与运放芯片u5a的2引脚电性连接,运放芯片u5a的3引脚分别与电阻r26的一端和电阻r34的一端电性连接,r26的另一端接有参考数值电压vref-2500,电阻r34的另一端分别与电阻r30的一端和电阻r35的一端电性连接,电阻r30的另一端连接有+15v电压,运放芯片u5a的4引脚连接有地线,运放芯片u5a的8引脚分别连接有+15电压和电容c24,电容24的一端连接有电容c25,电容c25的一端与另一端电性连接且接有地线;排插j3的1引脚与电阻r41的一端电性连接,电阻r41的另一端分别与运放芯片u4d的13引脚和电阻r38的一端电性连接,电阻r38的另一端与运放芯片u4d的14引脚电性连接,排插j3的2引脚与电阻r47的一端电性连接,电阻r47的另一端分别与电阻r49的一端和运放芯片u4d的12引脚电性连接,电阻r49的另一端接有参考数值电压vref-2500,运放芯片u4d的14引脚与电阻r45的一端电性连接,电阻r45的另一端与运放芯片u5b的6引脚电性连接,运放芯片u5b的5引脚分别与电阻r48的一端和电阻r51的一端电性连接,电阻r48的另一端接有参考数值电压vref-2500,运放芯片u5b的7引脚与电阻r51的另一端电性连接,电阻r51的另一端分别与电阻r50的一端和电阻r52的一端电性连接,电阻r50的另一端接有+15v电压,锁相控制电路pll14包括鉴相模块14和压控振荡输入vco模块15,两个波形整形比较电路模块13的输出端与鉴相模块14的输入端电性连接,鉴相模块14的输出端与环路滤波调节电路pf15的输入端电性连接,路滤波调节电路pf15的输出端与压控振荡输入vco模块15的输入端电性连接,压控振荡输入vco模块15的输出端调频输出得到pwm_ref信号,鉴相模块14的电路结构包括用于接收方波输出square_lc信号和方波输出square_c信号的鉴相输入16、运算芯片17、占空比输出18、压控振荡电压输入19、电容c28、电容c29、电阻r37、电阻r42、电阻r33和调频输出模块20,鉴相输入16与运算芯片17一侧的输入端电性连接,运算芯片17另一侧的输出端与占空比输出18的输入端电性连接,运算芯片17另一侧的输入端与压控振荡电压输入19的输出端电性连接,运算芯片17一侧的输出端与电阻r33的一端电性连接,电阻r33的另一端与调频输出模块20的输入端电性连接,运算芯片17一侧的输出端与电容c33的一端电性连接,电容c33的另一端与运算芯片17一侧的输入端电性连接,运算芯片17一侧的输出端与电阻r37的一端电性连接,运算芯片17一侧的输出端与电阻r42的一端电性连接,电阻r42的另一端与电阻r37的另一端电性连接,电阻r37的另一端与运算芯片17底部的输入端电性连接,电阻r37的另一端还连接有地线,运算芯片17顶部的输出端接有+15v电压且和电容c28的一端电性连接,电容c28的另一端与电容c29的一端电性连接,电容c29的一端与另一端电性连接且接有地线,环路滤波调节电路pf15包括低通滤波lpf21和pi调节器22,低通滤波lpf21的输入端与占空比输出18的输出端电性连接,低通滤波lpf21的输出端与pi调节器22的输入端电性连接,pi调节器22的输出端与压控振荡输入vco模块15的输入端电性连接,低通滤波lpf21

的电路结构包括电阻r31和电容c32,pi调节器22的电路结构包括电阻r32、电容c26、电阻r19、运放芯片u7a和可调电阻r40,电阻r31的一端与占空比输出18的输出端电性连接,电阻r31的另一端分别与电容c32的一端和电阻r32的一端电性连接,电容c32的另一端接有地线,电阻r32的另一端与运放芯片u7a的2引脚电性连接,电阻r32的另一端与电容c26的一端电性连接,电容c26的另一端与电阻r19的一端电性连接,电阻r19的另一端与运放芯片u7a的1引脚电性连接,运放芯片u7a的1引脚与压控振荡输入vco模块15的输入端电性连接,运放芯片u7a的3引脚与可调电阻r40的一端电性连接,可调电阻r40的另一端分别接有+15v电压和地线,运放芯片u7a的4引脚接有地线,运放芯片u7a的8引脚接有+15v电压且和运放芯片u7a的8引脚和电容c30的一端电性连接,电容c30的一端与另一端分别和电容c31的一端与另一端连接且电容c31的另一端接有地线,驱动控制电路ofd16包括互补信号输出模块23,互补信号输出模块23的输入端与调频输出模块20的输出端电性连接,互补信号输出模块23的输出端分别与驱动器d19的输入端和驱动器d210的输入端电性连接,驱动器d19包括驱动g1和驱动g2,驱动器d210包括驱动g3和驱动g4,驱动g1的输入端与驱动g2的输入端电性连接,g1的输出端和g2的输出端均与谐振回路电压ulc1的输入端电性连接,驱动g3的输入端与驱动g4的输入端电性连接,驱动g3的输出端和驱动g4的输出端均与谐振电容电压uc2的输入端电性连接,互补信号输出模块23的电路结构包括与非门u10a、与非门u10b、与非门u10c,驱动g1、驱动g2、驱动g3和驱动g4的电路结构分别包括光纤连接h1、光纤连接h2、光纤连接h3、光纤连接h4、电阻r73、电阻r70、电容c57、电容c55、电阻r76、电阻r75、电容c63、电容c62、电阻r78、电阻r77、电容c65、电容c64、电阻r81、电阻r80、电容c67、电容c66,与非门u10a的3引脚与与非门u10b的5引脚电性连接,与非门u10a的3引脚与与非门u10b的6引脚之间连接有死区时间控制模块a24,与非门u10a的1引脚与与非门u10c的9引脚之间连接有死区时间控制模块b25,与非门u10a的2引脚和与非门u10c的8引脚分别与死区时间控制模块b25的输入端电性连接,与非门u10b的7引脚与光纤连接h1的2引脚电性连接,光纤连接h1的1引脚与电阻r70的一端电性连接,电阻r70的另一端分别与电容c57的一端和电容c55的一端电性连接,电容c55的另一端与电容c57的另一端电性连接且电容c57的另一端连接有地线,电阻r70的另一端还接有+5v电压,电阻r73的一端与电阻r70的一端电性连接,电阻r73的另一端与电阻r70的另一端电性连接,与非门u10b的7引脚还与光纤连接h2的2引脚电性连接,光纤连接h2的1引脚与电阻r76的一端电性连接,电阻r76的另一端连接有+5v电压,电阻r75的一端与电阻r76的一端电性连接,电阻r75的另一端与电阻r76的另一端电性连接,电容c63的一端与电阻r76的另一端电性连接,电容c63的另一端接有地线,电容c62的一端与电容c63的一端电性连接,电容c62的另一端与电容c63的另一端电性连接;与非门u10c的10引脚与光纤连接h3的2引脚电性连接,光纤连接h3的1引脚与电阻r77的一端电性连接,电阻r77的另一端接有+5v电压,电阻r78的一端与电阻r77的一端电性连接,电阻r78的另一端与电阻r77的一端电性连接,电阻r77的另一端分别与电容c65的一端和电容c64的一端电性连接,电容c64的另一端与电容c65的另一端电性连接且电容c65的另一端接有地线,与非门u10c的10引脚还与光纤连接h4的2引脚电性连接,光纤连接h4的1引脚与电阻r81的一端电性连接,电阻r81的另一端接有+5v电压,电阻r81的另一端分部与电容c67的一端和电容c66的一端电性连接,电容c66的一端与电容c67的一端电性连接,电容c66的另一端与电容c67的另一端电性连接且电容c67的另一端接有地线,死区时间控制模块a24的电路

结构包括电阻r50、电容c80和电容c81,电阻r50的一端与与非门u10a的3引脚电性连接,电阻r50的另一端分别与电容c80的一端和电容c81的一端电性连接,电容c80的另一端与电容c81的另一端电性连接且电容c81的另一端接有地线,电容r50的另一端与与非门u10b的6引脚电性连接,死区时间控制模块b25的电路结构包括电阻r50、电容c82和电容c83,电阻r50的一端与与非门u10a的1引脚电性连接,电阻r50的另一端分别与电容c82的一端和电容c83的一端电性连接,电容c82的另一端与电容c83的另一端电性连接且电容c83的另一端接有地线,电阻r50的另一端与与非门u10c的9引脚电性连接,谐振回路电压ulc1的输出端和谐振电容电压uc2的输出端分别与采样比较电路ph13的输入端电性连接,采样比较电路ph13输出端与锁相控制电路pll14中的其中一个输入端电性连接,锁相控制电路pll14中的其中一个输出端与环路滤波调节电路pf16的输入端电性连接,环路滤波调节电路pf16的输出端与锁相控制电路pll14中的另一个输入端电性连接,锁相控制电路pll14的另一个输出端与驱动控制电路ofd16的输入端电性连接,驱动控制电路ofd16的输出端分别与驱动器d19与和驱动器d210的输入端电性连接。

27.在本说明书的描述中,术语“连接”、“安装”、“固定”、“设置”等均做广义理解,例如,“连接”可以是固定连接或在不影响部件关系与技术效果的基础上通过中间组件间接进行,也可以是一体连接或部分连接,如同此例的情形对于本领域普通技术人员而言,可根据具体情况理解上述术语在本实用新型或实用新型中的具体含义。

28.以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,根据本实用新型的技术方案及其实用新型构思加以等同替换或改变,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1