晶闸管的抗干扰电路的制作方法

1.本实用新型涉及晶闸管的抗干扰电路。

背景技术:

2.由于晶闸管开关的外部输入信号易受干扰信号的影响,造成开关工作不稳定,同时由于疫情的影响造成了当前全球供应链危机,尤其芯片的供应紧张,mcu的价格大幅度提高,因此尽量避免使用mcu,可以大大降低成本。

技术实现要素:

3.本实用新型的目的是克服现有技术中的不足,提供晶闸管的抗干扰电路。

4.为了达到上述目的,本实用新型是通过以下技术方案实现的:

5.晶闸管的抗干扰电路,包括三个晶闸管触发模块、输出电路,所述三个晶闸管触发模块都连接输出电路,所述输出电路包括隔离模块、整形模块、采样锁存输出模块,所述隔离模块通过整形模块连接采样锁存输出模块。

6.作为优选,隔离模块包括光耦u302、光耦u307、光耦u313、电阻r342、电阻r343、电阻r347、电阻r348、电阻r349、电阻r362、电源vcc,所述光耦u302的1管脚通过电阻r342连接12v,所述光耦u302的2管脚为第一外部输入控制信号,所述光耦u302的3管脚连接地信号gnd,所述光耦u302的4管脚通过电阻r343连接电源vcc,所述光耦u307的1管脚通过电阻r347连接12v,所述光耦u307的2管脚为第二外部输入控制信号,所述光耦u307的3管脚连接地信号gnd,所述光耦u307的4管脚通过电阻r349连接电源vcc,所述光耦u313的1管脚通过电阻r348连接12v,所述光耦u313的2管脚为第三外部输入控制信号,所述光耦u313的3管脚连接地信号gnd,所述光耦u313的4管脚通过电阻r362连接电源vcc,所述光耦u302的4管脚、光耦u307的4管脚、光耦u313的4管脚用于连接整形模块。

7.作为优选,整形模块包括74hc14施密特芯片u2d、74hc14施密特芯片u2e、74hc14施密特芯片u2f、电阻r18,所述电阻r18的一端连接74hc14施密特芯片u2d的输入端,所述电阻r18的另一端连接74hc14施密特芯片u2f的输入端,所述74hc14施密特芯片u2d的输入端连接光耦u302的4管脚,所述74hc14施密特芯片u2e的输入端连接光耦u307的4管脚,所述74hc14施密特芯片u2f的输入端连接光耦u313的4管脚,所述74hc14施密特芯片u2d的输出端、74hc14施密特芯片u2e的输出端、74hc14施密特芯片u2f的输出端用于连接采样锁存输出模块。

8.作为优选,采样锁存输出模块包括74hc174 d触发器u4、电容c11、电容c12、电阻r13、电源vcc,所述74hc14施密特芯片u2d的输出端连接74hc174 d触发器u4的6管脚,所述74hc14施密特芯片u2e的输出端连接74hc174 d触发器u4的4管脚,所述74hc14施密特芯片u2f的输出端连接74hc174 d触发器u4的3管脚,所述74hc174 d触发器u4的8管脚连接地信号gnd,所述74hc174 d触发器u4的1管脚通过电容c11连接地信号gnd,所述74hc174 d触发器u4的1管脚通过电阻r13连接电源vcc,所述74hc174 d触发器u4的16管脚通过电容c12连

接地信号gnd,所述74hc174 d触发器u4的16管脚连接电源vcc,所述74hc174 d触发器u4的2管脚、5管脚、7管脚都用于连接晶闸管触发模块,所述74hc174 d触发器u4的11管脚、13管脚、14管脚连接都地信号gnd,所述74hc174 d触发器u4的9管脚输入同步时钟信号clk。

9.作为优选,晶闸管触发模块包括电阻r16、电阻r17、电阻r360、电阻r361、电阻r382、电阻r383、电阻r384、电阻r385、三极管q3、二极管d313、二极管d322、晶闸管t、moc3081芯片u311、moc3081芯片u314,所述电阻r16的一端用于连接采样锁存输出模块,所述电阻r16的另一端连接三极管q3的基极,所述三极管q3的基极通过电阻r17连接三极管q3的发射极,所述三极管q3的发射极连接地信号gnd,所述三极管q3的集电极输入led灯控制信号,所述三极管q3的集电极通过电阻r382连接moc3081芯片u314的2管脚,所述moc3081芯片u314的1管脚连接moc3081芯片u311的2管脚,所述moc3081芯片u311的1管脚连接电源vcc,所述moc3081芯片u314的4管脚通过电阻r383连接moc3081芯片u314的6管脚,所述moc3081芯片u311的4管脚通过电阻r360连接moc3081芯片u311的6管脚,所述moc3081芯片u314的4管脚通过电阻r384连接二极管d322的负极,所述二极管d322的正极连接晶闸管t的6管脚,所述电阻r385与二极管d322相并联,所述二极管d322的负极连接晶闸管t的7管脚,所述moc3081芯片u311的6管脚连接二极管d313的负极,所述二极管d313的正极连接晶闸管t的5管脚,所述二极管d313的负极连接晶闸管t的4管脚,所述电阻r361与二极管d313相并联。

10.作为优选,电源vcc为5v。

11.本实用新型的有益效果如下:本实用新型的外部控制信号利用光耦进行隔离,同时利用74hc14施密特电路对输入边沿进行整形,再利用74hc174 d触发器的时钟边沿锁存的功能对输入信号进行采样、锁存、输出,增强电路抗外部干扰的能力,而且避免使用mcu也能实现本实用新型的功能,大大降低了成本。

附图说明

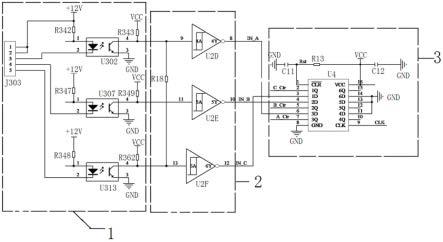

12.图1为本实用新型的输出电路的电路原理图;

13.图2为本实用新型的晶闸管触发模块的电路原理图。

具体实施方式

14.下面结合说明书附图对本实用新型的技术方案作进一步说明:

15.如图1、图2所示,晶闸管的抗干扰电路,包括三个晶闸管触发模块、输出电路,所述三个晶闸管触发模块都连接输出电路,所述输出电路包括隔离模块1、整形模块2、采样锁存输出模块3,所述隔离模块1通过整形模块2连接采样锁存输出模块3。

16.如图1所示,隔离模块1包括光耦u302、光耦u307、光耦u313、电阻r342、电阻r343、电阻r347、电阻r348、电阻r349、电阻r362、电源vcc,所述光耦u302的1管脚通过电阻r342连接12v,所述光耦u302的2管脚为第一外部输入控制信号,所述光耦u302的3管脚连接地信号gnd,所述光耦u302的4管脚通过电阻r343连接电源vcc,所述光耦u307的1管脚通过电阻r347连接12v,所述光耦u307的2管脚为第二外部输入控制信号,所述光耦u307的3管脚连接地信号gnd,所述光耦u307的4管脚通过电阻r349连接电源vcc,所述光耦u313的1管脚通过电阻r348连接12v,所述光耦u313的2管脚为第三外部输入控制信号,所述光耦u313的3管脚

连接地信号gnd,所述光耦u313的4管脚通过电阻r362连接电源vcc,所述光耦u302的4管脚、光耦u307的4管脚、光耦u313的4管脚用于连接整形模块2。

17.如图1所示,整形模块2包括74hc14施密特芯片u2d、74hc14施密特芯片u2e、74hc14施密特芯片u2f、电阻r18,所述电阻r18的一端连接74hc14施密特芯片u2d的输入端,所述电阻r18的另一端连接74hc14施密特芯片u2f的输入端,所述74hc14施密特芯片u2d的输入端连接光耦u302的4管脚,所述74hc14施密特芯片u2e的输入端连接光耦u307的4管脚,所述74hc14施密特芯片u2f的输入端连接光耦u313的4管脚,所述74hc14施密特芯片u2d的输出端、74hc14施密特芯片u2e的输出端、74hc14施密特芯片u2f的输出端用于连接采样锁存输出模块3。

18.如图1所示,采样锁存输出模块3包括74hc174 d触发器u4、电容c11、电容c12、电阻r13、电源vcc,所述74hc14施密特芯片u2d的输出端连接74hc174 d触发器u4的6管脚,所述74hc14施密特芯片u2e的输出端连接74hc174 d触发器u4的4管脚,所述74hc14施密特芯片u2f的输出端连接74hc174 d触发器u4的3管脚,所述74hc174 d触发器u4的8管脚连接地信号gnd,所述74hc174 d触发器u4的1管脚通过电容c11连接地信号gnd,所述74hc174 d触发器u4的1管脚通过电阻r13连接电源vcc,所述74hc174 d触发器u4的16管脚通过电容c12连接地信号gnd,所述74hc174 d触发器u4的16管脚连接电源vcc,所述74hc174 d触发器u4的2管脚、5管脚、7管脚都用于连接晶闸管触发模块,所述74hc174 d触发器u4的11管脚、13管脚、14管脚连接都地信号gnd,所述74hc174 d触发器u4的9管脚输入同步时钟信号clk。

19.如图2所示,晶闸管触发模块包括电阻r16、电阻r17、电阻r360、电阻r361、电阻r382、电阻r383、电阻r384、电阻r385、三极管q3、二极管d313、二极管d322、晶闸管t、moc3081芯片u311、moc3081芯片u314,所述电阻r16的一端用于连接采样锁存输出模块3,所述电阻r16的另一端连接三极管q3的基极,所述三极管q3的基极通过电阻r17连接三极管q3的发射极,所述三极管q3的发射极连接地信号gnd,所述三极管q3的集电极输入led灯控制信号,所述三极管q3的集电极通过电阻r382连接moc3081芯片u314的2管脚,所述moc3081芯片u314的1管脚连接moc3081芯片u311的2管脚,所述moc3081芯片u311的1管脚连接电源vcc,所述moc3081芯片u314的4管脚通过电阻r383连接moc3081芯片u314的6管脚,所述moc3081芯片u311的4管脚通过电阻r360连接moc3081芯片u311的6管脚,所述moc3081芯片u314的4管脚通过电阻r384连接二极管d322的负极,所述二极管d322的正极连接晶闸管t的6管脚,所述电阻r385与二极管d322相并联,所述二极管d322的负极连接晶闸管t的7管脚,所述moc3081芯片u311的6管脚连接二极管d313的负极,所述二极管d313的正极连接晶闸管t的5管脚,所述二极管d313的负极连接晶闸管t的4管脚,所述电阻r361与二极管d313相并联。

20.如图1、图2所示,电源vcc为5v。

21.第一外部输入控制信号、第二外部输入控制信号、第三外部输入控制信号是由外部控制器提供的,不需要通过单片机控制。

22.外部输入触发信号易受干扰毛刺信号影响,造成晶闸管开关的抖动从而损坏主回路器件。利用74hc174 d触发器对外部输入触发信号在同步时钟信号的边沿进行采样锁存,有效降低尖峰毛刺等干扰信号对晶闸管开关的影响。

23.本实用新型的外部控制信号利用光耦进行隔离,同时利用74hc14施密特电路对输

入边沿进行整形,再利用74hc174 d触发器的时钟边沿锁存的功能对输入信号进行采样、锁存、输出,增强电路抗外部干扰的能力,而且避免使用mcu也能实现本实用新型的功能,大大降低了成本。

24.需要注意的是,以上列举的仅是本实用新型的一种具体实施例。显然,本实用新型不限于以上实施例,还可以有许多变形,总之,本领域的普通技术人员能从本实用新型公开的内容直接导出或联想到的所有变形,均应认为是本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1