印制电路板和电子设备的制作方法

1.本技术涉及电子产品的领域,尤其涉及印制电路板和电子设备。

背景技术:

2.印制电路板是一种电子部件,能够代替复杂的布线,实现电路中各元件之间的电气连接。印制电路板的应用简化了电子设备的装配、焊接工作,并且减少了传统方式下的接线工作量。

3.印制电路板由多个沿第一方向层叠设置的芯板压合而成,在多个芯板中,其中一个芯板为第一芯板,另一芯板为第二芯板,其他芯板设置为功能芯板,在多个功能芯板中,部分功能芯板设置在第一芯板远离第二芯板的一侧,且至少一个功能芯板设置在第一芯板和第二芯板之间;在印制电路板上还设置有沿第一方向延伸的背钻孔,在第一方向上,背钻孔的第一端位于设置在第一芯板远离第二芯板一侧最外层的功能芯板,背钻孔的第二端延伸至第一芯板与第二芯板之间的功能芯板,并且在背钻孔内形成有导电层,从而能够利用背钻孔中的导电层实现设置在第一芯板远离第二芯板一侧最外层功能芯板至第一芯板之间各层芯板的连接,进而保证印制电路板的正常使用。

4.在印制电路板上形成背钻孔时,需要对印制电路板进行切片检测,从而确定背钻孔的深度。但通过切片检测确定背钻孔的深度的方法较为麻烦,导致检测背钻孔深度的效率低。

技术实现要素:

5.本技术实施例提供印制电路板和电子设备,用以解决相关技术中通过切片检测确定背钻孔的深度的方法较为麻烦,使得检测背钻孔深度的工作效率较低的问题。

6.本技术实施例提供的印制电路板,包括主体和测试部;

7.所述主体包括第一芯板、第二芯板和多个功能芯板,所述第一芯板、所述第二芯板和多个所述功能芯板沿第一方向层叠设置,所述主体上设置有背钻孔,所述背钻孔沿所述第一方向延伸;

8.所述测试部连接所述主体,且所述测试部包括第一测试板、第二测试板和多个填充板;所述第一测试板与所述第一芯板对应设置,所述第一测试板上设置有第一导电图案;所述第二测试板与所述第二芯板对应设置,所述第二测试板上设置有第二导电图案;多个所述填充板与多个所述功能芯板一一对应设置;所述测试部设置有多个深度测试孔,在所述第一方向上,所述深度测试孔的深度与所述背钻孔的深度相同,每个所述深度测试孔内均设置有第一导电层;

9.当所述深度测试孔延伸至所述第一测试板时,多个所述第一导电层通过所述第一导电图案连通;当所述深度测试孔延伸至所述第二测试板时,多个所述第一导电层通过所述第二导电图案连通。

10.通过采用上述技术方案,在主体连接测试部,从而利用测试部的第一测试板、第二

测试板和填充板分别模拟第一芯板、第二芯板和功能芯板;当需要确定背钻孔的深度时,通过多个深度测试孔进行检测,当多个深度测试孔未导通时,则背钻孔的深度较小,背钻孔未延伸至第一芯板处;当多个深度测试孔通过第一导电图案连通,并且未通过第二导电图案导通时,则背钻孔穿过第一芯板,并延伸至第一芯板与第二芯板之间;当多个深度测试孔既能够通过第一导电图案连通,并且还能够通过第二导电图案导通,则背钻孔的深度较大,背钻孔穿过第一芯板和第二芯板;从而能够利用多个深度测试孔对背钻孔的深度进行检测,从而无需通过切片检测确定背钻孔的深度,提高了检测背钻孔深度的工作效率。

11.进一步设置为,所述第一导电图案包括相连通的两个第一定位点,所述第二导电图案包括相连通的两个第二定位点;

12.所述深度测试孔的数量至少为四个,其中两个所述深度测试孔为第一深度测试孔,两个所述第一深度测试孔与两个所述第一定位点对应设置,当两个所述第一深度测试孔延伸至所述第一测试板时,两个所述第一深度测试孔中的所述第一导电层通过两个所述第一定位点连通;

13.另两个所述深度测试孔为第二深度测试孔,两个所述第二深度测试孔与两个所述第二定位点对应设置,当两个所述第二深度测试孔延伸至所述第二测试板时,两个所述第二深度测试孔中的所述第一导电层通过两个所述第二定位点连通。

14.进一步设置为,所述第一导电图案包括第一定位点,所述第二导电图案包括第二定位点;

15.所述深度测试孔包括第一深度测试孔、第二深度测试孔和第三深度测试孔,其中所述第一深度测试孔与所述第一定位点相对设置,当所述第一深度测试孔延伸至所述第一测试板时,所述第一深度测试孔中的所述第一导电层和所述第三深度测试孔中的所述第一导电层通过所述第一导电图案连通;

16.所述第二深度测试孔与所述第二定位点相对设置,当所述第二深度测试孔延伸至所述第二测试板时,所述第二深度测试孔中的所述第一导电层和所述第三深度测试孔中的所述第一导电层通过所述第二导电图案连通。

17.进一步设置为,所述测试部上还设置有至少一个偏移测试孔,在所述第一方向上,所述偏移测试孔的长度与所述背钻孔的长度相同,所述偏移测试孔内设置有第二导电层;所述第一测试板上设置有至少一个偏移测试点,且所述第一导电图案还包括至少一个环形导电部,所述环形导电部与所述第一定位点连通,且所述环形导电部与所述偏移测试孔对应设置,并环绕在相应所述偏移测试点的外侧,所述环形导电部与所述偏移测试点之间还形成有偏移间隙。

18.进一步设置为,所述偏移测试孔设置有多个,且多个所述偏移测试孔沿第二方向均匀设置。

19.进一步设置为,多个所述环形导电部沿所述第二方向均匀排布,并设置在两个所述第一定位点之间。

20.进一步设置为,在所述第二方向上,多个所述偏移测试孔共同构成测试孔组,所述测试孔组设置有多个,且多个所述测试孔组沿第三方向设置。

21.进一步设置为,所述偏移间隙设置有多个,在所述第三方向上,多个所述偏移间隙与多个所述测试孔组一一对应设置。

22.进一步设置为,所述第一测试板与所述第一芯板一体成型,所述第二测试板与所述第二芯板一体成型,所述填充板与相应的功能芯板一体成型。

23.本技术实施例还提供一种电子设备,包括上述印制电路板。

24.通过采用上述技术方案,在电子设备的印制电路板中,主体连接测试部,从而利用测试部的第一测试板、第二测试板和填充板分别模拟第一芯板、第二芯板和功能芯板;当需要确定背钻孔的深度时,通过多个深度测试孔进行检测,当多个深度测试孔未导通时,则背钻孔的深度较小,背钻孔未延伸至第一芯板处;当多个深度测试孔通过第一导电图案连通,并且未通过第二导电图案导通时,则背钻孔穿过第一芯板,并延伸至第一芯板与第二芯板之间;当多个深度测试孔既能够通过第一导电图案连通,并且还能够通过第二导电图案导通,则背钻孔的深度较大,背钻孔穿过第一芯板和第二芯板;从而能够利用多个深度测试孔对背钻孔的深度进行检测,从而无需通过切片检测确定背钻孔的深度,提高了检测背钻孔深度的工作效率。

附图说明

25.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本技术的实施例,并与说明书一起用于解释本技术的原理。

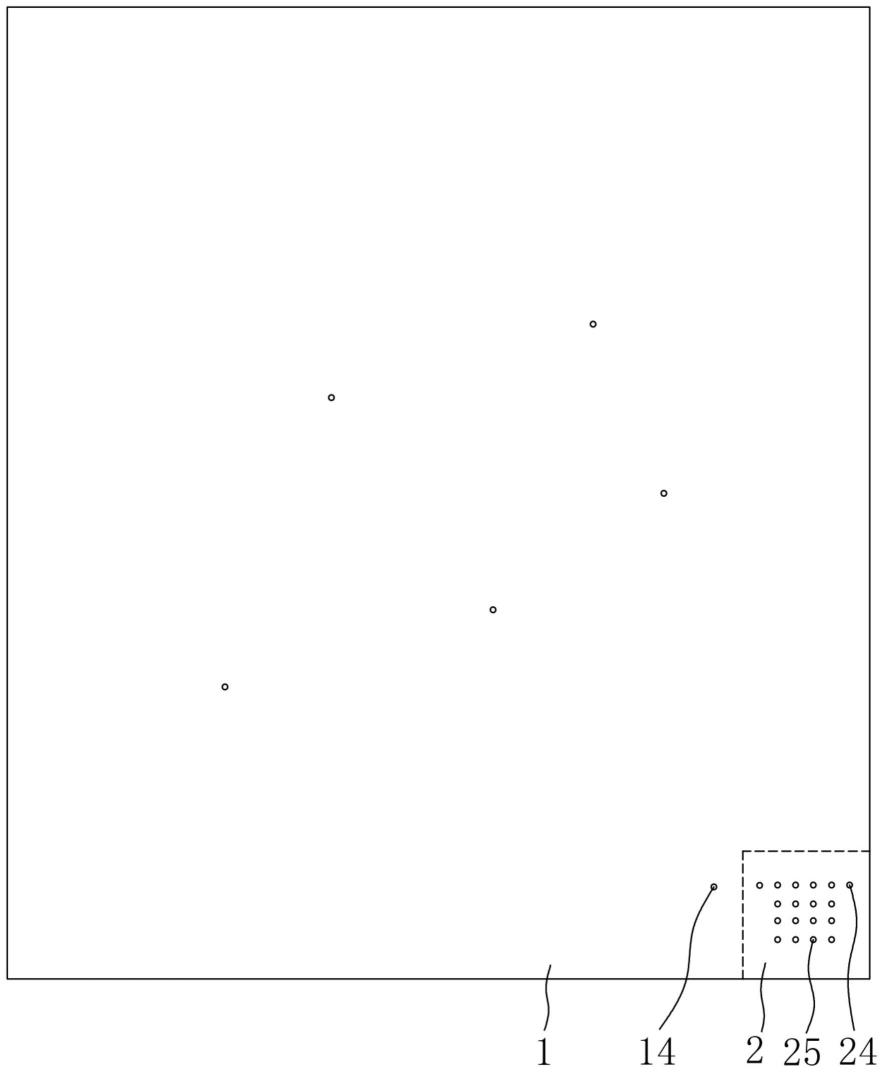

26.图1为本技术实施例提供的印制电路板的结构示意图;

27.图2为本技术实施例未形成深度测试孔时第一测试板的结构示意图;

28.图3为本技术实施例提供的未包含第三深度测试孔的第一测试板的结构示意图

29.图4为本技术实施例提供的包含第三深度测试孔的第一测试板的结构示意图;

30.图5为本技术实施例提供的未包含第三深度测试孔的第二测试板的结构示意图;

31.图6为本技术实施例提供的包含第三深度测试孔的第二测试板的结构示意图;

32.图7为本技术实施例提供的旨在显示偏移测试孔未偏移时的第一测试板的结构示意图;

33.图8为本技术实施例提供的旨在显示偏移测试孔偏移时的第一测试板的结构示意图。

34.附图标记说明:

35.1、主体;11、第一芯板;12、第二芯板;13、功能芯板;14、背钻孔;2、测试部;21、第一测试板;211、第一导电图案;2111、第一定位点;2112、环形导电部;212、偏移间隙;213、偏移测试点;22、第二测试板;221、第二导电图案;2212、第二定位点;23、填充板;24、深度测试孔;241、第一深度测试孔;242、第二深度测试孔;243、第三深度测试孔;244、第一导电层;25、偏移测试孔;251、第二导电层。

36.通过上述附图,已示出本技术明确的实施例,后文中将有更详细的描述。这些附图和文字描述并不是为了通过任何方式限制本技术构思的范围,而是通过参考特定实施例为本领域技术人员说明本技术的概念。

具体实施方式

37.正如背景技术所述,印制电路板上设置有背钻孔,并且在背钻孔内形成有第一导电层,从而能够利用背钻孔中的第一导电层实现最外层芯板至第一芯板之间各层芯板的连

接。但是在印制电路板上形成背钻孔时,需要对印制电路板进行切片检测,从而确定背钻孔的深度。但通过切片检测确定背钻孔的深度时,不仅需要切下部分印制电路板形成切片,还需要对切片进行切割和多次研磨,从而确定背钻孔的深度,进而使通过切片检测确定背钻孔的深度的方法较为麻烦,使得形成背钻孔的工作效率较低。

38.为了解决上述技术问题,本技术实施例提供一种印制电路板和电子设备,印制电路板包括主体和测试部,从而利用测试部的第一测试板、第二测试板和填充板分别模拟第一芯板、第二芯板和功能芯板,并且通过深度测试孔模拟背钻孔,从而只需要对测试板上深度测试孔的深度进行检测,即能够通过测试部得到主体上背钻孔的深度。

39.当需要确定背钻孔的深度时,通过多个深度测试孔进行检测,当多个深度测试孔未导通时,则背钻孔的深度较小,背钻孔未延伸至第一芯板处;当多个深度测试孔通过第一导电图案连通,并且未通过第二导电图案导通时,则背钻孔穿过第一芯板,并延伸至第一芯板与第二芯板之间;当多个深度测试孔既能够通过第一导电图案连通,并且还能够通过第二导电图案导通,则背钻孔的深度较大,背钻孔穿过第一芯板和第二芯板;从而能够利用多个深度测试孔对背钻孔的深度进行检测,从而无需通过切片检测确定背钻孔的深度,提高了形成背钻孔的工作效率。

40.这里将详细地对示例性实施例进行说明,其示例表示在附图中。下面的描述涉及附图时,除非另有表示,不同附图中的相同数字表示相同或相似的要素。以下示例性实施例中所描述的实施方式并不代表与本技术相一致的所有实施方式。相反,它们仅是与如所附权利要求书中所详述的、本技术的一些方面相一致的装置和方法的例子。

41.下面以具体地实施例对本技术的技术方案以及本技术的技术方案如何解决上述技术问题进行详细说明。下面这几个具体的实施例可以相互结合,对于相同或相似的概念或过程可能在某些实施例中不再赘述。下面将结合附图,对本技术的实施例进行描述。

42.参照图1-图8,本技术实施例提供一种印制电路板,包括主体1和测试部2;其中,主体1包括第一芯板11、第二芯板12和多个功能芯板13,第一芯板11、第二芯板12和多个功能芯板13沿第一方向层叠设置,主体1上设置有背钻孔14。并且容易理解的是,第一芯板11、第二芯板12和多个功能芯板13的排布顺序需要根据实际情况进行调整,例如第一芯板11可以设置在主体1的第六层,第二芯板12设置在主体1的第八层,此时在第一芯板11和第二芯板12之间设置有一个功能芯板13,则当背钻孔14穿过第一芯板11,并延伸至第一芯板11和第二芯板12之间的功能芯板13处时,则背钻孔14的深度处于正常状态;当背钻孔14未延伸至第一芯板11处时,则背钻孔14的深度较小;背钻孔14穿过第一芯板11和第二芯板12时,则背钻孔14的深度较大。

43.下面对测试部2的结构进行描述,示例性的,参照图1-图8,测试部2连接主体1,且测试部2包括第一测试板21、第二测试板22和多个填充板23;第一测试板21与第一芯板11对应设置,第一测试板21上设置有第一导电图案211;第二测试板22与第二芯板12对应设置,第二测试板22上设置有第二导电图案221;多个填充板23与多个功能芯板13一一对应设置;测试部2设置有多个深度测试孔24,深度测试孔24内设置有第一导电层244,第一导电层244用于连通第一导电图案211和/或第二导电图案221,在第一方向上,深度测试孔24的长度与背钻孔14的长度相同,从而能够利用深度测试孔24模拟背钻孔14。当深度测试孔24延伸至第一测试板21时,多个第一导电层244通过第一导电图案211连通;当深度测试孔24延伸至

第二测试板22时,多个第一导电层244通过第二导电图案221连通。

44.并且在本技术实施例中,第一测试板21与第一芯板11一体成型,第二测试板22与第二芯板12一体成型,填充板23与相应的功能芯板13一体成型,从而能够利用测试部2模拟主体1的结构,进而保证背钻孔14深度测试过程的准确性。

45.容易理解的是,在本技术实施例中,可以利用多种方式通过多个深度测试孔24实现对背钻孔14深度的测试。

46.参照图1-图4,示例性,在第一测试板21上,第一导电图案211包括相连通的两个第一定位点2111,在第二测试板22上,第二导电图案221包括相连通的两个第二定位点2212;深度测试孔24的数量至少为四个,并且四个深度测试孔24错位设置,其中两个深度测试孔24为第一深度测试孔241,两个第一深度测试孔241与两个第一定位点2111对应设置,当两个第一深度测试孔241延伸至第一测试板21时,两个第一深度测试孔241中的第一导电层244通过两个第一定位点2111连通;另两个深度测试孔24为第二深度测试孔242,两个第二深度测试孔242与两个第二定位点2212对应设置,当两个第二深度测试孔242延伸至第二测试板22时,两个第二深度测试孔242中的第一导电层244通过两个第二定位点2212连通。

47.应当注意的是,在本技术实施例中,第一导电图案211和第二导电图案221的形状和形成方式,本技术实施例对此不作限制,至于第一定位点2111在第一导电图案211的位置、第二定位点2212在第二导电图案221的位置可以有多种方式实现,只要能够保证两个第一定位点2111的连通状态、两个第二定位点2212的连通状态,以及当深度测试孔24从第一定位点2111或第二定位点2212上穿过时,深度测试孔24内的第一导电层244能够与第一定位点2111或者第二定位点2212连通即可。

48.通过采用上述技术方案,当利用多个深度测试孔24对背钻孔14的深度进行检测时,将检测装置的两个连接柱与两个第一深度测试孔241一一对应设置,并分别插入相对应的第一深度测试孔241中,若两个连接柱未连通,则第一深度测试孔241未穿过第一测试板21,即表示背钻孔14未穿过第一芯板11;若两个连接柱连通,则第一深度测试孔241穿过第一测试板21,从而能够利用第一导电图案211和第一深度测试孔241的第一导电层244将两个连接柱连通,即表示背钻孔14穿过第一芯板11。

49.随后将检测装置的两个连接柱与两个第二深度测试孔242一一对应设置,并分别插入相对应的第二深度测试孔242中,若两个连接柱未连通,则第二深度测试孔242未穿过第二测试板22,即表示背钻孔14未穿过第二芯板12;若两个连接柱连通,则第二深度测试孔242穿过第二测试板22,从而能够利用第二导电图案221和第二深度测试孔242的第一导电层244将两个连接柱连通,即表示背钻孔14穿过第二芯板12,进而完成背钻孔14深度的检测过程。

50.容易理解的是,在本技术实施例中,检测装置可以选用多种结构形成,例如检测装置可以选用万用表,从而将万用表的表笔连接在两个第一深度测试孔241或者两个第二深度测试孔242处;或者,检测装置还可以选用功能电路,将两个第一深度测试孔241或者两个第二深度测试孔242接入功能电路中,从而能够通过功能电路的通断状态确定深度测试孔24的深度。

51.或者,还可以将测试部2设置为如下结构,从而能够通过多个深度测试孔24实现对背钻孔14深度的测试。

52.参照图1-图6,示例性的,在第一测试板21上,第一导电图案211包括第一定位点2111,在第二测试板22上,第二导电图案221包括第二定位点2212;深度测试孔24包括第一深度测试孔241、第二深度测试孔242和第三深度测试孔243,其中第一深度测试孔241与第一定位点2111相对设置,当第一深度测试孔241延伸至第一测试板21时,第一深度测试孔241中的第一导电层244和第三深度测试孔243中的第一导电层244通过第一导电图案211连通;第二深度测试孔242与第二定位点2212相对设置,当第二深度测试孔242延伸至第二测试板22时,第二深度测试孔242中的第一导电层244和第三深度测试孔243中的第一导电层244通过第二导电图案221连通。

53.通过采用上述技术方案,当利用多个深度测试孔24对背钻孔14的深度进行检测时,将检测装置的两个连接柱其中一个放置在第一深度测试孔241内,另一个放置在第二深度测试孔242内,若两个连接柱未连通,则第一深度测试孔241未穿过第一测试板21,即表示背钻孔14未穿过第一芯板11;若两个连接柱连通,则第一深度测试孔241穿过第一测试板21,从而能够利用第一导电图案211、第一深度测试孔241的第一导电层244和第二深度测试孔242的第一导电层244将两个连接柱连通,即表示背钻孔14穿过第一芯板11。

54.随后将检测装置的两个连接柱其中一个放置在第二深度测试孔242内,另一个保持在第二深度测试孔242内,若两个连接柱未连通,则第二深度测试孔242未穿过第二测试板22,即表示背钻孔14未穿过第二芯板12;若两个连接柱连通,则第二深度测试孔242穿过第二测试板22,从而能够利用第二导电图案221、第二深度测试孔242的第一导电层244和第三深度测试孔243的第一导电层244将两个连接柱连通,即表示背钻孔14穿过第二芯板12,进而完成背钻孔14深度的检测过程。

55.容易理解的是,当制备印制电路板时,将第一芯板11、第二芯板12和多个功能芯板13沿第一方向层叠设置,并利用半固化片将第一芯板11、第二芯板12和多个功能芯板13固定,从而压合形成印制电路板的主体1。但在印制电路板的制备过程中,第一芯板11、第二芯板12和多个功能芯板13之间可能出现相对偏移,使得背钻孔14与第一芯板11、第二芯板12和多个功能芯板13之间的位置关系改变,从而影响印制电路板的正常使用。

56.所以在本技术实施例中,继续参照图1-图8,测试部2上还设置有至少一个偏移测试孔25,在第一方向上,偏移测试孔25的长度与背钻孔14的长度相同,且偏移测试孔25内设置有第二导电层251,从而能够利用偏移测试孔25模拟背钻孔14,第一测试板21上设置有至少一个偏移测试点213,且第一导电图案211还包括至少一个环形导电部2112,环形导电部2112与第一定位点2111连通,且环形导电部2112与偏移测试孔25对应设置,并环绕在相应偏移测试点213的外侧,环形导电部2112与偏移测试点213之间还形成有偏移间隙212,从而能够利用偏移测试孔25、偏移测试点213和环形导电部2112对印制电路板层间的偏移量进行检测。

57.应当注意的是,在本技术实施例中,环形导电部2112应当保持一定的宽度,从而避免印制电路板的偏移量较大时,偏移测试孔25完全设置在相对应的环形导电部2112的外侧,而未与环形导电部2112接触,进而对印制电路板偏移量的确定过程产生影响。并且偏移间隙212指环形导电部2112与偏移测试点213之间的距离与偏移测试孔25半径之差,从而保证印制电路板偏移量测试的准确性。

58.当利用偏移测试孔25对印制电路板的偏移量进行检测时,将检测装置的两个连接

柱其中一个放置在第一深度测试孔241内,另一个放置在偏移测试孔25内,当第一芯板11与相邻的功能芯板13之间未出现偏移时,在测试部2上,偏移测试孔25穿过第一测试板21时,偏移测试孔25与偏移测试点213相对应,并穿过偏移测试点213,第二导电层251未与环形导电部2112相接触,则检测装置两个连接柱之间未连通。

59.参照图5-图8,当第一芯板11与相邻的功能芯板13之间出现偏移,且偏移量小于偏移间隙212时,在测试部2上,偏移测试孔25穿过第一测试板21时,偏移测试孔25偏离偏移测试点213,并处于环形导电部2112的内侧,第二导电层251未与环形导电部2112相接触,则检测装置两个连接柱之间未连通。

60.当第一芯板11与相邻的功能芯板13之间出现偏移,且偏移量大于或等于偏移间隙212时,在测试部2上,偏移测试孔25穿过第一测试板21时,偏移测试孔25偏离偏移测试点213,第二导电层251与环形导电部2112连通,则检测装置两个连接柱之间通过第一导电层244、第二导电层251和导电图案连通,从而确定印制电路板的偏移量。

61.在本技术实施例中,偏移测试孔25设置有多个,且多个偏移测试孔25沿第二方向均匀设置,从而能够使确定印制电路板偏移量的过程更加准确,并且还能够将检测装置的两个连接柱与两个偏移测试孔25对应,并分别放置在对应的偏移测试孔25内,从而使印制电路板偏移量的确定过程更加方便。在第一导电图案211中,多个环形导电部2112沿第二方向均匀排布,并设置在两个第一定位点2111之间。

62.在第二方向上,多个偏移测试孔25共同构成测试孔组,测试孔组设置有多个,且多个测试孔组沿第三方向设置。而偏移间隙212设置有多个,在第三方向上,多个偏移间隙212与多个测试孔组一一对应设置,从而能够利用多个偏移间隙212使得印制电路板偏移量的确定更加准确。

63.容易理解的是,当偏移间隙212设置为多个时,例如偏移间隙212设置为2mil,3mil,4mil等,从而能够使得印制电路板偏移量确定在某个范围内。

64.继续参照图5-图8,下面以测试孔组设置为四个,并分别命名为第一测试孔组、第二测试孔组、第三测试孔组和第四测试孔组,且第一测试孔组、第二测试孔组、第三测试孔组和第四测试孔组的偏移间隙212分别设置为2mil、3mil、4mil和5mil为例,对印制电路板偏移量的确定过程进行描述,具体确定过程如下:

65.将检测装置的两个连接柱其中一个放置在第一深度测试孔241内,另一个放置在第一测试孔组的偏移测试孔25内,若检测装置两个连接柱之间未连通,则印制电路板的偏移量小于2mil;

66.若检测装置两个连接柱之间连通,则将检测装置的两个连接柱其中一个放置在第二测试孔组的偏移测试孔25内,另一个保持在第一深度测试孔241内,若检测装置两个连接柱之间未连通,则印制电路板的偏移量大于或等于2mil,并小于3mil;

67.若检测装置两个连接柱之间依然连通,则将检测装置的两个连接柱其中一个放置在第三测试孔组的偏移测试孔25内,另一个保持在第一深度测试孔241内,若检测装置两个连接柱之间未连通,则印制电路板的偏移量大于或等于3mil,并小于4mil;

68.若检测装置两个连接柱之间依然连通,则将检测装置的两个连接柱其中一个放置在第四测试孔组的偏移测试孔25内,另一个保持在第一深度测试孔241内,若检测装置两个连接柱之间未连通,则印制电路板的偏移量大于或等于4mil,并小于5mil;若检测装置两个

连接柱之间依然连通,则印制电路板的偏移量大于或等于5mil,从而能够通过上述方法确定印制电路板的偏移量。

69.容易理解的是,在本技术实施例中,第一导电图案21和偏移测试点213同样可以设置在第二测试板22和多个填充板23上,从而能够对印制电路板各层之间的偏移量进行检测,至于具体检测方式,本技术实施例在此不再赘述。

70.综上所述,当需要确定背钻孔14的深度时,通过多个深度测试孔24进行检测,当多个深度测试孔24未导通时,则背钻孔14的深度较小,背钻孔14未延伸至第一芯板11处;当多个深度测试孔24通过第一导电图案211连通,并且未通过第二导电图案221导通时,则背钻孔14穿过第一芯板11,并延伸至第一芯板11与第二芯板12之间;当多个深度测试孔24既能够通过第一导电图案211连通,并且还能够通过第二导电图案221导通,则背钻孔14的深度较大,背钻孔14穿过第一芯板11和第二芯板12;从而能够利用多个深度测试孔24对背钻孔14的深度进行检测,从而无需通过切片检测确定背钻孔14的深度,提高了检测背钻孔14深度的工作效率;

71.当利用偏移测试孔25对印制电路板的偏移量进行检测时,将检测装置的两个连接柱其中一个放置在第一深度测试孔241内,另一个放置在偏移测试孔25内,当第一芯板11与相邻的功能芯板13之间未出现偏移或偏移量较小时,在测试部2上,偏移测试孔25穿过第一测试板21时,偏移测试孔25与偏移测试点213相对应,并穿过偏移测试点213,第二导电层251未与环形导电部2112相接触,则检测装置两个连接柱之间未连通;当第一芯板11与相邻的功能芯板13之间出现偏移,且偏移量大于或等于偏移间隙212时,在测试部2上,偏移测试孔25穿过第一测试板21时,偏移测试孔25偏离偏移测试点213,第二导电层251与环形导电部2112连通,则检测装置两个连接柱之间通过第一导电层244、第二导电层251和导电图案连通,从而确定印制电路板的偏移量。

72.本技术实施例还提供一种电子设备,包括上述印制电路板。

73.通过采用上述技术方案,在电子设备的印制电路板中,主体1连接测试部2,从而利用测试部2的第一测试板21、第二测试板22和填充板23分别模拟第一芯板11、第二芯板12和功能芯板13;当需要确定背钻孔14的深度时,通过多个深度测试孔24进行检测,当多个深度测试孔24未导通时,则背钻孔14的深度较小,背钻孔14未延伸至第一芯板11处;当多个深度测试孔24通过第一导电图案211连通,并且未通过第二导电图案221导通时,则背钻孔14穿过第一芯板11,并延伸至第一芯板11与第二芯板12之间;当多个深度测试孔24既能够通过第一导电图案211连通,并且还能够通过第二导电图案221导通,则背钻孔14的深度较大,背钻孔14穿过第一芯板11和第二芯板12;从而能够利用多个深度测试孔24对背钻孔14的深度进行检测,从而无需通过切片检测确定背钻孔14的深度,提高了形成背钻孔14的工作效率。

74.本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本技术的其它实施方案。本技术旨在涵盖本技术的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本技术的一般性原理并包括本技术未公开的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本技术的真正范围和精神由下面的权利要求书指出。

75.应当理解的是,本技术并不局限于上面已经描述并在附图中示出的精确结构,并且可以在不脱离其范围进行各种修改和改变。本技术的范围仅由所附的权利要求书来限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1