差分放大电路和射频前端模组的制作方法

1.本实用新型涉及射频技术领域,尤其涉及一种差分放大电路和射频前端模组。

背景技术:

2.随着5g通信的逐渐普及,对终端等通信设备收发射频信号的性能需求也越来越高。例如,要求射频前端电路中的功率放大电路要有更好的线性度、功率、效率、带宽等。然而,现有的差分放大电路为了满足各项性能需求,往往需要占用很大面积来布局接入的元器件。例如:现有的差分放大电路为了实现阻抗匹配,往往需要接入多个匹配电容和多个匹配电感,从而导致差分放大电路的占用面积过大。因此,如何在保证差分放大电路的整体性能的同时实现差分放大电路的小型化需求,成为目前亟待解决的问题。

技术实现要素:

3.本实用新型实施例提供一种差分放大电路,以解决差分放大电路无法同时兼顾性能和占用面积的问题。

4.一种差分放大电路,包括第一级放大单元、第二级放大单元以及设置在所述第一级放大单元和所述第二级放大单元之间的匹配电路;所述匹配电路包括连接线,所述连接线与所述第一级放大单元和所述第二级放大单元之间的连接路径上的节点连接。

5.进一步地,所述连接线包括键合线。

6.进一步地,所述连接线包括第一连接线,所述第一连接线的第一端与所述第一级放大单元的第一输出端和所述第二级放大单元的第一输入端之间的连接路径上的节点连接,所述第一连接线的第二端与所述第一级放大单元的第二输出端和所述第二级放大单元的第二输入端之间的连接路径上的节点连接。

7.进一步地,所述连接线包括第二连接线和第三连接线,所述第二连接线的第一端与所述第一级放大单元的第一输出端和所述第二级放大单元的第一输入端之间的连接路径上的节点连接,所述第二连接线的第二端接地;所述第三连接线的第一端与所述第一级放大单元的第二输出端和所述第二级放大单元的第二输入端之间的连接路径上的节点连接,所述第三连接线的第二端接地。

8.进一步地,所述匹配电路还包括第一匹配电容、第二匹配电容、第三匹配电容和第四匹配电容,所述第一匹配电容的第一端与所述第一级放大单元的第一输入出连接,所述第一匹配电容的第二端与所述第二匹配电容的第一端连接,所述第二匹配电容的第二端与第二级放大单元的第一输入端连接;所述第三匹配电容的第一端与所述第一级放大单元的第二输出端连接,所述第三匹配电容的第二端与所述第四匹配电容的第一端连接,所述第四匹配电容的第二端与第二级放大单元的第二输入端连接。

9.进一步地,所述第一连接线的第一端与所述第一匹配电容的第二端连接,所述第一连接线的第二端与所述第三匹配电容的第二端连接。

10.进一步地,所述第二连接线的第一端与所述第一匹配电容的第二端连接,所述第

二连接线的第二端接地,所述第三连接线的第一端与所述第三匹配电容的第二端连接,所述第二连接线的第二端接地。

11.进一步地,所述连接线的等效电感值小于等于1纳亨。

12.进一步地,所述第一级放大单元包括第一放大晶体管和第一巴伦,所述第一放大晶体管的第一端与所述第一巴伦的第一输入端连接,所述第一巴伦的第二输入端接地,所述第一巴伦的第一输出端为所述第一级放大单元的第一输出端,所述第一巴伦的第二输出端为所述第一级放大单元的第二输出端,或者,所述第一级放大单元包括第一差分放大晶体管和第二差分放大晶体管,所述第一差分放大晶体管的输出端为所述第一级放大单元的第一输出端,所述第二差分放大晶体管的输出端为所述第一级放大单元的第二输出端;

13.所述第二级放大单元包括第三差分放大晶体管和第四差分放大晶体管,所述第三差分放大晶体管的输入端为所述所述第二级放大单元的第一输入端,所述第四差分放大晶体管的输入端为所述所述第二级放大单元的第二输入端。

14.进一步地,所述差分放大电路还包括第三连接线和第四连接线,所述第三连接线的第一端与所述第一差分放大晶体管的输出端连接,所述第三连接线的第二端与第一供电端连接,所述第四连接线的第一端与所述第二差分放大晶体管的输出端连接,所述第四连接线的第二端与第二供电端连接。

15.一种射频前端模组,包括第一级放大芯片、第二级放大芯片以及设置在所述第一级放大芯片和所述第二级放大芯片之间的匹配电路,所述匹配电路包括连接线;所述连接线与设置在所述第一级放大芯片和所述第二级放大芯片之间的连接路径上的焊盘连接。

16.进一步地,所述连接线包括第一连接线,所述焊盘包括第一焊盘和第二焊盘,所述第一焊盘设置在所述第一级放大芯片的第一输出端和所述第二级放大芯片的第一输入端上的连接路径上,所述第二焊盘设置在所述第一级放大芯片的第二输出端和所述第二级放大芯片的第二输入端的连接路径上,所述第一连接线的第一端与所述第一焊盘连接,所述第一连接线的第二端与所述第二焊盘连接。

17.进一步地,所述连接线包括第二连接线和第三连接,所述焊盘包括第三焊盘和第四焊盘,所述第三焊盘设置在所述第一级放大芯片的第一输出端和所述第二级放大芯片的第一输入端上的连接路径上,所述第四焊盘设置在所述第一级放大芯片的第二输出端和所述第二级放大单元的第二输入端的连接路径上,所述第二连接线的第一端与所述第三焊盘连接,所述第二连接线的第二端与接地端连接,所述第三连接线的第一端与所述第四焊盘连接,所述第三连接线的第二端与接地端连接。

18.上述差分放大电路,包括第一级放大单元、第二级放大单元以及设置在所述第一级放大单元和所述第二级放大单元之间的匹配电路;所述匹配电路包括连接线,所述连接线与所述第一级放大单元和所述第二级放大单元之间的连接路径上的节点连接,在本实施例中,通过采用连接线来替代差分放大电路的匹配电路中的电感参与差分放大电路的阻抗转换,实现差分放大电路的阻抗匹配,从而在保证差分放大电路的整体性能(例如:带宽性能)的同时,还能避免了因引入电感而导致差分放大电路的整体占用面积过大,进而优化了差分放大电路的整体布局,满足差分放大电路的小型化的需求。

或“在其之下”或“在其下”元件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在

…

下面”和“在

…

下”可包括上和下两个取向。器件可以另外地取向(旋转90度或其它取向)并且在此使用的空间描述语相应地被解释。

33.在此使用的术语的目的仅在于描述具体实施例并且不作为本实用新型的限制。在此使用时,单数形式的“一”、“一个”和“所述/该”也意图包括复数形式,除非上下文清楚指出另外的方式。还应明白术语“组成”和/或“包括”,当在该说明书中使用时,确定所述特征、整数、步骤、操作、元件和/ 或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

34.为了彻底理解本实用新型,将在下列的描述中提出详细的结构及步骤,以便阐释本实用新型提出的技术方案。本实用新型的较佳实施例详细描述如下,然而除了这些详细描述外,本实用新型还可以具有其他实施方式。

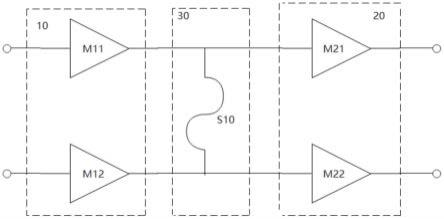

35.本实施例提供一种差分放大电路,如图1和图2所示,包括第一级放大单元10、第二级放大单元20以及设置在所述第一级放大单元10和所述第二级放大单元20之间的匹配电路30;所述匹配电路30包括连接线,所述连接线与所述第一级放大单元10和所述第二级放大单元20之间的连接路径上的节点连接。

36.其中,第一级放大单元10对射频输入信号进行放大,并输出射频放大信号。可选地,第一级放大单元10可以为单端放大单元,也可以为差分放大单元。第二级放大单元20对第一级放大单元10输出的射频放大信号进行放大,并输出射频输出信号。可选地,第二级放大单元20可以为单端放大单元,也可以为差分放大单元。

37.需要说明的是,由于本技术为差分放大电路,第一级放大单元10和第二放大单元20中至少有一个为差分放大单元。第一级放大单元10至第二放大单元20可以为单端转差分的差分放大电路,也可以为差分转单端的差分放大电路,还可以为双差分的差分放大电路。其中,第一级放大单元10可以为驱动级、中间级中的任一放大级。第二级放大单元20可以为中间级、输出级中的任一放大级。

38.其中,匹配电路30为设置在第一级放大单元10和第二级放大单元20之间,且参与差分放大电路的阻抗转换以实现阻抗匹配的电路。在本实施例中,匹配电路30包括连接线,所述连接线与所述第一级放大单元10和所述第二级放大单元20之间的连接路径上的节点连接。可以理解地,本技术中的连接线并非所述第一级放大单元10和所述第二级放大单元20之间连接路径上的连接线,而是与所述第一级放大单元10和所述第二级放大单元20之间的连接路径上的节点连接的连接线,且本技术中的连接线主要起阻抗匹配的作用。例如:连接线可以一端与所述第一级放大单元10和所述第二级放大单元20 之间的连接路径上的节点连接,另一端与接地端连接。

39.其中,连接线参与差分放大电路的阻抗转换。在本实施例中,连接线呈感性阻抗,可以替代电感参与阻抗匹配。相比较于通过电感进行阻抗匹配,连接线在实现相同功能且达到相同性能的前提下能节省更大的占用面积,使得差分放大电路的布局更紧凑和合理。可选地,所述连接线为可以为跳线、键合线或者引线等任意可将两个金属节点进行连接的连接线。连接线可以通过焊盘的形式实现连接。

40.在一具体实施例中,优选地,所述连接线包括键合线。

41.在本实施例中,差分放大电路包括第一级放大单元、第二级放大单元以及设置在所述第一级放大单元和所述第二级放大单元之间的匹配电路;所述匹配电路包括连接线,所述连接线与所述第一级放大单元和所述第二级放大单元之间的连接路径上的节点连接,在本实施例中,通过采用连接线来替代差分放大电路的匹配电路中的电感,连接线参与差分放大电路的阻抗转换,实现差分放大电路的阻抗匹配,从而在保证差分放大电路的整体性能(例如:带宽性能)的同时,还能避免了因引入电感而导致差分放大电路的整体占用面积过大,进而优化了差分放大电路的整体布局,满足小型化的需求。

42.在一具体实施例中,参照下图1所示,所述连接线包括第一连接线s10,所述第一连接线s10的第一端与所述第一级放大单元10的第一输出端和所述第二级放大单元20的第一输入端之间的连接路径上的节点连接,所述第一连接线s10的第二端与所述第一级放大单元10的第二输出端和所述第二级放大单元20的第二输入端之间的连接路径上的节点连接。

43.在本实施例中,所述第一级放大单元10包括第一差分放大晶体管m11 和第二差分放大晶体管m12。所述第二级放大单元20包括第三差分放大晶体管m21和第四差分放大晶体管m22。其中,第一差分放大晶体管m11、第二差分放大晶体管m12、第三差分放大晶体管m21和第四差分放大晶体管m22 均可以为bjt晶体管,也可以为场效应晶体管(fet)。可选地,第一差分放大晶体管m11、第二差分放大晶体管m12、第三差分放大晶体管m21和第四差分放大晶体管m22均包括至少一个bjt晶体管(例如,hbt晶体管)或至少一个场效应晶体管。示例性地,第一差分放大晶体管m11、第二差分放大晶体管m12、第三差分放大晶体管m21和第四差分放大晶体管m22均可以为多个bjt晶体管并联而成。

44.在一具体实施例中,第一差分放大晶体管m11被配置为放大第一射频输入信号并输出第一射频放大信号(放大后的第一射频输入信号),第一射频放大信号经过匹配电路30输入至第三差分放大晶体管m21的输入端,第二差分放大晶体管m12被配置为放大第二射频输入信号并输出第二射频放大信号 (放大后的第二射频输入信号),第二射频放大信号经过匹配电路30输入至第四差分放大晶体管m22的输入端。其中,第一射频输入信号可以为对应的前级放大电路放大之后输出的射频信号,也可以为将不平衡的输入射频信号进行转换后得到的其中一个平衡的射频信号等。同理,第二射频输入信号也可以为对应的前级放大电路放大之后输出的射频信号,也可以为将不平衡的输入射频信号进行转换后得到的其中一个平衡的射频信号等。

45.本示例中,第一连接线s10呈感性阻抗参与差分放大电路的阻抗转换,由于第一连接线的第一端与所述第一级放大单元的第一输出端和所述第二级放大单元的第一输入端之间的连接路径上的节点连接,第二端与所述第一级放大单元的第二输出端和所述第二级放大单元的第二输入端之间的连接路径上的节点连接,第一连接线没有跟实地(gnd)直接连接,第一连接线上自适应会形成一个虚地节点,从而可以避免因与实地(gnd)直接连接而带来的寄生效应,且还能改善差分放大电路的平衡性和对称性。

46.在一具体实施例中,所述第一连接线10上形成虚地节点,所述虚地节点被配置为自适应调整所述差分放大电路的平衡性。可以理解地,由于第一连接线没有跟实地(gnd)直接连接,所述第一连接线上会形成一个虚地节点,且该虚地节点的位置可以自适应地调整,以满足差分放大电路的平衡性,从而达到在实现阻抗匹配且满足差分放大电路的其它性能的同时,还能进一步提高差分放大电路的平衡性和对称性。

47.在一具体实施例中,参照下图2所示,所述连接线包括第二连接线s11 和第三连接线s12,所述第二连接线s11的第一端与所述第一级放大单元10 的第一输出端和所述第二级放大单元20的第一输入端之间的连接路径上的节点连接,所述第二连接线s11的第二端接地;所述第三连接线s12的第一端与所述第一级放大单元10的第二输出端和所述第二级放大单元20的第二输入端之间的连接路径上的节点连接,所述第三连接线s12的第二端接地。

48.本示例中,第二连接线s11和第三连接线s12呈感性阻抗参与差分放大电路的阻抗转换。优选地,为了保证差分放大电路的平衡性,第二连接线s11 所等效的感性阻抗和第三连接线s12所等效的感性阻抗大小相同。相比于在所述第一级放大单元10的第一输出端和所述第二级放大单元20的第一输入端之间的连接路径上的节点上接入到地的电感,以及在所述第一级放大单元 10的第二输出端和所述第二级放大单元20的第二输入端之间的连接路径上的节点上接入到地的电感,本实施例采用连接线的方式参与差分放大电路的阻抗转换,不但能实现差分放大电路的阻抗保证差分放大电路的整体性能(例如:带宽性能),且还能避免了因引入电感而导致差分放大电路的整体占用面积过大,进而优化了差分放大电路的整体布局,满足小型化的需求。

49.在一具体实施例中,参照下图3和图4所示,所述匹配电路还包括第一匹配电容c11、第二匹配电容c21、第三匹配电容c12和第四匹配电容c22,所述第一匹配电容c11的第一端与所述第一级放大单元10的第一输出端连接,所述第一匹配电容c11的第二端与所述第二匹配电容c21的第一端连接,所述第二匹配电容c21的第二端与第二级放大单元20的第一输入端连接。所述第三匹配电容c12的第一端与所述第一级放大单元10的第二输出端连接,所述第三匹配电容c12的第二端与所述第四匹配电容c22的第一端连接,所述第四匹配电容c22的第二端与第二级放大单元20的第二输入端连接。

50.其中,第一匹配电容c11、第二匹配电容c21、第三匹配电容c12和第四匹配电容c22均为匹配电路中参与阻抗转换的电容。第一匹配电容c11、第二匹配电容c21、第三匹配电容c12和第四匹配电容c22呈现的容性阻抗与匹配电路中连接线呈现的感性阻抗相互作用,以实现差分放大电路的阻抗匹配,优化差分放大电路在工作频段内的带宽性能。

51.参照下图3所示,所述第一连接线s10的第一端与所述第一匹配电容c11 的第二端连接,所述第一连接线s10的第二端与所述第三匹配电容c12的第二端连接。

52.本示例中,第一匹配电容c11、第二匹配电容c21、第三匹配电容c12 和第四匹配电容c22呈现的容性阻抗与所述第一连接线s10呈现的感性阻抗相互作用,以实现差分放大电路的阻抗匹配,优化差分放大电路在工作频段内的带宽性能。

53.或者,参照下图4所示,所述第二连接线s11的第一端与所述第一匹配电容c11的第二端连接,所述第二连接线s11的第二端接地,所述第三连接线s12的第一端与所述第三匹配电容c21的第二端连接,所述第三连接线s12 的第二端接地。

54.本示例中,第一匹配电容c11、第二匹配电容c21、第三匹配电容c12 和第四匹配电容c22呈现的容性阻抗与所述第二连接线s11和第三连接线s12 呈现的感性阻抗相互作用,以实现差分放大电路的阻抗匹配,优化差分放大电路在工作频段内的带宽性能。

55.在一具体实施例中,所述连接线的等效电感值小于等于1纳亨。

56.由于本本示例通过采用非巴伦式的匹配电路,因此,只需要较小电感阻抗和较小

电容阻抗相互作用即可实现阻抗匹配,从而不但可以减小阻抗匹配难度保证匹配带宽,还能减小匹配电路的占用面积,满足后续的封装需求。

57.在一具体实施例中,参照下图5所示,所述第一级放大单元10包括第一放大晶体管m10和第一巴伦b1,所述第一放大晶体管m10的第一端与所述第一巴伦b1的第一输入端连接,所述第一巴伦b1的第二输入端接地,所述第一巴伦b1的第一输出端为所述第一级放大单元的第一输出端,所述第一巴伦的第二输出端为所述第一级放大单元的第二输出端。可以理解地,本实施例中第一级放大单元10为单端放大单元。

58.或者,参照下图3所示,所述第一级放大单元10包括第一差分放大晶体管m11和第二差分放大晶体管m12,所述第一差分放大晶体管m11的输出端为所述第一级放大单元的第一输出端,所述第二差分放大晶体管m12的输出端为所述第一级放大单元的第二输出端。可以理解地,本实施例中第一级放大单元10为差分放大单元。

59.所述第二级放大单元20包括第三差分放大晶体管m21和第四差分放大晶体管m22,所述第三差分放大晶体管m21的输入端为所述所述第二级放大单元20的第一输入端,所述第四差分放大晶体管m22的输入端为所述所述第二级放大单元20的第二输入端。可以理解地,本实施例中第二级放大单元20 为差分放大单元。

60.由此可知,当第一级放大单元10为单端放大单元,所述第二级放大单元 20为差分放大单元时,差分放大电路为单端转差分的放大电路。当第一级放大单元10为差分放大单元,所述第二级放大单元20为差分放大单元时,差分放大电路为双差分的放大电路。

61.参照下图6所示,在一具体实施例中,所述差分放大电路还包括第三连接线s21和第四连接线s22,所述第三连接线s21的第一端与所述第一差分放大晶体管m11的输出端连接,所述第三连接线s21的第二端与第一供电端连接,所述第四连接线s22的第一端与所述第二差分放大晶体管m12的输出端连接,所述第四连接线s22的第二端与第二供电端连接。

62.其中,第一供电端通过第三连接线s21给第一差分放大晶体管m11供电,以保证第一差分放大晶体管m11的正常工作。第二供电端通过第四连接线s22 给第二差分放大晶体管m12供电,以保证第二差分放大晶体管m12的正常工作。

63.相比于供电电源端通过电感的方式给第一差分放大晶体管m11和第二差分放大晶体管m12供电,本示例的供电电源端通过传输线给第一差分放大晶体管m11和第二差分放大晶体管m12供电,不但可以保证差分放大电路的正常供电,还能避免因引入电感而导致差分放大电路的总体占用面积过大。

64.本技术还提供一种射频前端模组,包括第一级放大芯片100、第二级放大芯片200以及设置在所述第一级放大芯片100和所述第二级放大芯片200之间的匹配电路30,所述匹配电路30包括连接线;所述连接线与设置在所述第一级放大芯片100和所述第二级放大芯片200之间的连接路径上的焊盘连接。

65.其中,第一级放大芯片100为集成有放大器件或者转换合成器件的芯片。例如:第一级放大芯片100上集成有两个差分放大晶体管,或者第一级放大芯片100上集成有一个差分放大晶体管和一个巴伦。同样地,第二级放大芯片200为集成有放大器件或者转换合成器件的芯片。例如:第二级放大芯片 200上集成有两个差分放大晶体管,或者第二级放大芯片200上集成有一个差分放大晶体管和一个巴伦。

66.匹配电路30为设置在第一级放大芯片100和第二级放大芯片200之间,且参与差分

放大电路的阻抗转换以实现阻抗匹配的电路。所述匹配电路30包括连接线,所述连接线与设置在所述第一级放大芯片100和所述第二级放大芯片200之间的连接路径上的焊盘连接。可以理解的,本技术中的连接线并非所述第一级放大单元10和所述第二级放大单元20之间连接路径上的连接线,而是并联在在所述第一级放大单元10和所述第二级放大单元20之间的连接路径上的连接线。例如:连接线可以一端与所述第一级放大单元10和所述第二级放大单元20之间的连接路径上的焊盘连接,另一端与接地端连接。

67.其中,连接线参与差分放大电路的阻抗转换。在本实施例中,连接呈感性阻抗,线可替代电感。相比较于通过电感进行阻抗转换,连接线在实现相同功能且达到相同性能的前提下能节省更大的面积,使得差分放大电路的布局更紧凑和合理。可选地,所述连接线为可以为跳线、键合线线或者引线等任意可将两个金属节点进行连接的连接线。连接线通过焊盘的形式实现连接。

68.参照下图7所示,在一具体实施例中,所述连接线包括第一连接线s10,所述焊盘包括第一焊盘和第二焊盘,所述第一焊盘设置在所述第一级放大芯片的第一输出端和所述第二级放大芯片的第一输入端上的连接路径上,所述第二焊盘设置在所述第一级放大芯片的第二输出端和所述第二级放大芯片的第二输入端的连接路径上,所述第一连接线s10的第一端与所述第一焊盘连接,所述第一连接线的第二端与所述第二焊盘连接。

69.参照下图8所示,在另一具体实施例中,所述连接线包括第二连接线s11 和第三连接s12,所述焊盘包括第三焊盘和第四焊盘,所述第三焊盘设置在所述第一级放大芯片的第一输出端和所述第二级放大芯片的第一输入端上的连接路径上,所述第四焊盘设置在所述第一级放大芯片的第二输出端和所述第二级放大单元的第二输入端的连接路径上,所述第二连接线s11的第一端与所述第三焊盘连接,所述第二连接线s11的第二端与接地端连接,所述第三连接线s12的第一端与所述第四焊盘连接,所述第三连接线s12的第二端与接地端连接。

70.以上所述实施例仅用以说明本实用新型的技术方案,而非对其限制;尽管参照前述实施例对本实用新型进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型各实施例技术方案的精神和范围,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1