一种高速脉冲计数模块的制作方法

1.本实用新型涉及脉冲计数模块,尤其是涉及高速脉冲计数模块。

背景技术:

2.在冶金、电子、机械、医疗、天文等领域,都需要对电子器件输出的随机性高速脉冲进行采样检测,例如光电倍增管(pmt)就是一种将光信号转化为电信号的电子器件。随机性高速脉冲具有速度高、随机性强、脉宽小等特点,这就使得对随机性高速脉冲计数提出很高的要求。随机性高速脉冲脉宽很窄,一般在ns级,随机性强,传统的单片机脉冲计数方法,在输入脉冲频率很高或者脉宽很窄的时候,难以保证计数的实时性、准确性,存在计数误差,甚至不能检测到脉冲。

3.为解决上述问题,现有方案是将高速脉冲信号连接到fpga(英文field-programmable gate array,现场可编程门阵列)或cpld(英文complex programmable logic device,复杂可编程逻辑器件)的某个管脚上,通过fpga内部配置对高速脉冲采集、计数处理,然后输出计数值。然而,采用fpga或cpld计数方案成本高,需要内部编程来实现,同时受fpga主频影响,可靠性低,且对fpga芯片的质量要求很高。

技术实现要素:

4.本实用新型目的在于提供一种价格低廉、工作稳定的高速脉冲计数模块。

5.为实现上述目的,本实用新型采取下述技术方案:

6.本实用新型所述的高速脉冲计数模块,包括单片机、计数单元和逻辑门控单元;所述单片机的开关信号输出端与所述逻辑门控单元的控制信号输入端连接,用于控制逻辑门控单元的打开与关闭;单片机的清零信号输出端与所述计数单元的清零信号输入端连接,单片机通过清零信号控制计数单元的计数值;计数单元的数据输出端通过总线与单片机的数据输入端连接,计数单元的数据输入端与逻辑门控单元的数据输出端连接,用于对高速脉冲信号计数,逻辑门控单元数据输入端与高速脉冲信号输入端连接。

7.可选择地,所述逻辑门控单元为二输入与非门,所述计数单元由包含32个t触发器的芯片级联组成,计数值为32位;当然,在不需要计数值很大的领域,可以改为24位、16位或其他数值

8.本实用新型采用价格低廉的单片机、逻辑门控单元组成高速脉冲计数电路,在成本上优势更明显;同时减少了可编程器件,计数单元由纯硬件电路实现,更加稳定可靠,不受现有高速脉冲信号连接到fpga计数时的主频影响,更适合高速应用。

附图说明

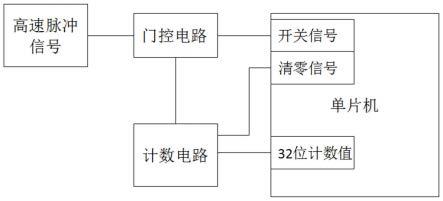

9.图1是本实用新型的电路原理结构框图。

10.图2是本实用新型所述二输入与非门的电路原理图。

11.图3是本实用新型所包含32个t触发器的芯片级联电路原理图。

具体实施方式

12.下面结合附图对本实用新型的实施例作详细说明,本实施例在以本实用新型技术方案为前提下进行实施,给出了详细的实施方式和具体的工作过程,但本实用新型的保护范围不限于下述实施例。

13.如图1所示,本实用新型所述的高速脉冲计数模块,包括单片机、计数单元和逻辑门控单元,

14.所述单片机的开关信号输出端与所述逻辑门控单元的控制信号输入端连接,用于控制逻辑门控单元的打开与关闭;打开状态下,高速脉冲信号可以通过逻辑门控单元到达计数单元;关闭状态下:高速脉冲信号不可通过逻辑门控单元,逻辑门控单元输出固定的高电平给计数电路。

15.单片机的清零信号输出端与所述计数单元的清零信号输入端连接;单片机通过清零信号控制计数单元的计数值,本计数单元是一个加法计数,给一个脉冲信号,计数值增加1;清零信号是当完成一次计数后,单片机对计数单元进行清零,重新开始计数。

16.计数单元的数据输出端通过32位总线与单片机的数据输入端连接,计数单元的数据输入端与逻辑门控单元的数据输出端连接,用于对高速脉冲信号计数,逻辑门控单元数据输入端与高速脉冲信号输入端连接。

17.本实用新型通过开关信号与清零信号配合使用,完成对高速脉冲信号的一次计数,计数值通过一条32位的总线并行传输给单片机,因此,计数值可以从0~42.9亿,完全满足光子计数领域应用。

18.本实用新型一次计数过程如下:

19.开关信号关闭逻辑门控单元,清零信号对计数单元进行复位清零;开关信号打开逻辑门控单元,同时开始计时,时间到,关闭逻辑门控单元,单片机从计数单元32位总线上获取当前计数值。

20.有益地或示例性地,如图2所示,所述逻辑门控单元为二输入与非门u1,二输入与非门u1的1脚接高速脉冲信号,2脚接单片机的开关信号输出端。

21.如图3所示,所述计数单元由包含32个t触发器的集成芯片u2、u3、u4级联组成。

技术特征:

1.一种高速脉冲计数模块,其特征在于:包括单片机、计数单元和逻辑门控单元;所述单片机的开关信号输出端与所述逻辑门控单元的控制信号输入端连接,单片机的清零信号输出端与所述计数单元的清零信号输入端连接;计数单元的数据输出端通过总线与单片机的数据输入端连接,计数单元的数据输入端与逻辑门控单元的数据输出端连接,逻辑门控单元数据输入端与高速脉冲信号输入端连接。2.根据权利要求1所述的高速脉冲计数模块,其特征在于:所述逻辑门控单元为二输入与非门;所述计数单元由包含32个t触发器的芯片级联组成。

技术总结

本实用新型公开了一种高速脉冲计数模块,包括单片机、计数单元和逻辑门控单元;单片机的开关信号输出端与所述逻辑门控单元的控制信号输入端连接,用于控制逻辑门控单元的打开与关闭;单片机的清零信号输出端与计数单元的清零信号输入端连接,单片机通过清零信号控制计数单元的计数值;计数单元的数据输出端通过总线与单片机的数据输入端连接,计数单元的数据输入端与逻辑门控单元的数据输出端连接,用于对高速脉冲信号计数,逻辑门控单元数据输入端与高速脉冲信号输入端连接。本实用新型采用价格低廉的单片机、逻辑门控单元组成高速脉冲计数电路,在成本上优势更明显;同时减少了可编程器件,计数单元由纯硬件电路实现,更加稳定可靠。定可靠。定可靠。

技术研发人员:王聪 唐鹏桢 尤红艳 王超 刘聪 魏文娟

受保护的技术使用者:安图实验仪器(郑州)有限公司

技术研发日:2022.10.31

技术公布日:2023/3/23

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1