总线架构的量子信息处理的时序控制信号产生装置

1.本实用新型涉及冷原子(离子)量子信息实验领域,具体涉及总线架构的量子信息处理的时序控制信号产生装置,适合于冷原子(离子)量子信息实验中时序控制信号的产生,也适合于光学频标、量子光学等领域。

背景技术:

2.目前的基于现场可编程逻辑器件(fpga)和直接数字频率合成器(dds)开发的通用时序控制信号产生系统主要包括时序控制模块、射频合成模块和转换模块三个模块。其中的转换模块由电平转换电路、数字信号输出电路和外部触发输入电路组成,它可以实现一个时序控制模块和多个射频合成模块的联接。电平转换电路主要是完成数字信号和低电压差分信号之间的转换,这样就可以把时序控制模块、射频合成模块以及转接模块单独在一块电路板上实现,各电路板间通信采用lvds信号,能有效排除噪声干扰。数字信号输出电路由排针连接器实现,数字信号输出电路把时序控制模块通过电平转换电路传过来的数字信号传输到物理系统上。外部触发输入电路也是由排针连接器实现,外部触发输入电路把外部触发信号通过电平转换电路输入到时序控制模块。

3.虽然目前的通用时序控制信号产生系统可以简单地通过上位机发送指令,从而自动产生量子比特操作所需的各种时序控制信号。但是该系统的转换模块中的数字信号输出电路和外部触发输入电路都是由排针连接器实现,这种连接在物理性能方面抗震动能力很差,每次迁移系统都可能造成物理连接松动,从而会导致实验难以进行,且这种故障很难找到根源。由排针连接器实现在信号传输方面也难以做到稳定传输,且系统的信号传输存在串扰问题。随着研究的深入,实验难度不断增加,实验对数字信号的数量有了更高的要求,目前的系统输出的数字信号只有32位,已经难以满足物理实验的需求。

技术实现要素:

4.本实用新型的目的在于针对现有技术存在的上述问题,提供总线架构的量子信息处理的时序控制信号产生装置。

5.本实用新型的上述目的通过以下技术手段实现:

6.总线架构的量子信息处理的时序控制信号产生装置,包括上位机,还包括时序控制模块、射频合成模块、转接模块和连接模块,

7.时序控制模块包括以太网接口电路、时序逻辑控制fpga、第一单端转差分模块、第一总线接口、sram内存和第一差分转单端模块,

8.射频合成模块包括滤波电路、功率放大器、vga模块、dds模块、dds逻辑控制fpga、第二差分转单端模块、第二总线接口和dac模块,

9.转换模块包括数字信号输出电路、分时复用模块、第三差分转单端模块、第三总线接口、外部触发输入电路和第二单端转差分模块,

10.连接模块包括外部总线接口,

11.第一总线接口分别与第一单端转差分模块和第一差分转单端模块连接,上位机通过以太网接口电路与时序逻辑控制fpga连接,时序逻辑控制fpga还分别与sram内存、第一单端转差分模块和第一差分转单端模块连接;

12.第二总线接口与第二差分转单端模块连接,第二差分转单端模块与dds逻辑控制fpga连接,dds逻辑控制fpga分别与dds模块和dac模块连接,vga模块分别与dds模块、dac模块和功率放大器连接,功率放大器与滤波电路连接;

13.第三总线接口分别与第二单端转差分模块和第三差分转单端模块连接,第三差分转单端模块分别与分时复用模块和数字信号输出电路连接,分时复用模块和数字信号输出电路连接,外部触发输入电路分别与分时复用模块和第二单端转差分模块连接;

14.外部总线接口、第一总线接口、第二总线接口和第三总线接口之间通过总线连接。

15.本实用新型相对于现有技术,具有以下益效果:

16.1、采用总线的架构,实现时序控制模块、射频合成模块和转接模块等三种类型的功能模块的互联,使拓展更加灵活方便,连接更加稳定,抗震能力大大提高,进而提高了整个装置的鲁棒性;

17.2、在电路板上实现总线架构,提高了信号传输的抗干扰能力;

18.3、在不增加成本的情况下,使用分时复用技术,增加了16位的数字信号输出。

附图说明

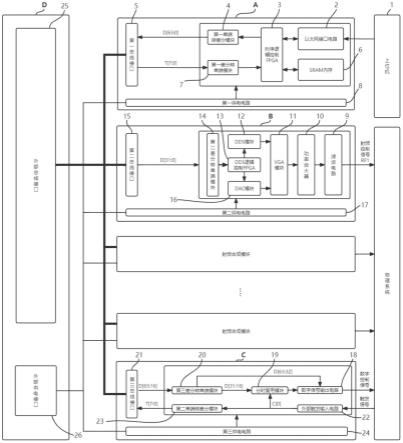

19.图1为本实用新型的原理示意图。

20.其中:1-上位机,2-以太网接口电路,3-时序逻辑控制fpga(field programmable gate array,fpga),4-第一单端转差分模块,5-第一总线接口,6-sram内存,7-第一差分转单端模块,8-第一供电电路,9-滤波电路,10-功率放大器,11-vga模块(variable gain amplifier,可变增益放大器),12-dds模块(direct digital synthesizer,dds,直接数字合成器),13-dds逻辑控制fpga,14-第二差分转单端模块,15-第二总线接口,16-dac模块(数模转换器,dac,digital to analog converter),17-第二供电电路,18-数字信号输出电路,19-分时复用模块,20-第三差分转单端模块,21-第三总线接口,22-外部触发输入电路,23-第二单端转差分模块,24-第三供电电路,25-外部总线接口,26-外部供电接口。a-时序控制模块;b-射频合成模块;c-转接模块;d-连接模块。

21.图2为物理系统的一种实例;

22.其中:27-激光器,28-switch开关,29-aom(声光调制器,acousto-optical modulators),30—离子阱。

具体实施方式

23.为了便于本领域普通技术人员理解和实施本实用新型,下面结合实施例对本实用新型作进一步的详细描述,应当理解,此处所描述的实施示例仅用于说明和解释本实用新型,并不用于限定本实用新型。

24.如图1所示,总线架构的量子信息处理的时序控制信号产生装置,包括上位机1,还包括时序控制模块a、射频合成模块b、转换模块c、以及连接模块d,

25.时序控制模块a包括以太网接口电路2、时序逻辑控制fpga3、sram内存6、第一单端

转差分模块4、第一差分转单端模块7、第一总线接口5和第一供电电路8,

26.射频合成模块b包括第二总线接口15、第二差分转单端模块14、dds逻辑控制fpga13、dds模块12、dac模块16、vga模块11、功率放大器10、滤波电路9和第二供电电路17,

27.转接模块c包括第三总线接口21、第三差分转单端模块20、分时复用模块19、第三供电电路24、第二单端转差分模块23、数字信号输出电路18和外部触发输入电路22,

28.连接模块d包括外部总线接口25和外部供电接口26,

29.第一总线接口5分别与第一单端转差分模块4和第一差分转单端模块7连接,上位机1通过以太网接口电路2与时序逻辑控制fpga3连接,时序逻辑控制fpga3还分别与sram内存6、第一单端转差分模块4和第一差分转单端模块7连接;第一供电电路8为时序控制模块a提供电源。

30.第二总线接口15与第二差分转单端模块14连接,第二差分转单端模块14与dds逻辑控制fpga13连接,dds逻辑控制fpga13分别与dds模块12和dac模块16连接,vga模块11分别与dds模块12、dac模块16和功率放大器10连接,功率放大器10与滤波器9连接;第二供电电路17为射频合成模块b提供电源。

31.第三总线接口21分别与第二单端转差分模块23和第三差分转单端模块20连接,第三差分转单端模块20分别与分时复用模块19和数字信号输出电路18连接,分时复用模块19和数字信号输出电路18连接,外部触发输入电路22分别与分时复用模块19和第二单端转差分模块23连接;第三供电电路24为转接模块c提供电源。

32.外部总线接口25通过总线分别与第一总线接口5、第二总线接口15和第三总线接口21连接。外部供电接口26分别与第一供电电路8、第二供电电路17和第三供电电路24连接。

33.射频合成模块b数目为2个或2个以上。

34.其中:

35.1、上位机

36.上位机1为普通pc机。上位机1通过以太网接口电路2传输数字控制信号和射频控制信号到时序逻辑控制fpga3。

37.2、时序控制模块a

38.时序控制模块a包括以太网接口电路2、时序逻辑控制fpga3、sram内存6、第一单端转差分模块4、第一差分转单端模块7、第一总线接口5和第一供电电路8,

39.2.1、以太网接口电路2

40.以太网接口电路2实现和上位机1的网络通信,采用以太网芯片dp83843实现。

41.2.2、时序逻辑控制fpga3

42.时序逻辑控制fpga3接收上位机1发送过来的数字控制信号和射频控制信号,并存入sram内存6,根据数字控制信号和射频控制信号生成32位的数字控制数据和32位的射频控制数据,根据32位的数字控制数据和32位的射频控制数据生成64位的控制信号d[63:0],64位的控制信号d[63:0]中的高32位数据为32位的数字控制数据,64位的控制信号d[63:0]中的低32位数据为32位的射频控制数据,将64位的控制信号d[63:0]通过第一单端转差分模块4、第一总线接口5传输到总线上,射频控制数据依次通过总线、第二总线接口15、第二差分转单端模块14传输给dds逻辑控制fpga13,数字控制数据和高16位射频控制数据依次

通过总线、第三总线接口21传输到第三差分转单端模块20。

[0043]

2.3、sram内存6

[0044]

sram内存6采用cyc7c1386b sram芯片实现,该芯片容量为512k

×

36。

[0045]

2.4、第一单端转差分模块4

[0046]

第一单端转差分模块4采用ds90lv047a芯片实现,该芯片将数字信号(cmos/ttl信号)转换为低电压差分信号(lvds,low-voltage differential signaling)。

[0047]

2.5、第一差分转单端模块7

[0048]

第一差分转单端模块7采用ds90lv048a芯片实现,该芯片将低电压差分信号转换为数字信号。

[0049]

2.6、第一供电电路8

[0050]

第一供电电路8采用ams1117系列的芯片,该系列芯片负责将+9v的电压转换为时序控制模块a所需的各种电压。供电的座子采用erni公司的7pin的背板连接器254018,该连接器使供电更加稳定,且方便拔插。

[0051]

2.7、第一总线接口5

[0052]

第一总线接口5采用erni公司的200pin的背板连接器124118。本实用新型采用这种连接器传输差分信号,大大提高了信号传输的稳定性,并且采用这种连接器解决了信号之间串扰的问题。这种连接方式在物理性能方面也表现出色,时序控制模块a和连接模块d采用这种连接器实现连接可以大大地提高抗震动的能力,方便系统的迁移。

[0053]

3、射频合成模块b

[0054]

每个射频合成模块b包括第二总线接口15、第二差分转单端模块14、dds逻辑控制fpga13、dds模块12、dac模块16、vga模块11、功率放大器10、滤波电路9和第二供电电路17。

[0055]

3.1、dds逻辑控制fpga13

[0056]

dds逻辑控制fpga13只接收时序控制模块a通过总线发过来的射频控制数据d[31:0]。dds逻辑控制fpga13根据射频控制信号d[31:0]通过dds模块12输出对应频率和初始相位值的射频信号到vga模块11,此射频信号作为vga模块11的信号源。同时dds逻辑控制fpga13根据射频控制数据d[31:0]通过调整dac模块16的电流输出并转换为电压输出来控制vga模块11的增益,从而控制从vga模块11输出的射频信号的幅值,vga模块11输出的射频信号依次通过功率放大器10和滤波电路9后作为射频信号rf1输出。

[0057]

3.2、dds模块12

[0058]

dds模块12采用analog devices公司的ad9910芯片,该芯片实现射频信号的产生。

[0059]

3.3、dac模块16

[0060]

dac模块16采用analog devices公司的ad9744芯片,该芯片实现dds逻辑控制fpga13传过来的数字信号转换为模拟信号,进而控制vga模块11的增益。

[0061]

3.4、vga模块11

[0062]

vga模块11采用analog devices公司的ad8367芯片,该芯片实现更大范围的射频信号的幅度控制。

[0063]

3.5、功率放大器10

[0064]

功率放大器10采用mini-circuits公司的era-3sm+芯片,该芯片实现增大射频信号的输出功率。

[0065]

3.6、滤波电路9

[0066]

滤波电路9采用分立元件电感和电容实现对射频信号的滤波。

[0067]

3.7、第二差分转单端模块14

[0068]

第二差分转单端模块14采用ds90lv048a芯片实现,该芯片将低电压差分信号转换为数字信号。

[0069]

3.8、第二供电电路17

[0070]

第二供电电路17采用lt3045芯片实现模拟电源的转换,采用xc6210、lm3940和lp38692芯片实现数字电源的转换,其中lt3045是超低噪声低压差稳压器,对于产生稳定的射频信号具有很大的意义。供电的座子采用erni公司的7pin的背板连接器254018。

[0071]

3.9、第二总线接口15

[0072]

第二总线接口15采用erni公司的200pin的背板连接器124118。

[0073]

4、转接模块c

[0074]

转接模块c包括第三总线接口21、第三差分转单端模块20、分时复用模块19、第三供电电路24、第二单端转差分模块23、数字信号输出电路18和外部触发输入电路22。

[0075]

4.1、第三总线接口21

[0076]

第三总线接口21采用erni公司的200pin的背板连接器124118。

[0077]

4.2、第三差分转单端模块20

[0078]

第三差分转单端模块20采用ds90lv048a芯片实现,该芯片将低电压差分信号转换为数字信号,具体将数字控制数据传输到数字信号输出电路18,将高16位射频控制数据传输到分时复用模块19。

[0079]

4.3、第三供电电路24

[0080]

第三供电电路24采用ams1117系列的芯片,该系列芯片负责将+9v的电压转换为转接模块c所需的各种电压。供电的座子采用erni公司的7pin的背板连接器254018。

[0081]

4.4、第二单端转差分模块23

[0082]

第二单端转差分模块23采用ds90lv047a芯片实现,该芯片将数字信号转换为低电压差分信号。

[0083]

4.5、分时复用模块19

[0084]

分时复用模块19采用nexperia(安世)公司的16位锁存器74lvc162373a芯片实现。本实用新型采用了分时复用技术,利用74lvc162373a芯片的锁存功能,

[0085]

当外部触发信号传输过来锁存控制信号c[0]为high时,将高16位射频控制数据d[31:16]进行锁存,高16位射频控制数据d[31:16]不作为转接模块c的输出,此时高16位射频控制数据d[32:16]可以作为射频合成模块的控制信号,数字信号输出电路18根据第三差分转单端模块20传输过来的数字控制数据生成数字信号ttl;

[0086]

当外部触发信号传输过来锁存控制信号c[0]为low时不对高16位射频控制数据d[31:16]进行锁存,高16位射频控制数据d[31:16]通过数字信号输出电路18输出,此时高16位射频控制数据d[32:16]不作为射频合成模块的控制信号。数字信号输出电路18根据第三差分转单端模块20传输过来的数字控制数据和分时复用模块19输出的高16位射频控制数据d[31:16]生成数字信号ttl。

[0087]

4.6、数字信号输出电路18

[0088]

数字信号输出电路18由smb接口实现,数字信号输出电路18把时序逻辑控制fpga3传过来的数字信号传输到物理系统上。

[0089]

4.7、外部触发输入电路22

[0090]

外部触发输入电路22由smb接口实现,外部触发输入电路22把外部触发信号中的锁存控制信号c[0]传输到分时复用模块19,外部触发输入电路22还将外部触发信号t[7:0]依次通过第二单端转差分模块23、第三总线接口21、总线、第一总线接口5、第一差分转单端模块7传输到时序逻辑控制fpga3。

[0091]

5、连接模块d

[0092]

连接模块d包括外部总线接口25和外部供电接口26。

[0093]

5.1、外部总线接口25

[0094]

外部总线接口25采用erni公司的200pin的背板连接器114279,外部总线接口25、第一总线接口5、第二总线接口15和第三总线接口21配合总线连接,不但大大提高了信号传输的稳定性,而且使装置能非常方便的进行拓展,不用区分接口。

[0095]

5.2、外部供电接口26

[0096]

外部供电接口26采用erni公司的7pin的背板连接器254016,将外部供电输送到各个模块。本实用新型采用这种连接器送电,大大提高了输电的稳定性。

[0097]

如图2所示,物理系统包括激光器27,switch开关28,aom(声光调制器,acousto-optical modulators)29,以及离子阱30。

[0098]

射频合成模块b输出的射频信号rf1输出到物理系统的aom29用作物理系统的信号源,转接模块c输出的数字信号ttl输出到物理系统的switch开关28上做数字开关使用。

[0099]

需要指出的是,本实用新型中所描述的具体实例仅是对本实用新型精神作举例说明。本实用新型所属技术领域的技术人员可以对所描述的具体实施例作各种各样的修改或补充或采用类似的方式替代,但并不会偏离本实用新型的精神或超越所附权利要求书所定义的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1