一种适用于多通道模拟量同步采集的去耦电路的制作方法

1.本实用新型一种适用于多通道模拟量同步采集的去耦电路属于传感器电路技术领域。

背景技术:

2.桥梁使用过程中,需要对桥梁支座的各项参数进行监测,例如支座滑移、倾角、振动承载力、温度、应变等参数。为了解决人工检查的弊端,节省检查成本,实现实时监测,可以采用无线传输状态监测系统。

3.然而,无论车辆在桥面行驶,还是自然环境,都会对测量信号造成干扰,导致测量结果不准确 ,甚至出现错误,影响对整个系统的状态判断,因此需要对各路限号进行针对性的抗干扰设计。

技术实现要素:

4.针对上述技术问题,本实用新型设计了一种适用于多通道模拟量同步采集的去耦电路,为纯硬件电路,通过配合现有技术的算法,能够有效抑制外界对测量信号的干扰,提高测量精度和准确性。

5.本实用新型的目的是这样实现的:

6.一种适用于多通道模拟量同步采集的去耦电路,包括电源模块,应变片模块,位移传感器模块,加速度传感器模块,ad转换模块,控制器模块和串行通信模块;

7.所述电源模块包括电源输入端、稳压芯片tps62177dqcr和低压差稳压芯片adm7160aujz-3.3-r7;

8.所述电源输入端包括电源输入,外挂电源充电盒和开关,电源输入端子的1脚和外挂电源充电盒端子的1脚短路,并通过二极管sk54a-ltp和二极管12v/2a的串联结构连接开关的1脚,电源输入端子的2脚和外挂电源充电盒端子的2脚短路,并连接gnd,开关的2脚作为电压输入,并通过二极管sk54a-ltp和2.2μf/50v电容的并联结构连接gnd;

9.在稳压芯片tps62177dqcr中,pgnd端口连接gnd,vin端口和en端口短路,并连接电压输入,nc端口、fb端口和agnd端口短路,连接gnd,pg端口通过100k电阻连接3.3v,sleep端口和vos端口短路,连接gnd,sw端口通过22uh电感连接3.3v,所述3.3v与gnd之间连接100μf/6.3v电容,3.3v为稳压输出,pad端口连接gnd;

10.在低压差稳压芯片adm7160aujz-3.3-r7中,vin端口连接电压输入,gnd端口连接gnd,并通过4.7μf电容连接电压输入,en端口通过10k电阻连接gnd,并连接stm32f103cb芯片中的pa4端口,vout端口定义为vref_wy,并通过4.7μf电容和100nf电容的并联结构连接gnd,所述gnd与agnd之间通过磁珠l1相连;

11.所述应变片模块包括应变片bf1k,bf1k的1脚通过1k电阻连接vref_wy,bf1k的2脚连接agnd,所述vref_wy通过100nf/25v电容连接agnd,通过两个1k电阻串联结构连接agnd,所述两个1k电阻串联结构抽头定义为-yb1;

12.所述位移传感器模块包括两个米朗ktr4,两个米朗ktr4的1脚短路,为vref_wy,并通过100nf/25v电容连接agnd,两个米朗ktr4的3脚短路,并连接agnd,两个米朗ktr4的1脚分别定义为+wy3和+wy4;

13.所述加速度传感器模块包括adxl203ce,在adxl203ce中,st端口连接agnd,并通过100nf/25v电容和22μf/16v电容的并联结构连接vs端口,com端口连接agnd,yout端口通过2.2μf/16v电容连接agnd,xout端口通过2.2μf/16v电容连接agnd,vs端口通过磁珠l5连接vref_wy;

14.所述ad转换模块包括24位adc芯片ads1248,所述ads1248的1脚连接vref_wy,ads1248的2脚和3脚短路,连接gnd,ads1248的4脚连接stm32f103cb的pa11脚,ads1248的5脚连接vref_wy,ads1248的6脚连接gnd,ads1248的9脚通过1μf电容连接gnd,ads1248的10脚连接gnd,并分别通过四个5.6nf电容连接ads1248的11脚、12脚、13脚和14脚,ads1248的11脚通过47nf电容连接ads1248的12脚,并通过6.04k电阻定义为-yb1,ads1248的12脚通过6.04k电阻定义为+yb1,ads1248的13脚通过6.04k电阻连接agnd,ads1248的14脚通过6.04k电阻定义为+wy3,ads1248的15脚通过5.6nf电容连接gnd,通过47nf电容连接ads1248的16脚,并通过6.04k电阻连接agnd,ads1248的16脚通过6.04k电阻定义为+wy4,并通过5.6nf电容连接gnd,ads1248的17脚连接u10的xout脚,ads1248的18脚连接u10的yout脚,ads1248的21脚连接gnd,并通过100nf电容连接ads1248的22脚,ads1248的22脚连接verf_wy,ads1248的23脚连接stm32f103cb的pa12脚,ads1248的24脚连接stm32f103cb的pb1脚,ads1248的25脚连接stm32f103cb的pb0脚,ads1248的26脚连接stm32f103cb的pa6脚,ads1248的27脚连接stm32f103cb的pa7脚,ads1248的28脚连接stm32f103cb的pa5脚;

15.所述控制器模块包括stm32f103cb芯片,在stm32f103cb芯片中,pa13端口为jtms,pa14端口为jtck,所述jtms和jtck为程序烧写接口,vbat端口连接3.3v,vss_1端口、vss_2端口、vss_3端口和vssa端口短路,连接gnd,并通过100nf和3*6*2.5轻触开关贴片的并联结构连接nrst端口,所述nrst端口通过10k电阻连接3.3v,boot0端口通过10k电阻连接gnd,并通过6.2k电阻连接外部复位信号,pb2端口通过10k电阻连接gnd,vdd_1端口、vdd_2端口、vdd_3端口和vdda端口短路,连接3.3v,并通过1μf和10nf电容的并联结构连接gnd;

16.所述串行通信模块包括maxim3232,在maxim3232中,c1+端口通过100nf电容连接v+端口,所述v+端口和c1-端口短路,并通过100nf电容连接接vref_wy,c2+端口通过100nf电容连接c2-端口,v-端口通过100nf电容连接gnd,t2out端口为串行通信的rx,r2in端口为串行通信的tx,r2out端口连接stm32f103cb的pa10脚,t2in端口连接stm32f103cb的pa9脚,gnd端口连接gnd,vcc端口连接vref_wy,并通过100nf电容连接gnd。

17.上述的一种适用于多通道模拟量同步采集的去耦电路,在控制器模块的stm32f103cb芯片中,pb6端口通过3.74k电阻连接3.3v,stm32f103cb的pb7端口通过3.74k电阻连接3.3v,所述 pb6端口和pb7端口连接i2c总线,用于测试。

18.有益效果:

19.本实用新型一种适用于多通道模拟量同步采集的去耦电路,为纯硬件电路,通过配合现有技术的算法,能够有效抑制外界对测量信号的干扰,提高测量精度和准确性。

附图说明

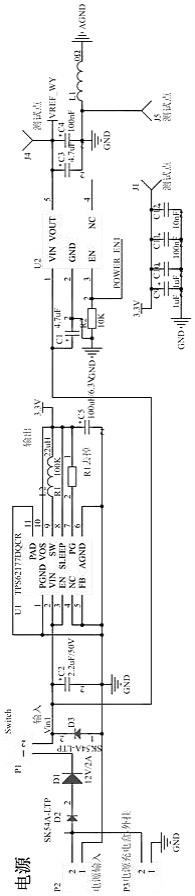

20.图1是电源模块的电路原理图。

21.图2是应变片模块的电路原理图。

22.图3是位移传感器模块的电路原理图。

23.图4是加速度传感器模块的电路原理图。

24.图5是ad转换模块的电路原理图。

25.图6是控制器模块的电路原理图。

26.图7是串行通信模块的电路原理图。

具体实施方式

27.下面结合附图对本实用新型具体实施方式作进一步详细描述。

28.具体实施方式一

29.该具体实施方式下的适用于多通道模拟量同步采集的去耦电路,包括如图1所示的电源模块,如图2所示的应变片模块,如图3所示的位移传感器模块,如图4所示的加速度传感器模块,如图5所示的ad转换模块,如图6所示的控制器模块和如图7所示的串行通信模块;

30.所述电源模块包括电源输入端、稳压芯片tps62177dqcr和低压差稳压芯片adm7160aujz-3.3-r7;

31.所述电源输入端包括电源输入,外挂电源充电盒和开关,电源输入端子的1脚和外挂电源充电盒端子的1脚短路,并通过二极管sk54a-ltp和二极管12v/2a的串联结构连接开关的1脚,电源输入端子的2脚和外挂电源充电盒端子的2脚短路,并连接gnd,开关的2脚作为电压输入,并通过二极管sk54a-ltp和2.2μf/50v电容的并联结构连接gnd;

32.在稳压芯片tps62177dqcr中,pgnd端口连接gnd,vin端口和en端口短路,并连接电压输入,nc端口、fb端口和agnd端口短路,连接gnd,pg端口通过100k电阻连接3.3v,sleep端口和vos端口短路,连接gnd,sw端口通过22uh电感连接3.3v,所述3.3v与gnd之间连接100μf/6.3v电容,3.3v为稳压输出,pad端口连接gnd;

33.在低压差稳压芯片adm7160aujz-3.3-r7中,vin端口连接电压输入,gnd端口连接gnd,并通过4.7μf电容连接电压输入,en端口通过10k电阻连接gnd,并连接stm32f103cb芯片中的pa4端口,vout端口定义为vref_wy,并通过4.7μf电容和100nf电容的并联结构连接gnd,所述gnd与agnd之间通过磁珠l1相连;

34.所述应变片模块包括应变片bf1k,bf1k的1脚通过1k电阻连接vref_wy,bf1k的2脚连接agnd,所述vref_wy通过100nf/25v电容连接agnd,通过两个1k电阻串联结构连接agnd,所述两个1k电阻串联结构抽头定义为-yb1;

35.所述位移传感器模块包括两个米朗ktr4,两个米朗ktr4的1脚短路,为vref_wy,并通过100nf/25v电容连接agnd,两个米朗ktr4的3脚短路,并连接agnd,两个米朗ktr4的1脚分别定义为+wy3和+wy4;

36.所述加速度传感器模块包括adxl203ce,在adxl203ce中,st端口连接agnd,并通过100nf/25v电容和22μf/16v电容的并联结构连接vs端口,com端口连接agnd,yout端口通过2.2μf/16v电容连接agnd,xout端口通过2.2μf/16v电容连接agnd,vs端口通过磁珠l5连接

vref_wy;

37.所述ad转换模块包括24位adc芯片ads1248,所述ads1248的1脚连接vref_wy,ads1248的2脚和3脚短路,连接gnd,ads1248的4脚连接stm32f103cb的pa11脚,ads1248的5脚连接vref_wy,ads1248的6脚连接gnd,ads1248的9脚通过1μf电容连接gnd,ads1248的10脚连接gnd,并分别通过四个5.6nf电容连接ads1248的11脚、12脚、13脚和14脚,ads1248的11脚通过47nf电容连接ads1248的12脚,并通过6.04k电阻定义为-yb1,ads1248的12脚通过6.04k电阻定义为+yb1,ads1248的13脚通过6.04k电阻连接agnd,ads1248的14脚通过6.04k电阻定义为+wy3,ads1248的15脚通过5.6nf电容连接gnd,通过47nf电容连接ads1248的16脚,并通过6.04k电阻连接agnd,ads1248的16脚通过6.04k电阻定义为+wy4,并通过5.6nf电容连接gnd,ads1248的17脚连接u10的xout脚,ads1248的18脚连接u10的yout脚,ads1248的21脚连接gnd,并通过100nf电容连接ads1248的22脚,ads1248的22脚连接verf_wy,ads1248的23脚连接stm32f103cb的pa12脚,ads1248的24脚连接stm32f103cb的pb1脚,ads1248的25脚连接stm32f103cb的pb0脚,ads1248的26脚连接stm32f103cb的pa6脚,ads1248的27脚连接stm32f103cb的pa7脚,ads1248的28脚连接stm32f103cb的pa5脚;

38.所述控制器模块包括stm32f103cb芯片,在stm32f103cb芯片中,pa13端口为jtms,pa14端口为jtck,所述jtms和jtck为程序烧写接口,vbat端口连接3.3v,vss_1端口、vss_2端口、vss_3端口和vssa端口短路,连接gnd,并通过100nf和3*6*2.5轻触开关贴片的并联结构连接nrst端口,所述nrst端口通过10k电阻连接3.3v,boot0端口通过10k电阻连接gnd,并通过6.2k电阻连接外部复位信号,pb2端口通过10k电阻连接gnd,vdd_1端口、vdd_2端口、vdd_3端口和vdda端口短路,连接3.3v,并通过1μf和10nf电容的并联结构连接gnd;

39.所述串行通信模块包括maxim3232,在maxim3232中,c1+端口通过100nf电容连接v+端口,所述v+端口和c1-端口短路,并通过100nf电容连接接vref_wy,c2+端口通过100nf电容连接c2-端口,v-端口通过100nf电容连接gnd,t2out端口为串行通信的rx,r2in端口为串行通信的tx,r2out端口连接stm32f103cb的pa10脚,t2in端口连接stm32f103cb的pa9脚,gnd端口连接gnd,vcc端口连接vref_wy,并通过100nf电容连接gnd。

40.具体实施方式二

41.该具体实施方式下的适用于多通道模拟量同步采集的去耦电路,在具体实施方式一的基础上,进一步限定:在控制器模块的stm32f103cb芯片中,pb6端口通过3.74k电阻连接3.3v,stm32f103cb的pb7端口通过3.74k电阻连接3.3v,所述 pb6端口和pb7端口连接i2c总线,用于测试。

42.需要说明的是,本实用新型已经研发出产品,为了使本技术符合实用新型保护客体,发明人特意在申报该专利之前,将程序提前公开,链接如下:https://blog.csdn.net/mengyicanglan/article/details/127361703,使得实现本技术发明目的不需要任何软件算法上的改进,仅依据本技术所公开的内容,直接下载程序,即可实现本技术。

43.还需要说明的是,该申请已经考虑到了本领域技术人员以及审查员的认知,确保所公开的技术方案,无论是本领域技术人员还是审查员,只要具备本科所涉及的电学知识(数电、模电、电路、单片机、传感器、原理图绘制和pcb绘制),都能够实现本技术,做到了公开充分。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1