一种数字修调电路及运算放大器的制作方法

本技术涉及集成电路,尤其涉及一种数字修调电路及运算放大器。

背景技术:

1、运算放大器被广泛应用在模拟集成电路中,输入失调电压是集成运算放大器的重要参数指标,任何集成运算放大器都会存在输入失调电压,输入失调电压来自于元器件的不匹配,在实际应用中,通常在流片完成后需要对运算放大器的输入失调电压进行修调以实现较小的输入失调电压,提高运算放大器的性能。

2、采用mos管作为差分对的运算放大器,其输入失调电压自身会随温度改变,变化的函数与尺寸失配、阈值电压失配、走线失配等做种因素相关,导致失调电压的温度系数存在随机性,常温测试难以反映失调电压的温度系数。

3、出于经济性和可操作性考虑,修调通常只在常温进行,因此考虑降低修调后失调电压的温度系数,主要考虑输入在修调时不额外引入随温度变化的参数。数字修调可以在运算放大器封装完成后进行,并可复用端口,不需要专门用于修调的端口,数字修调方式在高精度运算放大器中的应用有极大的优势,然而现有技术中的数字修调电路对运算放大器中的输入失调电压修调时会引入额外的随温度变化的参数,这将降低对运算放大器的修调精度。

技术实现思路

1、针对现有技术中所存在的不足,本实用新型提供了一种数字修调电路及运算放大器,其解决了现有技术中存在的数字修调电路对运算放大器中的输入失调电压修调时会引入额外的随温度变化的参数,这将降低对运算放大器的修调精度的问题。

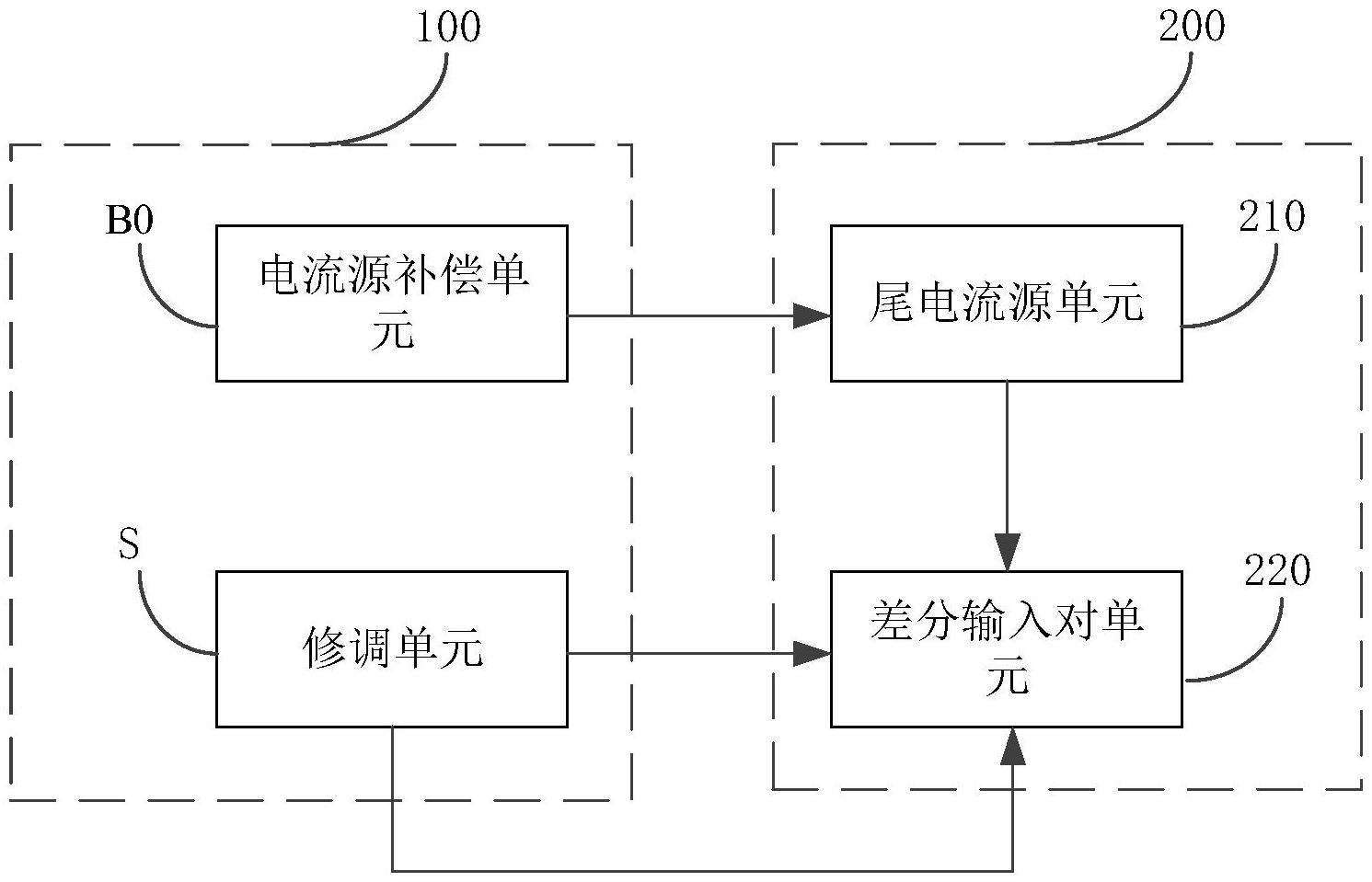

2、第一方面,本实用新型提供一种数字修调电路,应用于运算放大器,所述运算放大器包括:尾电流源单元和差分输入对单元,所述尾电流源单元与所述差分输入对单元相连,用于对所述差分输入对单元提供工作电压,所述数字修调电路:电流源补偿单元和修调单元;所述电流源补偿单元与所述尾电流源单元相连,用于对所述尾电流源单元进行补偿并产生仅包括电阻温度系数的第一补偿参数;所述修调单元与所述差分输入对单元相连,用于对所述差分输入对单元产生的输入失调电压进行修调并产生仅包括电阻温度系数的第二补偿参数,所述第二补偿参数的电阻温度系数对所述第一补偿参数的电阻温度系数抵消。

3、可选地,所述修调单元包括:修调电流源单元、第一数字选通单元和第二数字选通单元;所述修调电流源单元用于产生第一修调电流和第二修调电流;所述第一数字选通单元分别与所述修调电流源单元和所述差分输入对单元的正相电流输入端相连,用于控制所述修调电流源输入的第一修调电流,并产生包括电阻温度系数的第二补偿参数;所述第二数字选通单元分别与所述修调电流源单元和所述差分输入对单元的负相电流输入端相连,用于控制所述修调电流源输入的第二修调电流,并产生包括电阻温度系数的第二补偿参数;其中,所述第一数字选通单元和所述第二数字选通单元不同时导通。

4、可选地,所述电流源补偿单元包括:第九pmos管、第十pmos管、第三电阻、第七nmos管和第八nmos管;所述第九pmos管的栅极与所述第十pmos管的漏极相连,所述第九pmos管的源极与所述第一电源的第一端相连,所述第九pmos管的漏极与所述第七nmos管的漏极相连;所述第十pmos管的栅极与所述尾电流源的控制端相连,所述第十pmos管的源极与所述第一电源的第一端相连,所述第十pmos管的漏极与通过第三电阻与所述第八nmos管的漏极相连;所述第七nmos管的栅极与所述第八nmos管的栅极相连,所述第七nmos管的源极与所述第一电源的第二端相连,所述第七nmos管的栅极与漏极相连;所述第八nmos管的漏极与所述第一电源的第二端相连。

5、可选地,所述电流源补偿单元包括:第九pmos管、第十pmos管、第三电阻、第十一pmos管、第十二pmos管、第十nmos管、第十一nmos管、第七nmos管和第八nmos管;所述第九pmos管的栅极与所述第十pmos管的漏极相连,所述第九pmos管的源极与所述第一电源的第一端相连,所述第九pmos管的漏极与所述第十一pmos管的源极相连;所述第十pmos管的栅极与所述尾电流源的控制端相连,所述第十pmos管的源极与所述第一电源的第一端相连,所述第十pmos管的漏极与通过第三电阻与所述第十二pmos管的漏极相连;所述第十一pmos管的栅极与所述第十二pmos管的栅极相连,所述第十一pmos管的漏极与所述第十nmos管的漏极相连;所述第十二pmos管的栅极与漏极相连,所述第十二pmos管的源极与所述第三电阻的第二端相连,所述第十二pmos管的漏极与所述第十一nmos管的漏极相连;所述第十nmos管的栅极与所述第十一nmos管的栅极相连,所述第十nmos管的漏极与栅极相连,所述第十nmos管的源极与所述第七nmos管的漏极相连;所述第十一nmos管的源极与所述第八nmos管的漏极相连;所述第七nmos管的栅极与所述第八nmos管的栅极相连,所述第七nmos管的漏极与栅极相连,所述第七nmos管的源极与第一电源端的第二端相连所述第八nmos管的源极与第一电源端的第二端相连。

6、可选地,所述修调电流源单元包括:带隙基准源、内置运算放大器、第九nmos管、第八pmos管和第四电阻;所述带隙基准源的正极与所述内置运算放大器的同相输入端相连,所述带隙基准源的负极与所述第一电源的第二端相连;所述内置运算放大器的反相输入端与所述第四电阻的第一端相连,所述内置运算放大器的输出端与所述第九nmos管的栅极相连;所述第九nmos管的漏极与所述第八pmos管的漏极相连,所述第九nmos管的源极与所述第四电阻的第一端相连;所述第八pmos管的栅极分别与所述第一数字选通单元的控制端和所述第二数字选通单元的控制端相连,所述第八pmos管的源极与第一电源端的第一端相连,所述第八pmos管的漏极与栅极相连;所述第四电阻的第二端与第一电源的第二端相连。

7、可选地,所述修调电流源单元包括:第二十一pmos管、第二十二pmos管、第三p型三极管、第四p型三极管、第六n型三极管、第七n型三极管、第一电阻、第七电阻、第九n型三极管、第八电阻、第八n型三极管、第九电阻、第八pmos管、第十n型三极管和第四电阻;所述第二十一pmos管的栅极与所述第二十二pmos管的栅极相连,所述第二十一pmos管的源极与第一电源的第一端相连,所述第二十一pmos管的漏极分别与所述第三p型三极管的发射极、第四p型三极管的发射极、所述第九n型三极管的基极和所述第十n型三极管的基极相连;所述第二十二pmos管的源极与所述第一电源的第一端相连,所述第二十二pmos管的栅极与漏极相连,所述第二十二pmos管的漏极与所述第八n型三极管的集电极相连;所述第三p型三极管的基极与所述第四p型三极管的基极相连,所述第三p型三极管的集电极与所述第六n型三极管的集电极相连;所述第四p型三极管的基极和集电极相连,所述第四p型三极管的集电极与所述第七n型三极管的发射极相连;所述第六n型三极管的基极分别与所述第七n型三极管的基极相连,所述第六n型三极管的发射极与所述第一电阻的第二端相连;所述第七n型三极管的发射极与所述第一电阻的第一端相连;所述第七电阻的第一端与所述第一电阻的第二端相连,所述第七电阻的第二端与所述第一电源的第二端相连;所述第八电阻的第一端与所述第七n型三极管的栅极相连,所述第八电阻的第二端与第一电源的第二端相连;所述第九n型三极管的集电极第一电源的第一端相连,所述第九n型三极管的发射极与所述第八n型三极管的基极相连;所述第八pmos管的栅极分别与所述第一数字选通单元和所述第二数字选通单元的控制端相连,所述第八pmos管的栅极与漏极相连,所述第八pmos管的源极与第一电源的第一端相连,所述第八pmos管的漏极与所述第十n型三极管的集电极相连;所述第十n型三极管的发射极通过所述第四电阻与所述第一电源的第二端相连。

8、可选地,所述每个数字选通单元包括:若干个pmos管和数字选通模块;所述每个pmos管的栅极与所述第八pmos管的栅极相连,所述每个pmos管的源极与所述第一电源的第一端,所述每个pmos管的漏极与所述数字选通模块相连;所述数字选通模块还与差分输入对单元相连。

9、可选地,所述修调电流源单元包括:第十三pmos管、第十四pmos管、第十五pmos管、第十六pmos管、第十二nmos管、第十三nmos管、第十四nmos管、第一电容、第九nmos管、第五电阻、第六电阻、第一电阻、第一p型三极管、第二p型三极管;所述第十三pmos管的栅极分别与所述第十pmos管的栅极所述第十四pmos管的栅极相连,所述第十三pmos管的源极与所述第一电源的第一端相连,所述第十三pmos管的漏极与所述第十五pmos管的源极和所述第十六pmos管的源极相连;所述第十四pmos管的源极与所述第一电源的第一端相连,所述第十四pmos管的漏极与所述第十四nmos管的漏极和所述第九nmos管的栅极相连;所述第十五pmos管的栅极与所述第五电阻的第二端和所述第一电阻的第一端相连,所述第十五pmos管的漏极与所述第十二nmos管的漏极相连;所述第十六pmos管的栅极分别与所述第六电阻的第二端和所述第二p型三极管的发射极相连,所述第十六pmos管的漏极与所述第十三nmos管的漏极相连;所述第十二nmos管的栅极与所述第十三nmos管的栅极相连,所述第十二nmos管的漏极与栅极相连,所述第十二nmos管的源极与所述第一电源的第二端相连;所述第十三nmos管的漏极还分别与所述第一电容的第一端和所述第十四nmos管的栅极相连,所述第十三nmos管的源极所述第一电源的第二端相连;所述第十四nmos管的漏极还与所述第一电容的第二端相连,所述第十四nmos管的源极还与所述第一电源的第二端相连;所述第九nmos管的漏极与所述第一电源的第一端相连,所述第九nmos管的源极分别与所述第五电阻的第一端和和所述第六电阻的第一端相连;所述第一电阻的第二端与所述第一p型三极管的发射极相连;所述第一p型三极管的基极和集电极与第一电源的第二端相连;所述第二p型三极管的基极和集电极与第一电源的第二端相连。

10、可选地,所述每个数字选通单元包括:数字选通模块和若干个修调电流控制模块,所述每个修调电流控制模块包括:pmos管和修调电阻;所述数字选通模块的第一端与所述差分输入对单元相连;所述pmos管的栅极与所述第九nmos管的栅极相连,所述pmos管的漏极与所述修调电阻的第一端相连,所述pmos管的源极与所述修调电阻的第一端相连;所述修调电阻的第二端与所述第一电源的第二端相连。

11、第二方面,本实用新型提供一种运算放大器,包括权利上述数字修调电路,所述运算放大器包括:第三pmos管、第一pmos管、第二pmos管和有源负载;所述第三pmos管的栅极与所述电流源补偿单元相连,所述第三pmos管的源极与所述第一电源的第一端相连,所述第三pmos管的漏极分别与所述第一pmos管的源极和所述第二pmos管的源极相连;所述第一pmos管的栅极作为输入信号的正相输入端,所述第一pmos管的漏极与所述有源负载相连;所述第二pmos管的栅极作为输入信号的反相输入端,所述第二pmos管的漏极与所述有源负载相连;所述有源负载还与所述第一电源的第二端相连。

12、第三方面,本实用新型提供一种运算放大器,包括上述数字修调电路,所述运算放大器包括:第一pmos管、第二pmos管、第三pmos管、第四pmos管、第十一n型三极管、第十二n型三极管、第十三n型三极管、第十四n型三极管、第十五n型三极管、第十电阻、第十一电阻和第二电容;所述第三pmos管的栅极与所述电流源补偿单元相连,所述第三pmos管的源极与所述第一电源的第一端相连,所述第三pmos管的漏极分别与所述第一pmos管的源极和所述第二pmos管的源极相连;所述第一pmos管的栅极作为输入信号的正相输入端,所述第一pmos管的漏极分别与所述第十一n型三极管的集电极和所述第十三n型三极管的基极相连;所述第二pmos管的栅极作为输入信号的反相输入端,所述第二pmos管的漏极分别与所述第十二n型三极管的集电极和所述第十四n型三极管的基极相连;所述第四pmos管的栅极与所述第三pmos管的栅极相连,所述第四pmos管的源极与第一电源的源极相连,所述第四pmos管的发射极与第十五n型三极管的集电极相连;所述第十一n型三极管的基极与所述第十二n型三极管的基极相连,所述第十一n型三极管的发射极与第一电源的第二端相连;所述第十二n型三极管的发射极与第一电源的第二端相连;所述第十电阻的两端分别与所述第十二n型三极管的基极和发射极相连;所述第十三n型三极管的集电极与所述第一电源的第一端相连,所述第十三n型三极管的发射极与所述第十二n型三极管的基极相连;所述第十四n型三极管的集电极与所述第一电源的第一端相连,所述第十四n型三极管的发射极与所述第十一电阻的第一端相连;所述第十一电阻的第二端与第一电源的第二端相连;所述第十五n型三极管的基极与所述第十四n型三极管的发射极相连,所述第十五n型三极管的发射极与第一电源的第二端相连。

13、第四方面,本实用新型提供一种运算放大器,包括上述数字修调电路,所述运算放大器包括:第一pmos管、第二pmos管、第三pmos管、第十七pmos管、第十八pmos管、第十九pmos管、第二十pmos管、第十七nmos管、第十八nmos管、第十五nmos管和第十六nmos管;所述第三pmos管的栅极与所述电流源补偿单元相连,所述第三pmos管的源极与所述第一电源的第一端相连,所述第三pmos管的漏极分别与所述第一pmos管的源极和所述第二pmos管的源极相连;所述第一pmos管的栅极作为输入信号的正相输入端,所述第一pmos管的漏极分别与所述第一数字选通单元的数字选通模块、第十五nmos管的漏极和第十七nmos管的漏极相连;所述第二pmos管的栅极作为输入信号的反相输入端,所述第二pmos管的漏极分别与所述第二数字选通单元的数字选通模块、第十六nmos管的漏极和第十八nmos管的漏极相连;所述第十九pmos管的栅极分别与所述第二十pmos管的栅极和所述第十七pmos管的漏极相连,所述第十九pmos管的源极与所述第一电源的第一端相连,所述第十九pmos管的漏极与所述第十七pmos管的源极相连;所述第二十pmos管的源极与所述第一电源的第一端相连,所述第二十pmos管的漏极与所述第十八pmos管的源极相连;所述第十七pmos管的栅极接第三偏置电压并与所述第十八pmos管的栅极相连,所述第十七pmos管的漏极与所述第十七nmos管的漏极相连;所述第十八pmos管的漏极与所述第十八nmos管的漏极相连;所述第十七nmos管的栅极接第二偏置电压并与所述第十八nmos管的栅极相连;所述第十五nmos管的栅极接第一偏置电压并与所述第十六nmos管的栅极相连,所述第十五nmos管源极分别与所述第十六nmos管的源极和第一电源的第二端相连。

14、相比于现有技术,本实用新型具有如下有益效果:

15、通过电流源补偿单元对尾电流源单元进行补偿并产生仅包括电阻温度系数的第一补偿参数,修调单元对输入失调电压进行修调,修调产生仅包括电阻温度系数的第二补偿参数,第二补偿参数的电阻温度系数对第一补偿参数的电阻温度系数抵消,因此本技术方案的修调电路最终不包括随温度变化的参数,从而实现不引入额外的随温度变化的参数,提高运算放大器的修调精度。

- 还没有人留言评论。精彩留言会获得点赞!