三维存储器器件及其制造方法与流程

背景技术:

1、本公开的实施例涉及三维(3d)存储器器件及其制造方法。

2、通过改进工艺技术、电路设计、编程算法和制造工艺,平面存储器单元缩小到更小的尺寸。然而,随着存储器单元的特征尺寸接近下限,平面工艺和制造技术变得具有挑战性并且成本高昂。结果,用于平面存储器单元的存储器密度接近上限。

3、3d存储器架构可以解决平面存储器单元中的密度上限。3d存储器架构包括存储器阵列和用于控制通往和来自存储器阵列的信号的外围器件。

技术实现思路

1、本文公开了用于形成3d存储器器件的栅极结构的方法及其制造方法的实施例。

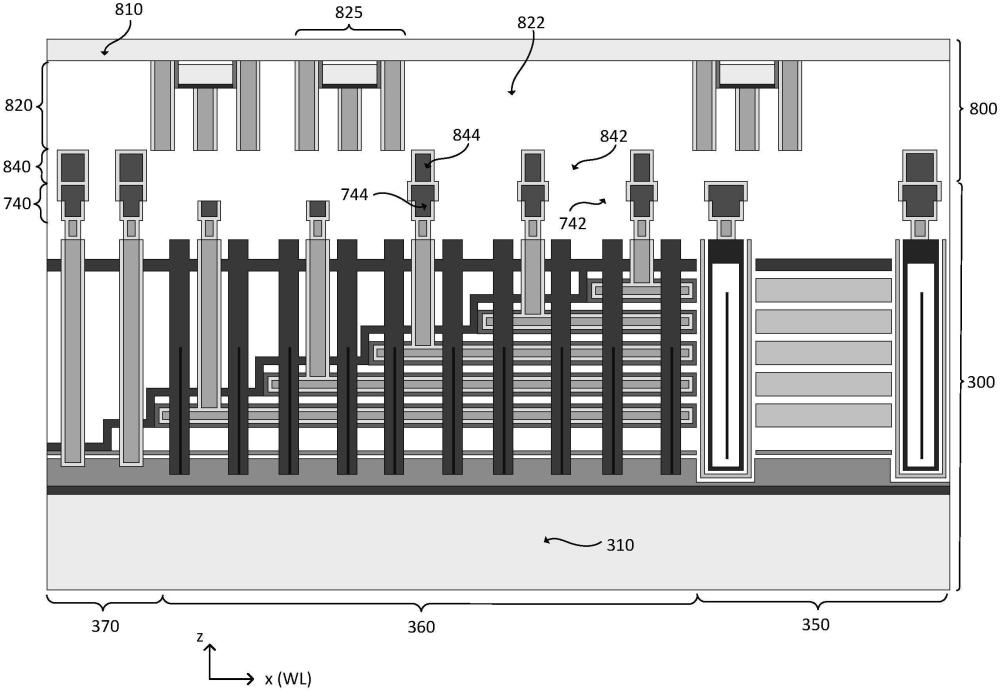

2、公开了一种用于形成三维(3d)nand存储器器件的方法,包括:形成包括核心阵列区域、阶梯区域和外围区域的阵列晶圆,包括:在第一衬底上形成交替电介质堆叠体,在核心阵列区域中的交替电介质堆叠体中形成多个沟道结构,每个沟道结构包括功能层和沟道层,在阶梯区域中形成阶梯结构,并且形成多个虚设沟道结构,以及将cmos晶圆键合到阵列晶圆;以及去除第一衬底;去除每个沟道结构的功能层的一部分以暴露沟道层,并且对沟道层的暴露部分进行掺杂。

3、在一些实施例中,该方法还可以包括:在形成交替电介质堆叠体之前,在第一衬底上形成支撑堆叠体,其中,交替电介质堆叠体形成在支撑堆叠体上;以及在去除每个沟道结构的功能层的部分之前,去除支撑堆叠体的部分。

4、在一些实施例中,形成多个虚设沟道结构包括:形成穿透交替电介质堆叠体和支撑堆叠体并且延伸到第一衬底中的多个虚设沟道结构。

5、在一些实施例中,形成多个虚设沟道结构包括:形成穿透交替电介质堆叠体而不穿透支撑堆叠体的多个虚设沟道结构。

6、在一些实施例中,形成阵列晶圆还包括:形成穿透交替电介质堆叠体和支撑堆叠体的多个缝隙;以及在每个缝隙中形成阵列公共源极触点。

7、在一些实施例中,该方法还可以包括:将交替电介质堆叠体转变为交替导体/电介质堆叠体。

8、在一些实施例中,形成阵列晶圆还包括:在阶梯区域中形成多个字线触点;以及在外围区域中形成多个外围触点。

9、在一些实施例中,形成阵列晶圆还包括:形成包括多个互连触点的阵列接合层;其中,将cmos晶圆键合到阵列晶圆的阵列接合层。

10、在一些实施例中,将cmos晶圆键合到阵列晶圆包括:制备包括第二衬底、在第二衬底上的外围电路层以及在外围电路层上的cmos接合层的cmos晶圆;以及将cmos晶圆的cmos接合层键合到阵列晶圆的阵列接合层,以形成键合结构。

11、在一些实施例中,该方法还可以包括:形成支撑堆叠体包括:在第一衬底上形成牺牲电介质层;在牺牲电介质层上形成第一半导体层;以及在第一半导体层上形成第二半导体层。

12、在一些实施例中,去除支撑堆叠体的部分和第一衬底包括:通过使用牺牲电介质层作为蚀刻停止层来去除第一衬底;去除牺牲电介质层在核心阵列区域和外围区域中的部分;以及去除第一半导体层在核心阵列区域和外围区域中的部分。

13、在一些实施例中,该方法还可以包括:去除每个沟道结构的功能层的部分包括:去除每个沟道结构的阻挡层、存储层和隧穿层位于第二半导体层之上的部分;以及同时去除牺牲电介质层在阶梯区域中的部分。

14、在一些实施例中,该方法还可以包括:形成与每个沟道结构的沟道层的掺杂部分电连接的补充半导体层。

15、在一些实施例中,该方法还可以包括:在补充半导体层上形成焊盘层,并且焊盘层与每个沟道结构的沟道层电连接。

16、在一些实施例中,形成交替电介质堆叠体包括:形成堆叠在支撑堆叠体上的多个电介质层对,每个电介质层对包括第一电介质层和不同于第一电介质层的第二电介质层。

17、在一些实施例中,将交替电介质堆叠体转变为交替导体/电介质堆叠体包括:通过缝隙去除在交替电介质堆叠体中的多个第二电介质层,以形成多个水平沟槽;以及在每个水平沟槽中形成栅极结构。

18、另一方面是一种三维(3d)存储器器件,包括:cmos晶圆;以及连接在cmos晶圆上的阵列晶圆,阵列晶圆包括核心阵列区域、阶梯区域和外围区域,阵列晶圆包括:交替导体/电介质堆叠体,包括在阶梯区域中的阶梯结构,以及在核心阵列区域中的交替导体/电介质堆叠体中的多个沟道结构,每个沟道结构包括功能层和沟道层,并且沟道层包括掺杂部分,穿透交替导体/电介质堆叠体的多个虚设沟道结构,以及在阶梯区域中的支撑堆叠体。

19、在一些实施例中,该器件还可以包括:与每个沟道结构的沟道层的掺杂部分电连接的补充半导体层;以及在补充半导体层上并且与每个沟道结构的沟道层电连接的焊盘层。

20、在一些实施例中,每个虚设沟道结构的上端与补充半导体层接触。

21、在一些实施例中,每个虚设沟道结构的上端与支撑堆叠体的第一半导体层接触。

22、在一些实施例中,该器件还可以包括:穿透交替导体/电介质堆叠体的多个缝隙;以及在每个缝隙中并且电连接到补充半导体层的阵列公共源极触点。

23、在一些实施例中,阵列晶圆还包括:在阶梯区域中的多个字线触点;以及在外围区域中的多个外围触点。

24、本领域技术人员可以根据本公开的说明书、权利要求和附图来理解本公开的其他方面。

技术特征:

1.一种用于形成三维(3d)存储器器件的方法,包括:

2.根据权利要求1所述的方法,还包括:

3.根据权利要求2所述的方法,其中,形成所述多个虚设沟道结构包括:

4.根据权利要求2所述的方法,其中,形成所述多个虚设沟道结构包括:

5.根据权利要求2所述的方法,其中,形成所述阵列晶圆还包括:

6.根据权利要求1所述的方法,还包括:

7.根据权利要求1所述的方法,其中,形成所述阵列晶圆还包括:

8.根据权利要求2所述的方法,其中,形成所述阵列晶圆还包括:

9.根据权利要求8所述的方法,其中,将所述cmos晶圆键合到所述阵列晶圆包括:

10.根据权利要求8所述的方法,其中,形成所述支撑堆叠体包括:

11.根据权利要求10所述的方法,其中,去除所述支撑堆叠体的部分和所述第一衬底包括:

12.根据权利要求10所述的方法,其中,去除每个沟道结构的功能层的所述部分包括:

13.根据权利要求1所述的方法,还包括:

14.根据权利要求13所述的方法,还包括:

15.根据权利要求6所述的方法,其中,形成所述交替电介质堆叠体包括:

16.根据权利要求15所述的方法,其中,将所述交替电介质堆叠体转变为所述交替导体/电介质堆叠体包括:

17.一种三维(3d)存储器器件,包括:

18.根据权利要求17所述的器件,还包括:

19.根据权利要求18所述的器件,其中,每个虚设沟道结构的上端与所述补充半导体层接触。

20.根据权利要求18所述的器件,其中,每个虚设沟道结构的上端与所述支撑堆叠体的第一半导体层接触。

21.根据权利要求18所述的器件,还包括:

22.根据权利要求17所述的器件,其中,所述阵列晶圆还包括:

技术总结

提供了一种用于形成3D存储器器件的方法。该方法包括:形成包括核心阵列区域、阶梯区域和外围区域的阵列晶圆。形成阵列晶圆包括:在第一衬底上形成交替电介质堆叠体,在核心阵列区域中的交替电介质堆叠体中形成多个沟道结构,每个沟道结构包括功能层和沟道层,在阶梯区域中形成阶梯结构,以及形成多个虚设沟道结构。该方法还包括:将CMOS晶圆键合到阵列晶圆;以及去除第一衬底;去除每个沟道结构的功能层的部分以暴露沟道层,以及对沟道层的暴露部分进行掺杂。

技术研发人员:张坤

受保护的技术使用者:长江存储科技有限责任公司

技术研发日:

技术公布日:2024/1/5

- 还没有人留言评论。精彩留言会获得点赞!