用于电源电压高于内核电源电压的输出缓冲器的自适应栅极偏置调节器的制作方法

本发明涉及输出缓冲器电路,并且更具体地涉及用于多电源设备的电平移位缓冲器。

背景技术:

1、半导体工艺的进步已经导致更小尺寸的晶体管和更低的电源电压。这些较小的晶体管具有较薄的栅极氧化物层和可能会被相对较低的电压损坏的其他层。因此,可以施加到这些较小晶体管的最大电压降低了。

2、半导体集成电路(ic)或芯片的内核中的密集逻辑可以使用较低的电源电压来提供最快的速度。较高的电源电压可以用于去往印刷电路板(pcb)或其他基板上的其他芯片或组件的输入/输出(i/o)接口。

3、图1示出了i/o的电源电压较高、内核的电源电压较低的芯片。内核102具有许多晶体管10,所述晶体管10可以被布置用于逻辑、存储器或其他电路。内核102由诸如1.8伏的低电源电压供电。该低电源电压防止了对内核晶体管10的损坏。

4、内核102使用i/o 104连接至外部接口。i/o 104具有较高的电源电压,诸如3.3伏。i/o 104中的电平移位器可以将来自内核102的1.8伏高电平移位到i/o接口的更高的3.3伏高电平。

5、i/o 104具有许多晶体管12,所述晶体管形成电平移位器、输入和输出缓冲器以及其他组件。为了更好的过压保护,这些i/o晶体管12可能具有更长的沟道长度,但是在标准的半导体工艺中它们的栅极氧化物与内核晶体管10的栅极氧化物厚度相同。因此,i/o 104中的晶体管12容易遭受来自较高的3.3伏i/o电源电压的损坏。晶体管12的过压可能导致产品寿命期间的即时故障、泄漏或可靠性问题。

6、图2a-2b示出了用于过压保护的共源共栅输出缓冲器。在图2a中,共源共栅晶体管22、24被插入在3.3伏电源和地电平之间的p沟道驱动器晶体管20和n沟道驱动器晶体管26之间。偏置电压pbias被施加到p沟道共源共栅晶体管22的栅极,而偏置电压nbias被施加到n沟道共源共栅晶体管24的栅极。在一些应用中,pbias和nbias可以是相同的固定电压。n沟道驱动器晶体管26的栅极接收输入数据in,而p沟道驱动器晶体管20的栅极接收电平移位的输入in_sh,其中高电平已经从1.8伏移位到3.3伏。

7、在图2b中,输入in在地电平和1.8伏之间摆动,而移位输入in_sh在1.8伏的低电平至3.3伏的高电平之间摆动。偏置电压pbias和nbias为1.8伏。i/o焊盘从3.3伏摆动到0伏(地电平)。

8、i/o焊盘和地电平之间的电压分散在两个晶体管24、26上,从而减少了任一单个晶体管上的电压应力。同样,3.3伏i/o电源和i/o焊盘之间的电压跨两个晶体管20、22分布。共源共栅晶体管22提供了附加的沟道电阻,其降低了施加到p沟道驱动器晶体管20的电压。此外,共源共栅晶体管24提供了附加的沟道电阻,其降低了施加到n沟道驱动器晶体管26的电压。晶体管20、22之间的节点p1在3.3v和1.8v之间摆动,而晶体管24、26之间的节点n1在1.8v和地电平之间摆动。在稳态下,所有晶体管的漏极-源极(vds)和栅极-源极(vgs)小于2伏,从而防止过压损坏。

9、然而,在电压转换期间,可能在共源共栅晶体管22、24上施加更大的电压应力,从而导致潜在的可靠性问题。当焊盘最初在3.3伏处,并且in切换为高时,n沟道驱动器晶体管26可以导通,并且迅速将节点n1拉向地电平。在切换转变期间,n沟道共源共栅晶体管24可以具有多于2伏的vds。p沟道共源共栅晶体管22可能具有在焊盘从低到高转变时施加的类似瞬态过压应力。这些瞬态过压应力是不合期望的。

10、所期望的是一种电平移位输出缓冲器,其晶体管上的过压应力减小。期望一种电平移位输出缓冲器,其调整到共源共栅晶体管的偏置电压以降低电压应力。具有自适应调节器的输出缓冲器,用于动态调整共源共栅栅极偏置。

技术实现思路

技术特征:

1.一种共源共栅偏置升压输出缓冲器,包括:

2.根据权利要求1所述的共源共栅偏置升压输出缓冲器,其中所述上自适应调节器包括:

3.根据权利要求2所述的共源共栅偏置升压输出缓冲器,其中下自适应调节器包括:

4.根据权利要求3所述的共源共栅偏置升压输出缓冲器,其中上n沟道旁路晶体管、上n沟道钳位晶体管和上n沟道栅极偏置晶体管的衬底连接到上调节器输出;

5.根据权利要求3所述的共源共栅偏置提升输出缓冲器,进一步包括:

6.根据权利要求5所述的共源共栅偏置升压输出缓冲器,其中共源共栅偏置缓冲器在第三数据信号指示p沟道驱动器晶体管关断时将中间偏置驱动至上共源共栅栅极节点,并且在第三数据信号指示p沟道驱动器晶体管导通时使用上调节器输出来驱动所述上共源共栅栅极节点;

7.根据权利要求6所述的共源共栅偏置升压输出缓冲器,其中中间偏置电压与上电源的上电源电压相比更低至少30%。

8.根据权利要求7所述的共源共栅偏置升压输出缓冲器,进一步包括:

9.根据权利要求8所述的共源共栅偏置升压输出缓冲器,其中预驱动器和下缓冲器由中间偏置供电。

10.根据权利要求9所述的共源共栅偏置升压输出缓冲器,进一步包括:

11.根据权利要求10所述的共源共栅偏置升压输出缓冲器,进一步包括:

12.一种偏置升压输出缓冲器,包括:

13.根据权利要求12所述的偏置升压输出缓冲器,其中第二自适应调节器包括:

14.根据权利要求13所述的偏置升压输出缓冲器,其中所述第一自适应调节器包括:

15.根据权利要求14所述的偏置升压输出缓冲器,进一步包括:

16.根据权利要求15所述的偏置升压输出缓冲器,进一步包括:

17.一种输出缓冲器,包括:

18.根据权利要求17所述的输出缓冲器,其中所述上自适应调节器装置进一步包括:

19.根据权利要求18所述的输出缓冲器,其中下自适应调节器装置进一步包括:

20.根据权利要求19所述的输出缓冲器,其中上n沟道旁路晶体管装置、上n沟道钳位晶体管装置和上n沟道栅极偏置晶体管装置的衬底连接到上调节输出;

技术总结

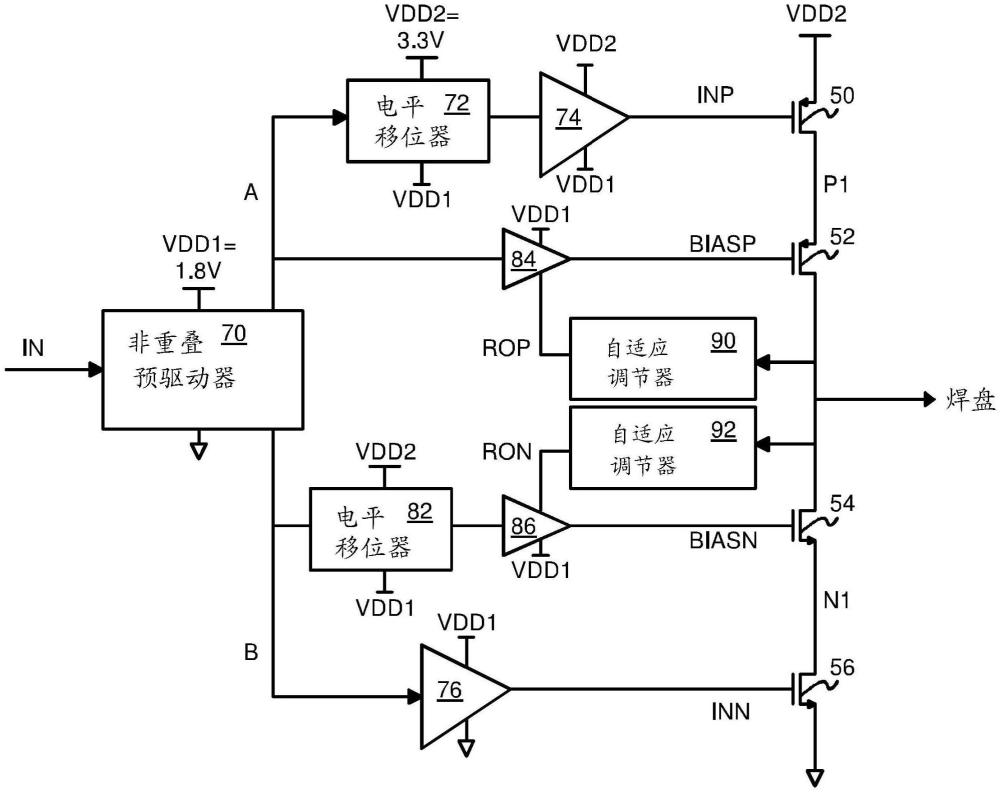

一种电平移位输出缓冲器具有共源共栅放大器晶体管,所述共源共栅放大器晶体管具有变化的而不是固定的栅极偏置电压。当I/O开始切换时,自适应调节器将I/O焊盘电压旁路至调节器输出,但是稍后将调节器输出钳位至中间偏置电压。调节器输出可以施加到驱动共源共栅晶体管栅极的缓冲器的电源端。由于自适应调节器在开关开始时跟随I/O焊盘电压,因此向共源共栅晶体管的栅极提供升压,从而允许更高的电流或更小的共源共栅晶体管,并且防止过压应力。自适应调节器具有在I/O焊盘和调节器输出之间的n沟道旁路晶体管,以及在调节器输出和中间偏置之间的n沟道钳位晶体管,其栅极由p沟道栅极偏置晶体管或n沟道栅极偏置晶体管从I/O焊盘驱动。

技术研发人员:陈捷生,任俊杰

受保护的技术使用者:香港应用科技研究院有限公司

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!