用于DELTA-SIGMA模数转换器的数字滤波器的制作方法

背景技术:

1、模数转换器(adc)有各种应用。adc将输入模拟信号转换为数字输出值。一种类型的adc是delta-sigma adc。delta-sigma adc包括耦合到滤波器的delta-sigma调制器。delta-sigma调制器接收输入模拟信号并生成包括一组逻辑0和1的输出调制器数据。在给定时间段内逻辑0的数量相对于逻辑1的数量是输入模拟信号幅值的函数。滤波器接收来自delta-sigma调制器的输出调制器数据。滤波器衰减高频噪声并抽取滤波后的调制器数据,以产生较低数据速率的输出值(低于delta-sigma调制器的采样率)。

技术实现思路

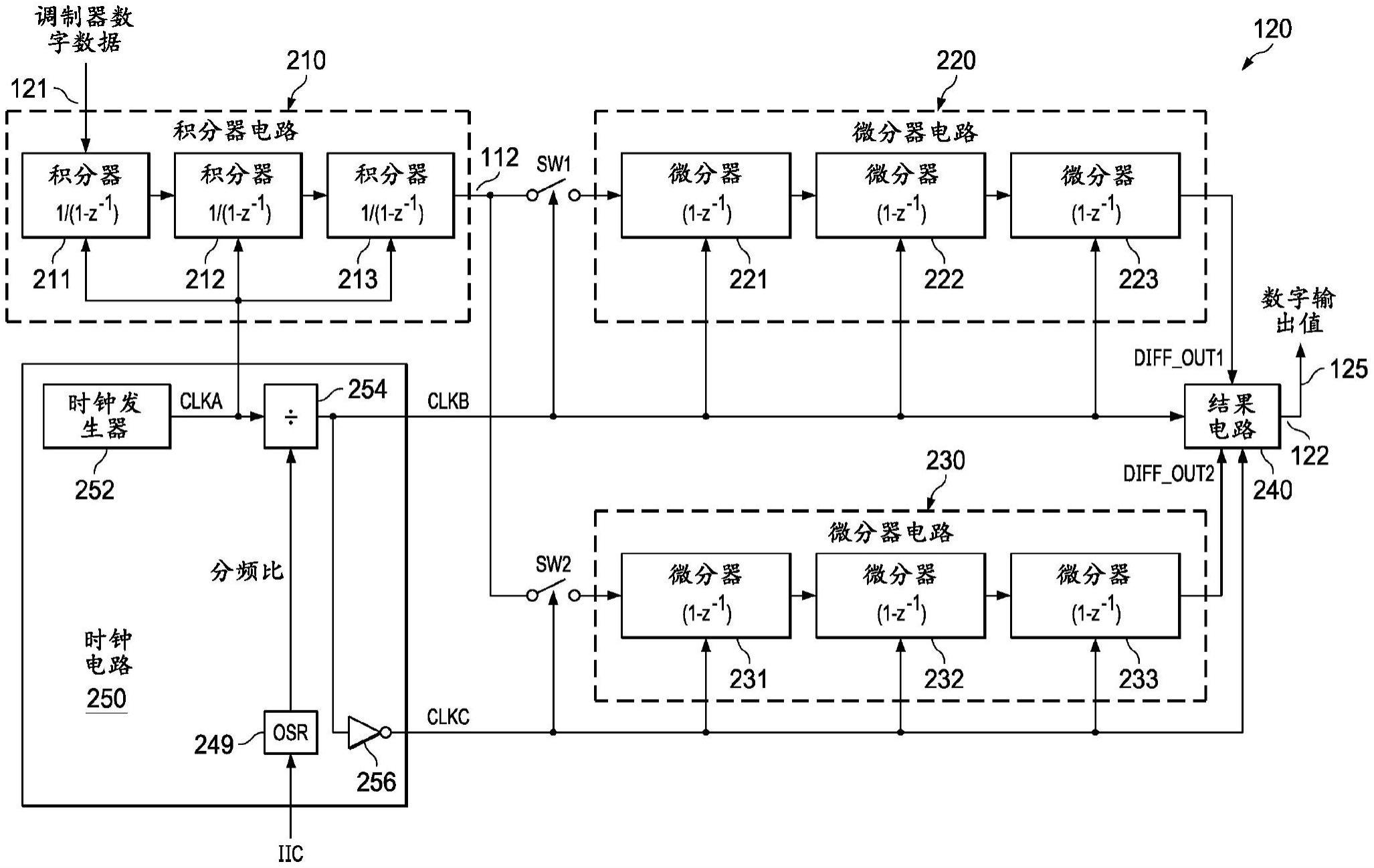

1、在一个示例中,一种模数转换器(adc)包括调制器、积分器电路以及第一微分器电路和第二微分器电路。调制器具有调制器输入端和调制器输出端。调制器输入端被配置为接收模拟信号,并且调制器被配置为在调制器输出端上生成数字数据。积分器电路具有积分器电路输入端和积分器输出端。积分器输入端耦合到调制器输出端。第一微分器电路耦合到积分器输出端,并且第一微分器电路被配置为以第一时钟被钟控。第二微分器电路耦合到积分器输出端,并且第二微分器电路被配置为以第二时钟被钟控。第二时钟相对于第一时钟异相。

技术特征:

1.一种用于模数转换器的滤波器,所述滤波器包括:

2.根据权利要求1所述的滤波器,其中,所述滤波器进一步包括结果电路,所述结果电路耦合到所述第一微分器的数据输出端和所述第二微分器的数据输出端。

3.根据权利要求2所述的滤波器,其中,所述结果电路包括多路复用器。

4.根据权利要求1所述的滤波器,进一步包括:

5.根据权利要求1所述的滤波器,其中,所述第三时钟是所述第二时钟的逻辑反相时钟。

6.根据权利要求1所述的滤波器,其中,所述时钟电路被配置为生成第四时钟,所述第四时钟具有所述第二频率并且相对于所述第二时钟和所述第三时钟异相,所述滤波器进一步包括第三微分器,所述第三微分器具有第三微分器时钟输入端,所述第三微分器时钟输入端被配置为接收所述第四时钟。

7.根据权利要求6所述的滤波器,进一步包括第三开关,所述第三开关耦合在所述第一积分器与所述第三微分器之间,所述第三开关被配置为接收所述第四时钟。

8.一种模数转换器(adc),包括:

9.根据权利要求8所述的adc,其中,所述调制器是delta-sigma调制器。

10.根据权利要求8所述的adc,其中,所述第一微分器电路包括至少两个第一微分器电路微分器,并且所述第二微分器电路包括至少两个第二微分器电路微分器,所述至少两个第一微分器电路微分器被配置为以所述第一时钟被钟控,并且所述至少两个第二微分器电路微分器被配置为以所述第二时钟被钟控。

11.根据权利要求8所述的adc,其中:

12.根据权利要求8所述的adc,其中,所述第一微分器电路具有第一微分器电路输出端,并且所述第二微分器电路具有第二微分器电路输出端,并且所述adc进一步包括耦合到所述第一微分器电路输出端和所述第二微分器电路输出端的结果电路。

13.根据权利要求12所述的adc,其中:

14.根据权利要求8所述的adc,其中,所述第一时钟和所述第二时钟相对于彼此异相180度。

15.根据权利要求8所述的adc,进一步包括:

16.根据权利要求15所述的adc,其中,所述第一时钟、所述第二时钟和所述第三时钟具有相同的频率。

17.根据权利要求8所述的adc,进一步包括:

18.一种模数转换器(adc),包括:

19.根据权利要求18所述的adc,其中,所述结果电路包括寄存器或至少一个多路复用器。

20.根据权利要求18所述的adc,其中:

技术总结

一种模数转换器(ADC)包括调制器、积分器电路(210)以及第一和第二微分器电路(220,230)。调制器具有调制器输入端和调制器输出端。调制器输入端被配置为接收模拟信号,并且调制器被配置为在调制器输出端上生成数字数据。积分器电路(210)具有积分器电路输入端和积分器输出端。积分器输入端耦合到调制器输出端。第一微分器电路(220)耦合到积分器输出端,并且第一微分器电路(220)被配置为以第一时钟被钟控。第二微分器电路(230)耦合到积分器输出端,并且第二微分器电路(230)被配置为以第二时钟被钟控。第二时钟相对于第一时钟异相。

技术研发人员:V·阿肯迪拉贾拉胡帕蒂

受保护的技术使用者:德克萨斯仪器股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!