具有多层级漏极选择电极的三维存储器器件及其形成方法与流程

本公开整体涉及半导体器件的领域,且具体地讲涉及具有电连接位于不同层级处的多个漏极选择层级导电层的漏极选择层级接触通孔结构的三维存储器器件及其形成方法。

背景技术:

1、包括每个单元具有一个位的三维竖直nand串的三维存储器器件在t.endoh等人的标题为“novel ultra high-density memory with a stacked-surrounding gatetransistor(s-sgt)structured cell”,iedm proc.(2001)33-36的文章中公开。

技术实现思路

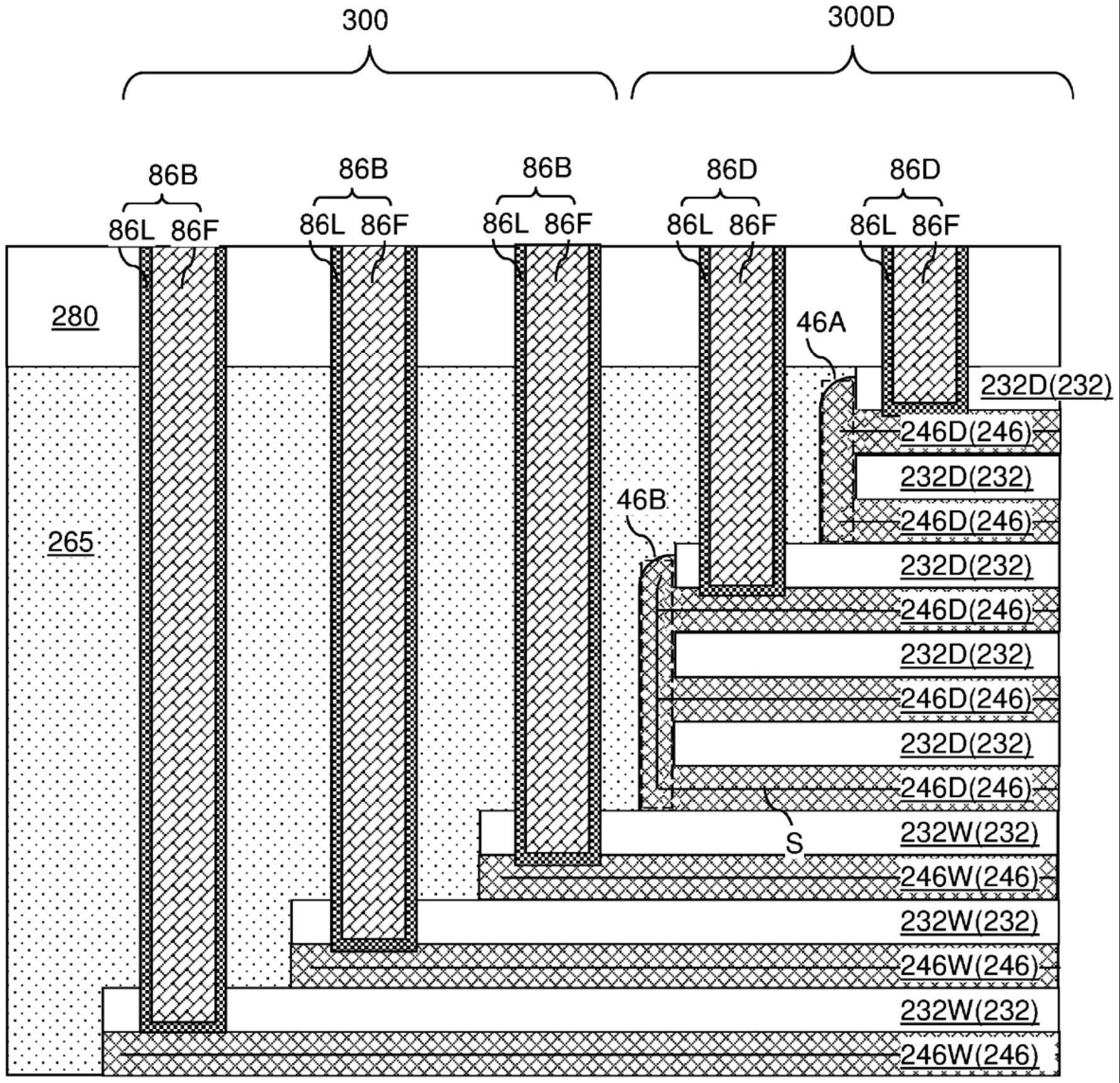

1、根据本公开的一方面,一种三维存储器器件包括:绝缘层和导电层的交替堆叠,其中所述导电层包括字线层级导电层和位于所述字线层级导电层上方的漏极选择层级导电层;存储器开口填充结构,所述存储器开口填充结构在其中存在所述交替堆叠内的每个层的存储器阵列区域中竖直延伸穿过所述交替堆叠,其中所述存储器开口填充结构中的每个存储器开口填充结构包括竖直半导体沟道和存储器膜;和漏极选择层级接触通孔结构。所述漏极选择层级接触结构中的第一漏极选择层级接触结构直接接触所述漏极选择层级导电层中的彼此竖直间隔开的至少前两个漏极选择层级导电层。所述漏极选择层级接触结构中的第二漏极选择层级接触结构直接接触所述漏极选择层级导电层中的至少接下来两个漏极选择层级导电层,所述接下来两个漏极选择层级导电层彼此竖直间隔开并且位于所述漏极选择层级导电层中的至少所述前两个漏极选择层级导电层下方。

2、根据本公开的另一方面,一种形成三维存储器器件的方法,所述方法包括:在衬底上方形成绝缘层和牺牲材料层的交替堆叠,其中所述牺牲材料层包括字线层级牺牲材料层和覆盖在所述字线层级牺牲材料层上面的漏极选择层级牺牲材料层;通过图案化所述漏极选择层级牺牲材料层来形成阶梯式表面;在所述阶梯式表面上方形成后向阶梯式介电材料部分;穿过所述交替堆叠在其中存在所述交替堆叠的每个层的存储器阵列区域中形成存储器堆叠结构,其中所述存储器堆叠结构中的每个存储器堆叠结构包括存储器膜和竖直半导体沟道;分别用所述字线层级导电层和漏极选择层级导电层替换所述字线层级牺牲材料层和所述漏极选择层级牺牲材料层;形成延伸穿过所述漏极选择层级导电层的漏极选择层级隔离结构,其中所述漏极选择层级导电层中的每个漏极选择层级导电层分成相应一组漏极选择层级导电条带,所述相应一组漏极选择层级导电条带包括通过所述漏极选择层级隔离结构彼此横向间隔开的漏极侧选择栅极电极;以及直接在彼此竖直间隔开的相应一组至少两个漏极选择层级导电条带内的每个漏极选择层级导电条带上形成穿过所述后向阶梯式介电材料部分的漏极选择层级接触通孔结构。

3、根据本公开的实施方案,一种三维存储器器件包括:绝缘层和导电层的交替堆叠,其中所述导电层包括字线层级导电层和位于所述字线层级导电层上方的漏极选择层级导电层;第一背侧沟槽填充结构,所述第一背侧沟槽填充结构沿第一水平方向延伸并且包括接触所述交替堆叠内的每个层的第一侧壁的第一介电表面;第二背侧沟槽填充结构,所述第二背侧沟槽填充结构沿所述第一水平方向延伸、沿垂直于所述第一水平方向的第二水平方向与所述第一背侧沟槽填充结构分离并且包括接触所述交替堆叠内的每个层的第二侧壁的第二介电表面;漏极选择层级隔离结构,所述漏极选择层级隔离结构延伸穿过交替堆叠的所述漏极选择层级导电层但不穿过所述字线层级导电层,其中所述漏极选择层级隔离结构沿所述第一水平方向延伸并且沿所述第二水平方向间隔开;存储器开口填充结构,所述存储器开口填充结构在其中存在所述交替堆叠内的每个层的存储器阵列区域中竖直延伸穿过所述交替堆叠,其中所述存储器开口填充结构中的每个存储器开口填充结构包括竖直半导体沟道和存储器膜;和导电间隔物,所述导电间隔物竖直延伸并将所述漏极选择层级导电层中的第一漏极选择层级导电层电连接到所述漏极选择层级导电层中的第二漏极选择层级导电层,其中所述导电间隔物沿所述第二水平方向延伸并且沿所述第二水平方向接触所述第一漏极选择层级导电层和所述第二漏极选择层级导电层的端部。

4、根据本公开的另一方面,一种形成存储器器件的方法包括:在衬底上方形成绝缘层和牺牲材料层的竖直交替序列;通过图案化所述竖直交替序列在所述竖直交替序列的较高层级处形成至少一个多层级竖直阶梯,其中所述至少一个多层级竖直阶梯中的每个多层级竖直阶梯包括所述竖直交替序列内的两个或更多个绝缘层和两个或更多个牺牲材料层的竖直重合侧壁;在所述至少一个多层级竖直阶梯中的每个多层级竖直阶梯上形成至少一个牺牲间隔物;通过图案化所述竖直交替序列在所述竖直交替序列的位于所述较高层级下方的较低层级处形成单层级竖直阶梯;形成竖直延伸穿过所述竖直交替序列的存储器开口;在所述存储器开口中形成存储器开口填充结构,其中所述存储器开口填充结构中的每个存储器开口填充结构包括相应竖直半导体沟道和相应存储器膜;以及分别用导电层和至少一个导电间隔物替换所述牺牲材料层和所述至少一个牺牲间隔物。

技术特征:

1.一种三维存储器器件,所述三维存储器器件包括:

2.根据权利要求1所述的三维存储器器件,其中:

3.根据权利要求1所述的三维存储器器件,所述三维存储器器件还包括:

4.根据权利要求3所述的三维存储器器件,其中:

5.根据权利要求4所述的三维存储器器件,其中:

6.根据权利要求5所述的三维存储器器件,其中:

7.根据权利要求6所述的三维存储器器件,其中所述第一侧壁区段包括:

8.根据权利要求7所述的三维存储器器件,所述三维存储器器件还包括接触层级介电层,所述接触层级介电层覆盖在所述交替堆叠上面并且具有在包括所述后向阶梯式介电材料部分的顶表面的水平平面内的顶表面,

9.根据权利要求4所述的三维存储器器件,其中漏极选择层级导电条带中的至少一些漏极选择层级导电条带的端部侧壁包括相对于所述第一水平方向以大于0但小于90度的角度延伸的之字形侧壁。

10.根据权利要求4所述的三维存储器器件,其中漏极选择层级导电条带中的至少一些漏极选择层级导电条带的端部侧壁具有平行于所述第一水平方向延伸的部分。

11.根据权利要求4所述的三维存储器器件,其中所述漏极选择层级接触通孔结构中的至少一个漏极选择层级接触通孔结构接触所述漏极选择层级导电条带中的同一漏极选择层级导电条带的两个端部侧壁。

12.根据权利要求4所述的三维存储器器件,其中所述漏极选择层级接触通孔结构中的至少一个漏极选择层级接触通孔结构接触同一漏极选择层级导电条带的内圆柱形侧壁。

13.根据权利要求4所述的三维存储器器件,其中所述相应一组至少两个漏极选择层级导电条带包括:

14.根据权利要求1所述的三维存储器器件,所述三维存储器器件还包括竖直延伸穿过所述交替堆叠内的相应层子集的横向隔离接触结构,其中所述横向隔离接触结构中的每个横向隔离接触结构包括:

15.根据权利要求14所述的三维存储器器件,其中所述横向隔离接触结构位于在所述交替堆叠中不含漏极选择层级隔离结构或阶梯式表面的区域中,并且其中所述漏极选择层级导电层中的每个漏极选择层级导电层从所述第一背侧沟槽填充结构连续延伸到所述第二背侧沟槽填充结构。

16.一种形成存储器器件的方法,所述方法包括:

17.根据权利要求16所述的方法,其中:

18.根据权利要求17所述的方法,所述方法还包括通过使用所述上覆漏极选择层级导电条带和所述下伏漏极选择层级导电条带作为蚀刻停止结构而蚀刻穿过所述后向阶梯式介电材料部分和所述绝缘层中的位于所述下伏漏极选择层级导电条带与所述上覆漏极选择层级导电条带之间的一个绝缘层,来形成漏极选择层级接触通孔腔体,其中:

19.根据权利要求17所述的方法,其中所述相应一组至少两个漏极选择层级导电条带包括还包括位于所述上覆漏极选择层级导电条带与所述下伏漏极选择层级导电条带之间的至少一个中间漏极选择层级导电条带。

20.根据权利要求16所述的方法,所述方法还包括形成竖直延伸穿过所述交替堆叠内的相应层子集的横向隔离接触结构,其中所述横向隔离接触结构中的每个横向隔离接触结构包括:

21.一种三维存储器器件,所述三维存储器器件包括:

22.根据权利要求21所述的三维存储器器件,其中:

23.根据权利要求21所述的三维存储器器件,其中所述导电间隔物、所述第一漏极选择层级导电层和所述第二漏极选择层级导电层具有一体式构造,并且在所述导电间隔物、所述第一漏极选择层级导电层和所述第二漏极选择层级导电层之间没有任何界面。

24.根据权利要求21所述的三维存储器器件,其中:

25.根据权利要求24所述的三维存储器器件,其中:

26.根据权利要求21所述的三维存储器器件,其中:

27.根据权利要求21所述的三维存储器器件,其中所述导电间隔物包括:

28.根据权利要求27所述的三维存储器器件,其中所述导电间隔物在所述直外侧壁区段与所述直内侧壁区段之间具有均匀的横向厚度,并且在所述锥形上外侧壁区段与所述直内侧壁区段之间具有随着距衬底的竖直厚度而减小的可变横向厚度。

29.根据权利要求21所述的三维存储器器件,所述三维存储器器件还包括:

30.根据权利要求29所述的三维存储器器件,其中所述后向阶梯式介电材料部分与所述交替堆叠的所述绝缘层中的在所述第一漏极选择层级导电层和所述第二漏极选择层级导电层下面的每个绝缘层的侧壁接触。

31.根据权利要求29所述的三维存储器器件,所述三维存储器器件还包括:

32.根据权利要求29所述的三维存储器器件,其中所述后向阶梯式介电材料部分接触所述第一介电表面和所述第二介电表面中的一个介电表面,并且与所述第一介电表面和所述第二介电表面中的另一个介电表面横向间隔开。

33.根据权利要求21所述的三维存储器器件,所述三维存储器器件还包括:

34.一种形成存储器器件的方法,所述方法包括:

35.根据权利要求34所述的方法,其中形成所述至少一个牺牲间隔物包括:

36.根据权利要求35所述的方法,其中:

37.根据权利要求34所述的方法,所述方法还包括:

38.根据权利要求37所述的方法,其中:

39.根据权利要求37所述的方法,其中:

40.根据权利要求39所述的方法,其中所述导电间隔物、所述第一漏极选择层级导电层和所述第二漏极选择层级导电层形成为在所述导电间隔物、所述第一漏极选择层级导电层和所述第二漏极选择层级导电层之间没有任何界面的单个连续结构。

技术总结

一种三维存储器器件包括:绝缘层和导电层的交替堆叠,其中该导电层包括字线层级导电层和位于该字线层级导电层上方的漏极选择层级导电层;竖直延伸穿过该交替堆叠的存储器开口填充结构;以及漏极选择层级接触通孔结构。该漏极选择层级接触结构中的第一漏极选择层级接触结构直接接触该漏极选择层级导电层中的彼此竖直间隔开的至少前两个漏极选择层级导电层。该漏极选择层级接触结构中的第二漏极选择层级接触结构直接接触该漏极选择层级导电层中的至少接下来两个漏极选择层级导电层,该接下来两个漏极选择层级导电层彼此竖直间隔开并且位于该漏极选择层级导电层中的至少该前两个漏极选择层级导电层下方。

技术研发人员:飞冈晃洋,清水悟,崔志欣

受保护的技术使用者:桑迪士克科技有限责任公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!