基准缓冲器的制作方法

背景技术:

1、逐次逼近寄存器(sar)模数转换器(adc)在多通道数据采集系统中很常见,诸如超声和其他医学成像系统、制造检查和质量控制系统以及温度和应力感测系统等。在sar adc中,由缓冲器输出的基准电压被用于在保持(hold)或转换(convert)阶段期间对电容器充电,这可能导致基准电压骤降而不是维持恒定值。一些基准缓冲器包括误差放大器和电容器,以帮助校正基准电压的骤降并帮助以期望的准确度维持电平或dc基准电压。然而,误差放大器和电容器占据集成电路的大面积并消耗大量的功率。此外,误差放大器基于包括瞬态骤降的基准电压的时间平均值来调整基准电压的电平或dc值。因为瞬态骤降包含信号和谐波含量,误差放大器基于基准电压的时间平均值对基准电压的电平或dc值的调整可能将基本误差和谐波误差引入到adc输出中。

技术实现思路

1、一种反馈回路包括比较器、数模转换器(dac)和开关电容器累加器。该比较器具有用于基准电压输入的第一输入、用于反馈输入的第二输入和用于控制信号的第三输入。该dac被耦合到比较器的输出,并且该开关电容器累加器被耦合到dac的输出。在一些实施方式中,数字滤波器被耦合在比较器的输出与dac的输入之间。在一些示例中,该反馈回路被耦合到缓冲器,该缓冲器被配置为输出反馈输入和用于模数转换器(adc)的基准电压。

2、在一些示例中,多个反馈回路共享公共比较器。第一反馈回路接收第二控制信号,并且第二反馈回路接收第三控制信号。缓冲器被耦合到第一反馈回路的输出。选择器逻辑电路接收基准电压输入和缓冲器的输出,并输出反馈输入。选择器逻辑电路的控制输入接收第二控制信号。第二反馈回路输出用于比较器的偏移校正信号。

3、在多个反馈回路共享公共比较器的一些实施方式中,第一反馈回路接收第一时钟信号,并且第二反馈回路接收第二时钟信号。耦合到第一反馈回路的输出的第一缓冲器输出第一基准电压输出,并且耦合到第二反馈回路的输出的第二缓冲器输出第二基准电压输出。选择器逻辑电路接收第一基准电压输出和第二基准电压输出并输出反馈输入。选择器逻辑电路的控制输入接收第一时钟信号。

技术特征:

1.一种基准电压发生器,其包括:

2.根据权利要求1所述的基准电压发生器,其中所述控制信号输入是时钟输入。

3.根据权利要求1所述的基准电压发生器,其中所述开关电容器累加器包括:

4.根据权利要求1所述的基准电压发生器,其进一步包括数字滤波器,所述数字滤波器被耦合在所述比较器的所述输出与所述一位dac的所述输入之间。

5.根据权利要求1所述的基准电压发生器,其中所述控制信号是第一控制信号,并且其中所述一位dac包括:

6.根据权利要求1所述的基准电压发生器,其中所述控制信号是第一控制信号,并且其中所述一位dac包括:

7.根据权利要求1所述的基准电压发生器,其中所述基准电压发生器被耦合到缓冲器,其中所述缓冲器具有用于模数转换器的基准电压输出和所述反馈输入。

8.一种设备,其包括:

9.根据权利要求8所述的设备,其中所述选择器逻辑电路被配置为输出所述基准电压输入,并且所述第二反馈回路被配置为在所述第二控制信号为逻辑高并且所述第三控制信号为逻辑低时输出所述偏移校正信号。

10.根据权利要求8所述的设备,其中所述第一反馈回路和所述第二反馈回路中的每个包括:

11.根据权利要求10所述的设备,其中所述第一反馈回路和所述第二反馈回路中的至少一个进一步包括耦合在所述比较器的所述输出和所述一位dac的输入之间的数字滤波器。

12.根据权利要求10所述的设备,其中所述一位dac包括:

13.根据权利要求10所述的设备,其中所述一位dac包括:

14.根据权利要求10所述的设备,其中所述开关电容器累加器包括:

15.根据权利要求8所述的设备,其中模数转换器即adc包括所述设备,并且其中所述设备的输出被配置为向所述adc提供基准电压。

16.根据权利要求15所述的设备,其中所述adc是逐次逼近寄存器adc,并且其中所述设备的所述输出被配置为对所述adc中的至少一个电容器充电。

17.一种基准电压发生器,其包括:

18.根据权利要求17所述的基准电压发生器,其中所述第一反馈回路和所述第一缓冲器包括粗略基准电压发生器,其中所述第二反馈回路和所述第二缓冲器包括精细基准电压发生器。

19.根据权利要求17所述的基准电压发生器,其进一步包括:

20.根据权利要求19所述的基准电压发生器,其中所述n个唯一时钟信号的频率是1除以n。

21.根据权利要求17所述的基准电压发生器,其中所述第一时钟信号和所述第二时钟信号相对于彼此反相。

22.根据权利要求17所述的基准电压发生器,其中所述第一时钟信号和所述第二时钟信号的频率大约等于所述控制信号的频率的一半。

23.根据权利要求17所述的基准电压发生器,其中所述第一反馈回路和所述第二反馈回路中的每个包括:

24.根据权利要求23所述的基准电压发生器,其中所述第一反馈回路和所述第二反馈回路中的至少一个进一步包括耦合在所述比较器的所述输出与所述一位dac的输入之间的数字滤波器。

技术总结

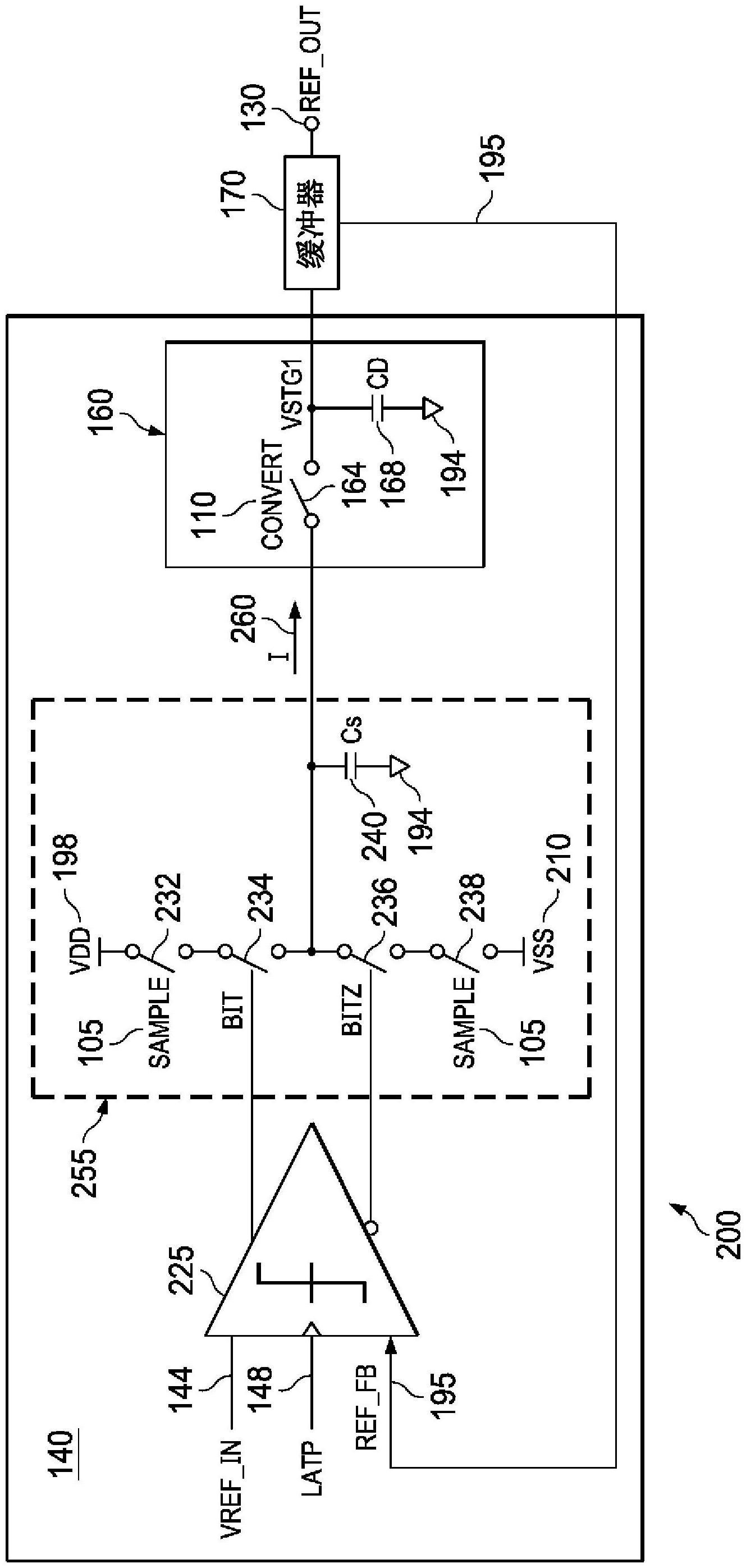

基准电压发生器(200)包括比较器(225)、数模转换器(DAC)(255)和开关电容器累加器(160)。该比较器接收基准电压输入(144)、反馈输入(195)和控制信号(148)。该DAC被耦合到比较器的输出,并且该开关电容器累加器被耦合到DAC的输出。在一些实施方式中,数字滤波器被耦合在比较器的输出和DAC的输入之间。该开关电容器累加器可以被耦合到缓冲器(170),该缓冲器输出反馈输入和用于模数转换器(ADC)的基准电压(130)。在一些实施方式中,反馈回路包括N个开关电容器累加器和耦合到比较器的输出的N个一位DAC,这些开关电容器累加器中的每个都耦合到唯一的一位DAC。

技术研发人员:S·保罗,R·N·斯里尼瓦撒,S·B·塞沙德里,S·杜塔

受保护的技术使用者:德克萨斯仪器股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!